# A 1.5-V 900-Mhz Monolithic CMOS Fast-Switching Frequency Synthesizer for Wireless Applications

A thesis submitted to The Hong Kong University of Science and Technology in partial fulfillment of the requirements of The Degree of Master of Philosophy in Electrical and Electronic Engineering

By

### Lo Chi Wa

Department of Electrical and Electronic Engineering Bachelor of Engineering in Electronic Engineering (1997) The Hong Kong University of Science and Technology

January, 2000

## A 1.5-V 900-Mhz Monolithic CMOS Fast-Switching Frequency Synthesizer for Wireless Applications

by

## Lo Chi Wa

Approved by:

**Dr. Howard Cam LUONG** Thesis Supervisor

**Dr. Bertram Emil Shi** Thesis Examination Committee Member (Chairman)

**Dr. Philip Mok Kwok Tai** Thesis Examination Committee Member

**Prof. Philip Ching-Ho Chan** Head of Department of Electrical and Electronic Engineering

> Department of Electrical and Electronic Engineering The Hong Kong University of Science and Technology

> > January, 2000

## A 1.5-V 900-Mhz Monolithic CMOS Fast-Switching Frequency Synthesizer for Wireless Applications

by

### Lo Chi Wa

For the degree of Master of Philosophy in Electrical and Electronic Engineering at the Hong Kong University of Science and Technology in January, 2000

### ABSTRACT

In modern transceiver designs, a frequency synthesizer with good phase-noise performance is very important because it affects the efficiency of valuable air channel usage and sensitivity of small signals under the presence of large interference. Fast frequency switching is also required in many TDMA systems and frequency-hopping spread-spectrum systems. Other than these, low supply voltage, low power consumption and monolithic design are three important features of any modern analog circuits.

However, the above requirements are difficult to be achieved in traditional frequency synthesizer designs. To solve these problems, a new design of phase-locked loop frequency synthesizer is proposed. Instead of voltage or current domain, some signals in the phase-locked loop are manipulated in capacitance domain. A binary-weighted switchable-capacitor array is used to replace the digital-to-analog converter while two varactors connected in parallel replace the voltage adder. This design provides many advantages, including simplified analog circuitry, low supply voltage, low power consumption, small chip area, fast frequency switching and high immunity of substrate noise.

A prototype of a 1.5-V 900-Mhz monolithic CMOS fast-switching frequency synthesizer based on GSM specifications is designed and fabricated to demonstrate the idea. It consumes 30mW. The total chip area is  $0.9 \times 1.1 \text{ mm}^2$ . The settling time is within 150us and phase noise is –118dBc/Hz at 600kHz offset. The ability of direct-digital modulation is also provided with the sigma-delta fractional-N architecture.

## Acknowledgments

I am grateful to Dr. Howard Cam Luong, my research supervisor. He really takes very good care of me and my everything in this few years in HKUST.

I would also like to thank my friends: Vincent Cheung, Toby Kan, Issac Hsu, Thomas Choi, David Leung, Guo Chun Bing, William Yan, Pang Ho Yin, Bunny Mak, Cai Yue Ming, Alan Chan, Wallace Wong, Lau Kwok Kit, Bob Wong, and Ronny Hui. They share with me their knowledge, books, comics, magazines, stationery, food, drink and so-called jokes.

I also thank to Fred Kwok, Jack Chan, Luk Siu Fai and Joe Lai. They are really the best technical support team.

I would also like to express my gratitude to Dr Bertram E. Shi and Dr Philip Mok for being my thesis examination committee members and tolerating my late thesis.

Finally, I would like to thank my family for their patience in these twenty-four years.

# **Table of Contents**

| i                                                                                                                                                                    | Page                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Acknowledgments                                                                                                                                                      | i                          |

| Table of Contents                                                                                                                                                    | ii                         |

| List of Tables                                                                                                                                                       | V                          |

| List of Figures                                                                                                                                                      | vi                         |

| Chapter 1 Introduction                                                                                                                                               | 1                          |

| Background<br>Challenges<br>Noise<br>Switching speed<br>Supply voltage<br>Monolithic<br>Thesis overview                                                              | 2<br>3<br>4<br>4<br>4      |

| Chapter 2 Specifications                                                                                                                                             | 6                          |

| Frequency range and resolution<br>Phase noise<br>Spurs<br>Frequency switching time<br>Loop bandwidth<br>Summary of specifications                                    |                            |

| Chapter 3 System Design                                                                                                                                              | 19                         |

| Phase-locked loop synthesizer<br>Existing architecture<br>Proposed architecture<br>Advantages<br>Faster switching speed<br>Lower supply voltage<br>Smaller chip area | 20<br>21<br>22<br>23<br>23 |

| Low phase noise<br>Fractional-N synthesizer<br>Design criteria<br>Quantization noise                                                                                 | 24<br>24<br>26             |

| System parameters                                                                                                                                                    |                            |

| Chapter 4 Circuit Implementation                                                                                                                                     | 32                         |

| Voltage-controlled oscillator<br>Quaduature LC oscillators                                                                                                           |                            |

| Switchable-capacitor-array                                                   | 33  |

|------------------------------------------------------------------------------|-----|

| Varactor                                                                     |     |

| Inductor                                                                     |     |

| Phase noise performance                                                      | 39  |

| Novel idea of zero excess noise factor                                       | 45  |

| Loop filter                                                                  |     |

| Dual-path filter                                                             |     |

| Dual-path filter based on capacitance domain operation                       |     |

| Implementation                                                               |     |

| Charge pump                                                                  | 53  |

| Frequency-phase detector                                                     |     |

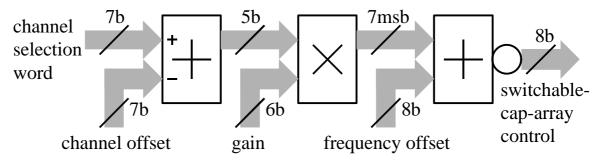

| Gain and offset adjustment for the switchable-capacitor-array                | 56  |

| Specification                                                                | 56  |

| Circuits                                                                     | 57  |

| Prescalar                                                                    | 58  |

| Architecture                                                                 | 58  |

| High-speed multi-modulus divider                                             | 59  |

| Phase select circuit                                                         | 61  |

| Low-speed dual-modulus dividers                                              | 62  |

| Low speed divide-by-2 divider                                                | 63  |

| Control logic                                                                | 64  |

| Sigma-Delta Modulator                                                        | 65  |

| Architecture                                                                 | 65  |

| MESH-3 Sigma-Delta modulator                                                 |     |

| Dither generator                                                             | 71  |

| Chapter 5 Quadrature phase and amplitude matchings in coupled-LC oscillators | 74  |

| Introduction                                                                 | 74  |

| Operational principles                                                       |     |

| Amplitude control                                                            |     |

| Quadrature phase control                                                     |     |

| Matched output amplitudes                                                    | 82  |

| Current interaction                                                          | 83  |

| Design considerations                                                        | 84  |

| Layout considerations                                                        |     |

| Simulation results                                                           | 88  |

| Limitations                                                                  | 89  |

| Chapter 6 Layout Considerations                                              | 90  |

| Switchable-capacitor array layout                                            | 90  |

| Varactor layout                                                              |     |

| Inductor layout                                                              |     |

| Voltage-controlled oscillator layout                                         |     |

| Synthesizer Layout                                                           |     |

| Die Layout                                                                   |     |

| Chapter 7 Measurement                                                        |     |

| Introduction                                                                 | 102 |

| Passive components                                                           |     |

| Testing setup                                           |     |

|---------------------------------------------------------|-----|

| Inductor                                                |     |

| Varactor                                                |     |

| Switchable-capacitor array                              |     |

| Voltage-controlled oscillator and frequency synthesizer |     |

| Testing setup                                           |     |

| Frequency tuning by switchable-capacitor array          |     |

| Frequency tuning by varactor                            |     |

| Amplitude and phase matchings                           |     |

| Frequency synthesizer calibration and operation         |     |

| Phase noise                                             |     |

| Spurs                                                   |     |

| Frequency switching                                     |     |

| Digital modulation                                      |     |

| Summary of performance                                  |     |

| Comparison of performance                               |     |

| Chapter 8 Conclusion                                    |     |

| Bibliography                                            | 141 |

# **List of Tables**

| Pa                                                                            | ge  |

|-------------------------------------------------------------------------------|-----|

| Table 1 Summary of specifications                                             | 18  |

| Table 2 Summary of filter parameters                                          | 51  |

| Table 3 Summary of input and output ranges of high-order loop and cascade-typ | be  |

| modulators                                                                    | 66  |

| Table 4 Summary of parameters of inductor                                     | 108 |

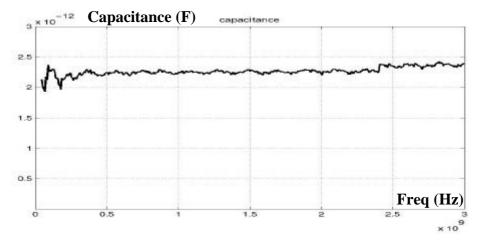

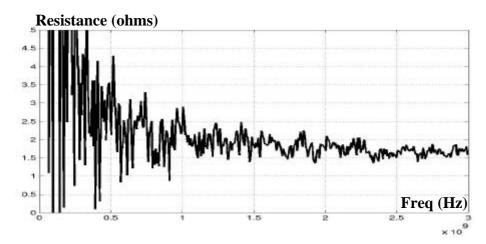

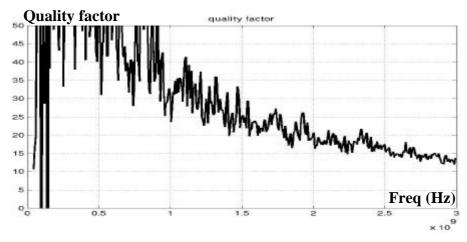

| Table 5 Summary of parameters of varactor (132 diodes)                        | 111 |

| Table 6 Summary of N-well substrate parasites                                 | 113 |

| Table 7 Summary of parameters of switchable-capacitor array                   | 117 |

| Table 8 Summary of performances of VCO                                        | 135 |

| Table 9 Summary of performances of frequency synthesizer                      | 136 |

| Table 10 Comparison of performances                                           | 137 |

# List of Figures

| Pag                                                                                            | ze   |

|------------------------------------------------------------------------------------------------|------|

| Fig. 1 Block diagram of a receiver                                                             |      |

| Fig. 2 Frequency domain representation of the down-conversion and the relationship             | -    |

| between RF, image, LO, and IF signals                                                          |      |

| Fig. 3 Frequency domain representation of the channel selection                                |      |

| Fig. 4 Profile of interference signals                                                         |      |

| Fig. 5 Frequency domain representation of phase noise                                          | 10   |

| Fig. 6 Effect of phase noise of LO signal                                                      |      |

| Fig. 7 Phase noise envelope for local oscillator signal in GSM receiver                        | 12   |

| Fig. 8 Frequency domain representation of spurs                                                | 13   |

| Fig. 9 Effect of spurs of LO signal                                                            | 13   |

| Fig. 10 Spur envelope for local oscillator signal in GSM receiver                              | 15   |

| Fig. 11 GSM Receive and transmit time slots                                                    |      |

| Fig. 12 Frequency selective fading and narrowband interference                                 | 17   |

| Fig. 13 System diagram of the proposed transceiver                                             | 18   |

| Fig. 14 Block diagram of phase-locked loop frequency synthesizer                               | 20   |

| Fig. 15 The evolution of fast-switching PLL frequency synthesizer - a) two possibl             | e    |

| configurations employing DAC to increase frequency switching speed; b                          | )    |

| employing switchable-capacitor-array to increase frequency switching speed                     | 22   |

| Fig. 16 Block diagrams of some dual-loop synthesizer designs                                   | 25   |

| Fig. 17 Quantization noise in frequency domain                                                 | 27   |

| Fig. 18 Quantization noise in a sigma-delta Fractional-N synthesizer                           | 27   |

| Fig. 19 Maximal loop bandwidths and minimal reference frequencies for second, third            | l,   |

| fourth-order sigma-deltra modulators for phase noise requirement of                            | _    |

| 121dBc/Hz @ 600kHz offset                                                                      | 29   |

| Fig. 20 Detailed system diagram of this design                                                 | 30   |

| Fig. 21 The schematic diagram of the voltage-controlled oscillator with switchable             |      |

| capacitor-array                                                                                | 32   |

| Fig. 22 Another view of coupled LC oscillators                                                 | 33   |

| Fig. 23 Tuning curve of the oscillator by switchable-capacitor-array                           | 35   |

| Fig. 24 Models of an unit switchable-capacitar (A) general case (B) turn-on (C) turn-off       | f.37 |

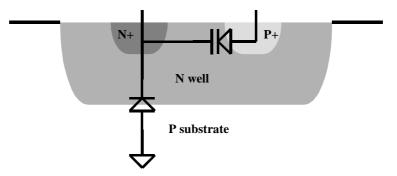

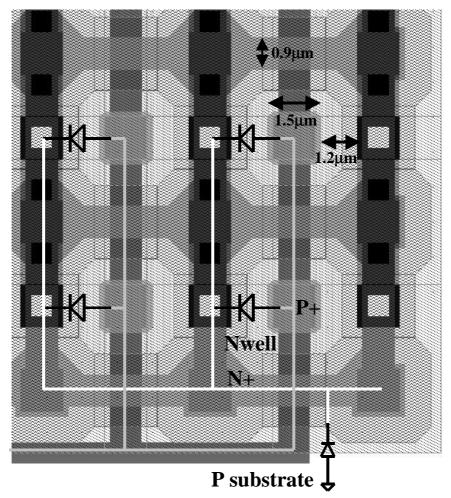

| Fig. 25 Cross section of the parasitic PN junction varactor                                    | 38   |

| Fig. 26 Model of a simple LC oscillator                                                        | 40   |

| Fig. 27 Graphical representations of the generalized criterion for oscillation a) based or     | n    |

| loop gain b) based on negative conductance                                                     | 41   |

| Fig. 28 Schematic diagram of an LC oscillator                                                  | 42   |

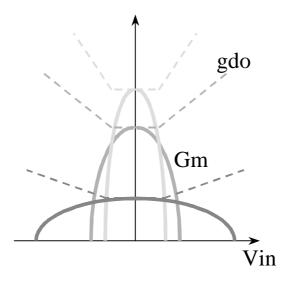

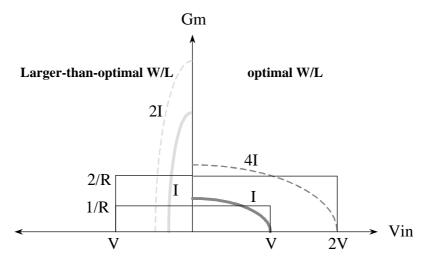

| Fig. 29 gdo for different negative conductances                                                |      |

| Fig. 30 Transconductance vs input voltage of transistors of different W/L ratios               | 44   |

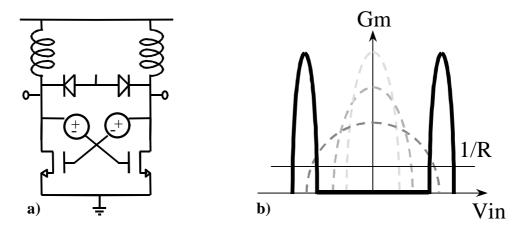

| Fig. 31 a) Proposed LC oscillator and b) the corresponding Gm                                  | 46   |

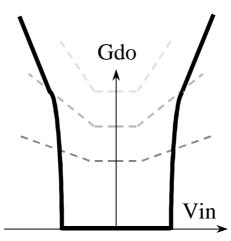

| Fig. 32 Gdo of the proposed LC oscillator                                                      | 47   |

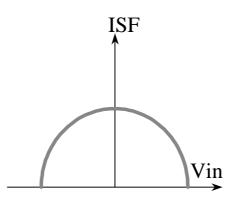

| Fig. 33 Impulse sensitivity function                                                           | 47   |

| Fig. 34 Phase contribution of the proposed oscillator                                          | 47   |

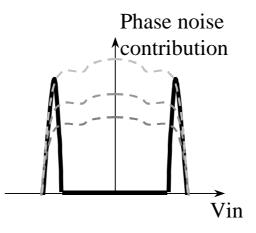

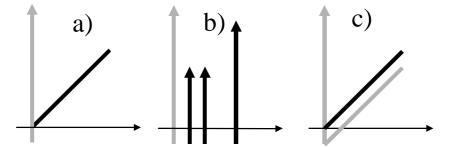

| Fig. 35 Evolution of the loop filter $-a$ ) simple active filter b) dual-path filter by adding | g    |

| the outputs of the integrator and LPF with a voltage adder; c) dual-path filter by             | У    |

| adding the outputs in capacitance domain                                                       | 49   |

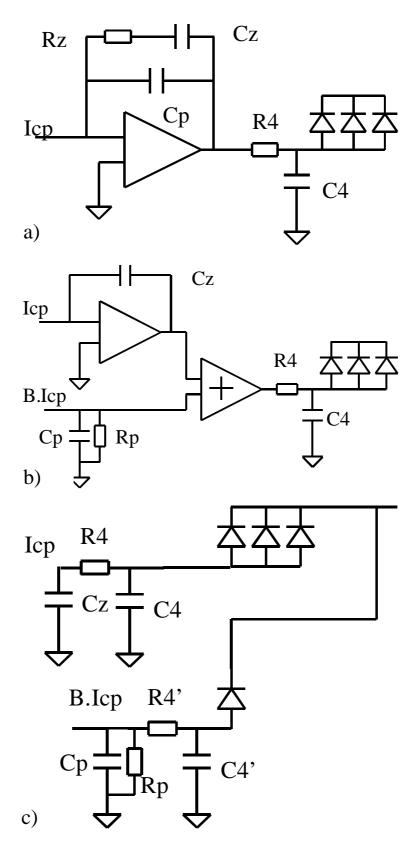

| Fig. 36 Dual-path loop filter principle                                                   | 50 |

|-------------------------------------------------------------------------------------------|----|

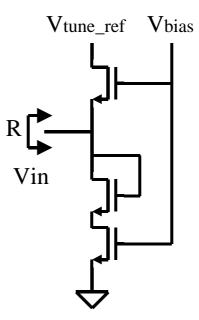

| Fig. 37 Schematic of the largest resistor implemented by NMOS transistors                 | 52 |

| Fig. 38 Resistance of NMOS resistor vs. input voltage                                     |    |

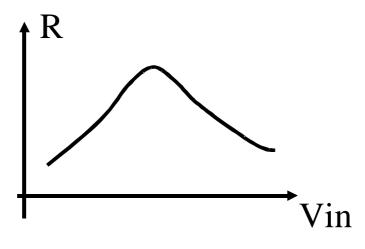

| Fig. 39 Schematic of current steering charge-pump                                         | 54 |

| Fig. 40 Schematic diagram of the current steering charge-pump (pump-down current          |    |

| branch only) and the switch capacitor driving stage                                       |    |

| Fig. 41 Schematic of frequency phase detector                                             |    |

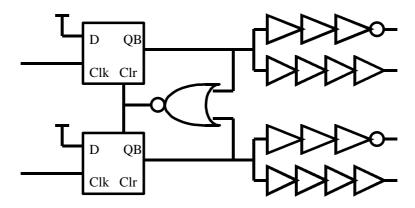

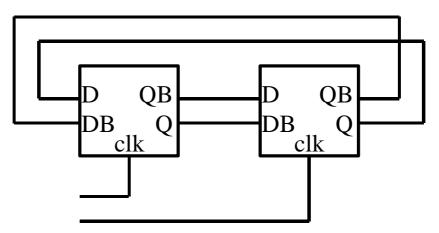

| Fig. 42 Schematic of simplified TSPL D F/F                                                |    |

| Fig. 43 Tuning curve by switchable-capacitor-array with gain adjustment of finit          |    |

| resolution                                                                                |    |

| Fig. 44 gain and offset adjustments for the switchable-capacitor-array control            |    |

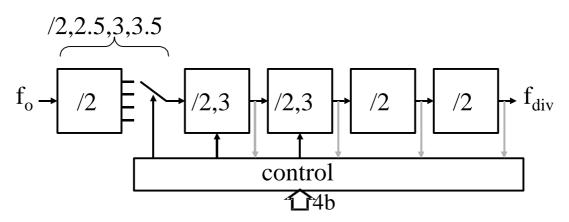

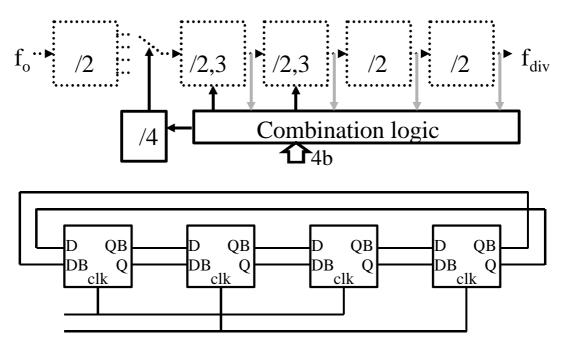

| Fig. 45 System diagram of the multi-modulus prescalar                                     |    |

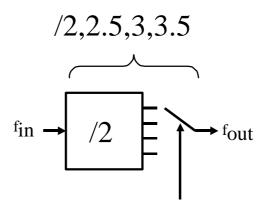

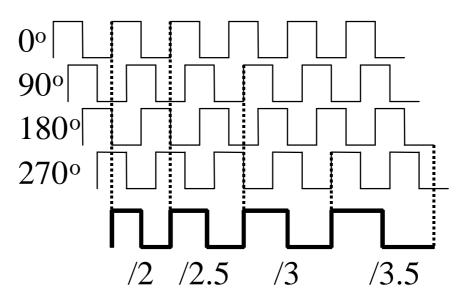

| Fig. 46 Schematic of high speed divide-by-2,2.5,3,3.5 multi-modulus divider               |    |

| Fig. 47 Timing diagram of the high-speed divide-by-2,2.5,3,3.5 multi-modulus divider      |    |

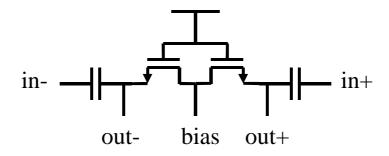

| Fig. 48 AC couple and biasing for the input of the prescalar                              |    |

| Fig. 49 Schematic diagram of the high speed divide-by-2 divider                           |    |

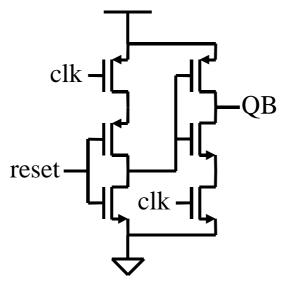

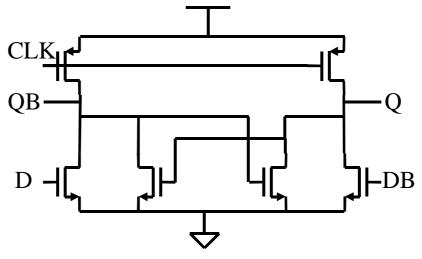

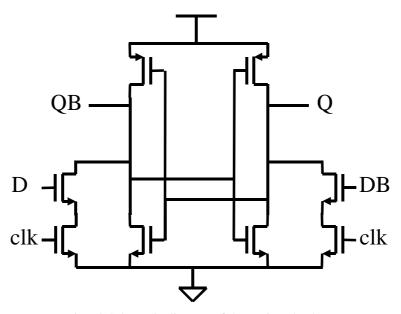

| Fig. 50 Schematic diagram of the high speed D latch                                       |    |

|                                                                                           |    |

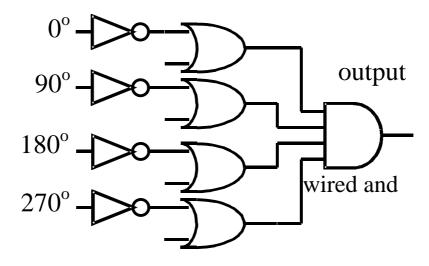

| Fig. 51 Schematic of the phase select circuit                                             |    |

| Fig. 52 Schematic of the pseudo-NMOS a) inverter, b) OR gate, c) wired-AND gate           |    |

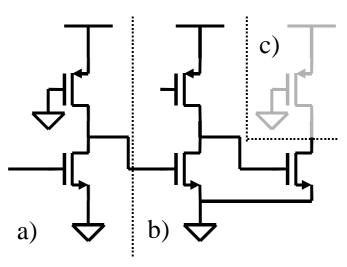

| Fig. 53 Schematic diagram of the dual-modulus divider                                     |    |

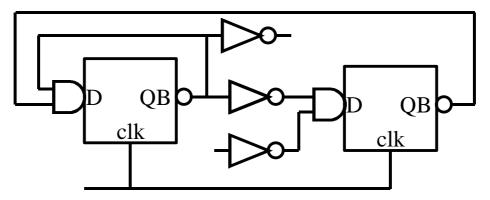

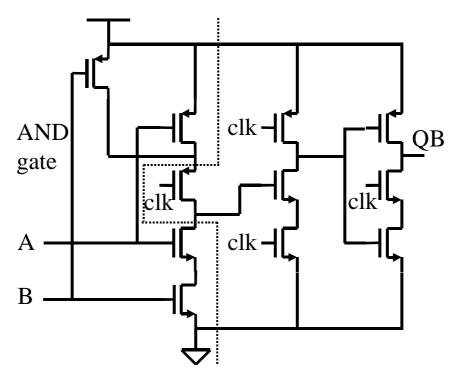

| Fig. 54 Schematic diagram of the TSP D F/F with AND gate embedded                         |    |

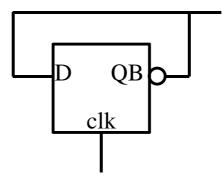

| Fig. 55 Schematic diagram of the low speed divide-by-two divider                          |    |

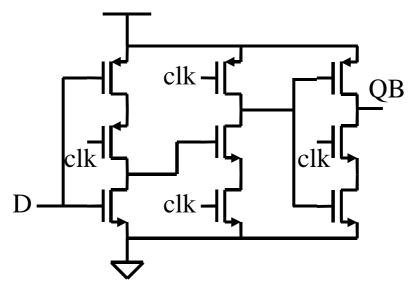

| Fig. 56 Schematic diagram of the TSP D F/F                                                |    |

| Fig. 57 Schematic diagram of the state machine of the phase select                        |    |

| Fig. 58 Schematic diagram of the static D latch                                           |    |

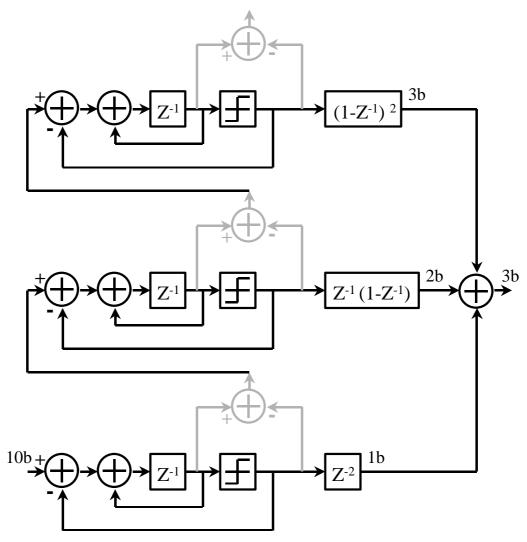

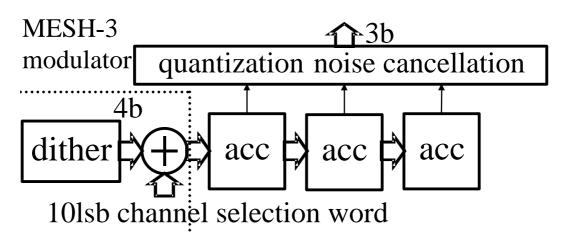

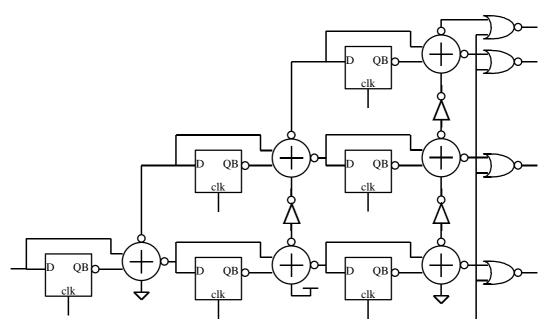

| Fig. 59 System diagram of MESH-3 Sigma-Delta modulator                                    |    |

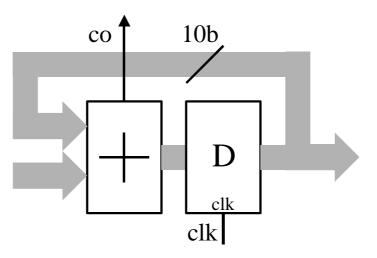

| Fig. 60 Schematic of the accumulator                                                      |    |

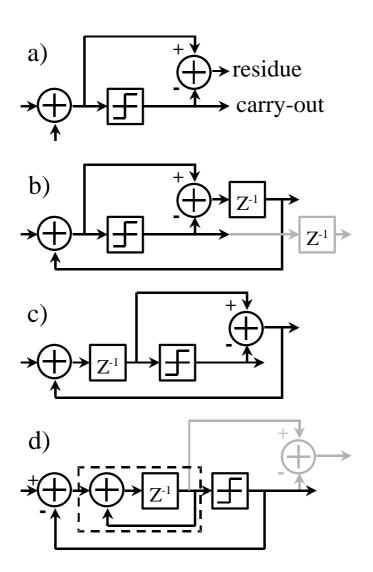

| Fig. 61 Evolution of the digital accumulator a) System diagram of a digital adder b-d     | ·  |

| Different views of system diagram of a digital accumulator                                | 69 |

| Fig. 62 Schematic of the 3-order digital Sigma-Delta modulator with a dither input        | 70 |

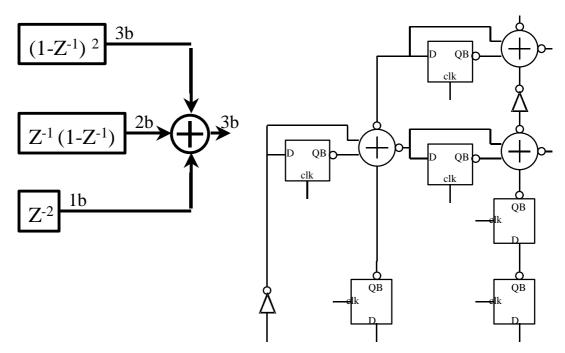

| Fig. 63 System and schematic diagrams of the quantization noise cancellation              | 71 |

| Fig. 64 Output of a first-order modulator with a half-range input                         | 72 |

| Fig. 65 Output spectrums of a sigma-delta modulator a) random input b) DC or periodi      | с  |

| input c) DC or periodic input with dither                                                 |    |

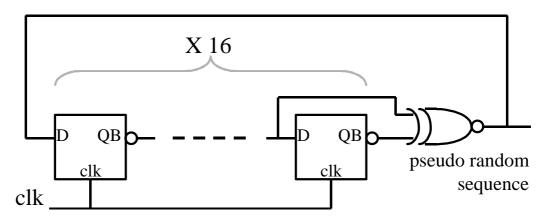

| Fig. 66 Schematic diagram of the pseudo random sequence generator                         | 73 |

| Fig. 67 Schematic diagram of the 3-order high pass digital filter                         |    |

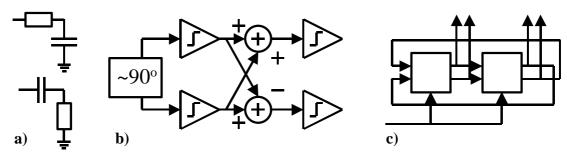

| Fig. 68 Different methods to generate quadrature outputs                                  |    |

| Fig. 69 Schematic of coupled LC oscillators with quadrature outputs                       |    |

| Fig. 70 (a) Schematic of LC oscillator; (b) Output-input characteristic of gm cell        |    |

| Fig. 71 (a) Less current flow in gm cell when small differential output; (b) More current |    |

| flow in gm cell when large differential output                                            |    |

| Fig. 72 (a) Single-ended output voltage of LC oscillator; (b) Common source voltage       |    |

| (c) Current flow into gm cell. (1) without capacitor (2) with capacitor                   |    |

|                                                                                           |    |

| Fig. 73 Current flows in two oscillators with 90-degree phase difference                  |    |

| Fig. 74 (a) Output voltage of LC oscillator; (b) Common source voltage; (c) Currer        |    |

| flow into gm cell. (1) without capacitor or common source node connection (2              |    |

| with capacitor (3) with connection                                                        |    |

| Fig. 75 Another view of a matched coupled-LC oscillators                                  | 81 |

| Fig. 76 Amplitudes    | s and currents of the two mistmatched oscillators : T1: period wh    | ien  |

|-----------------------|----------------------------------------------------------------------|------|

| differential          | output is large in oscillator A; T2: period when differential output | i is |

|                       | illator B                                                            |      |

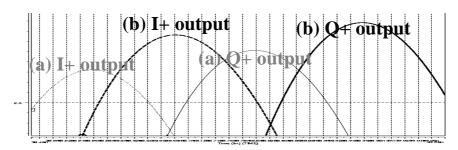

| Fig. 77 IQ outputs of | of coupled LC oscillators (a) without common source connection a     | nd   |

| (b) with cor          | nnection                                                             | 82   |

| Fig. 78 Circuit to ve | erify imperfect control of the phase for different IQ amplitudes     | 82   |

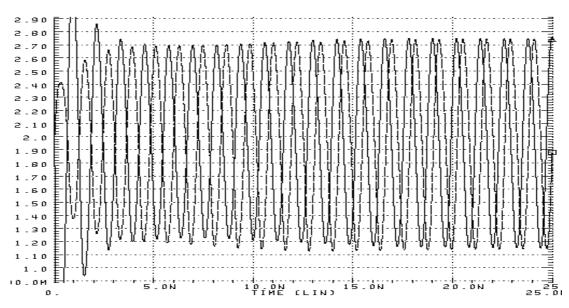

| Fig. 79 Output vol    | ltage waveform of two LC oscillators with common source no           | ode  |

| connection            | only                                                                 | 83   |

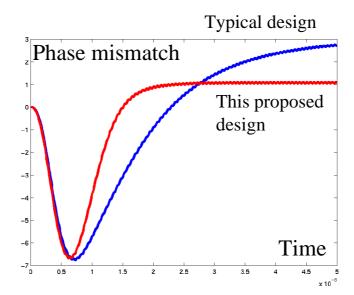

| Fig. 80 Phase erro    | or with time of coupled LC oscillators without common sour           | rce  |

|                       | and with connection                                                  |      |

| Fig. 81 Different vi  | ews of the coupled-LC oscillators                                    | 85   |

| Fig. 82 Floorplan o   | f the Gm cell transistors (matched pairs in dotted rectangles) and t | he   |

|                       | ng schematic                                                         |      |

| Fig. 83 a) Floorplan  | n of four inductors with rotational symmetry b) Floorplan of the tw  | WO   |

| pairs of indu         | uctors in the two oscillators with x-symmetry                        | 87   |

| Fig. 84 Layouts of    | oscillators a) four inductors with rotational symmetry b) two pairs  | of   |

| inductors in          | the two oscillators with x-symmetry                                  | 87   |

| Fig. 85 Other altern  | ative arrangement of inductors and the corresponding layout          | 88   |

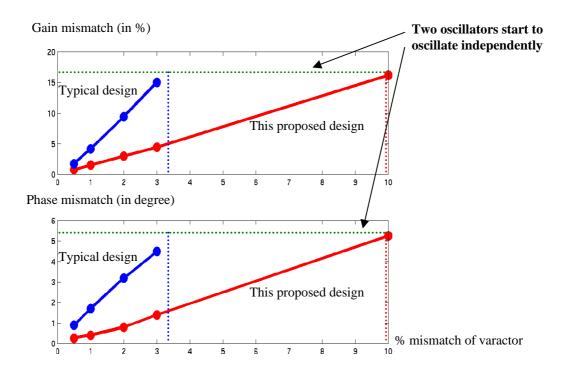

| Fig. 86 a) Amplitu    | de mismatch with mismatch error in varactors; b) phase mismat        | ich  |

| with misma            | tch error in varactors                                               | 89   |

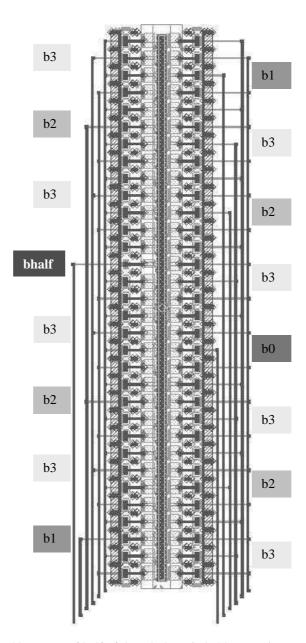

| Fig. 87 Layout of s   | witchable-capacitor-array                                            | 91   |

| Fig. 88 Layout of h   | alf of the whole switchable-capacitor array                          | 92   |

| Fig. 89 Layout of P   | P+ Nwell varactor                                                    | 93   |

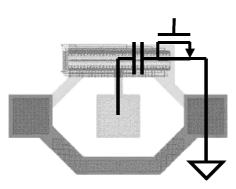

| Fig. 90 Layout of m   | netal-2 layer of the inductor                                        | 95   |

| Fig. 91 Layout of m   | netal-3 layer of the inductor                                        | 95   |

| Fig. 92 Layout of th  | ne inductor                                                          | 96   |

| Fig. 93 Zoomed vie    | ew of the interconnection of two layers of the inductor              | 96   |

|                       | ne voltage-controlled oscillator                                     |      |

|                       | of the voltage-controlled oscillator                                 |      |

|                       | he frequency synthesizer                                             |      |

|                       | am of the frequency synthesizer                                      |      |

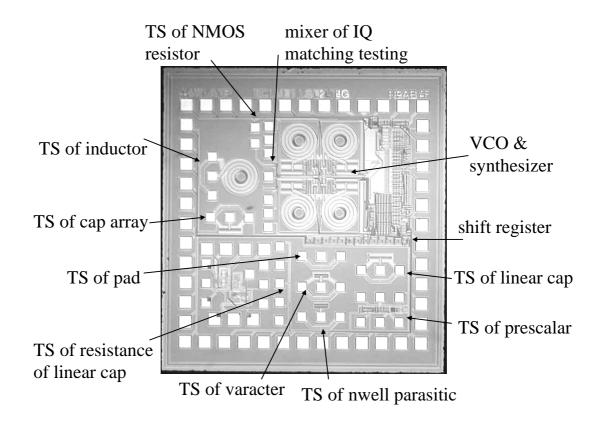

|                       | f the frequency synthesizer and the test structures                  |      |

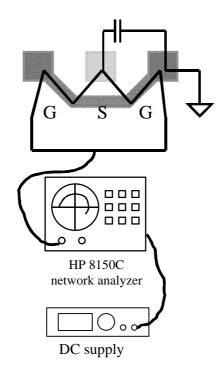

| Fig. 99 Testing setu  | p for the passive component measurement                              | 103  |

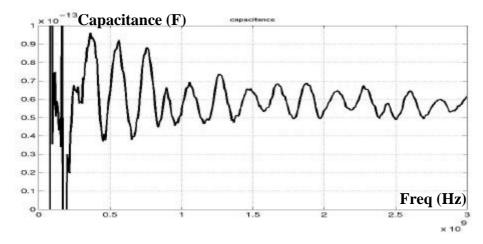

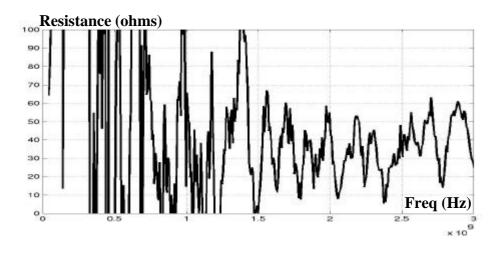

|                       | ce of the testing pads of the passive components vs. frequency       |      |

|                       | of the testing pads of the passive components vs. frequency          |      |

|                       | ctor of the testing pads of the passive components vs. frequency     |      |

|                       | ucture of the spiral inductor                                        |      |

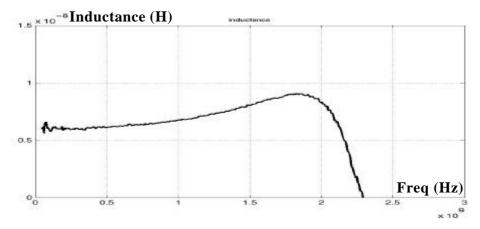

| -                     | e of the inductor vs. frequency                                      |      |

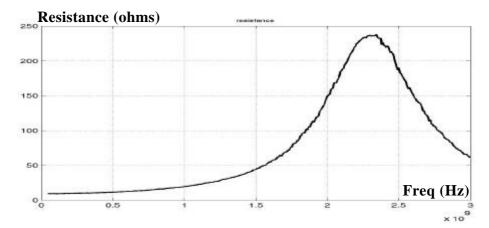

|                       | stance of the inductor vs. frequency                                 |      |

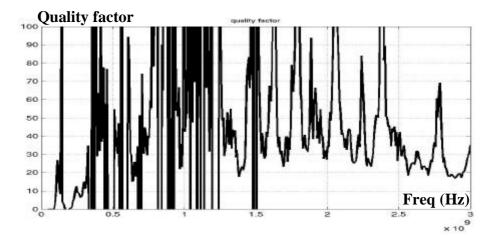

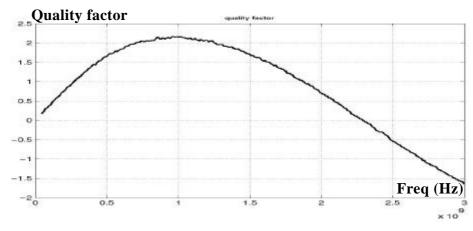

|                       | ctor of the inductor vs. frequency                                   |      |

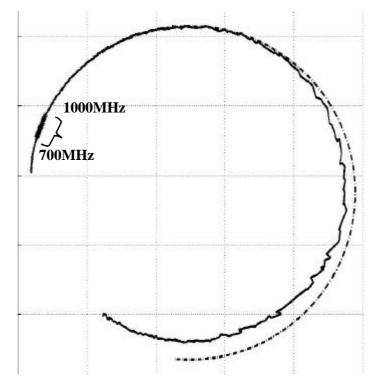

|                       | S-parameter of the inductor and the corresponding fitting curve      |      |

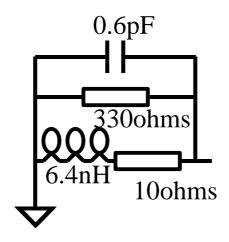

|                       | nd model of the spiral inductor                                      |      |

|                       | ucture of the varactor                                               |      |

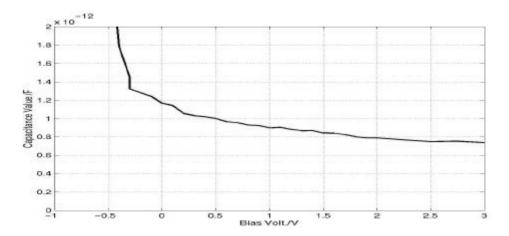

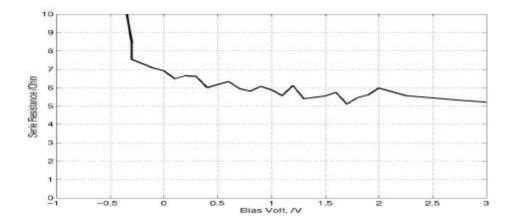

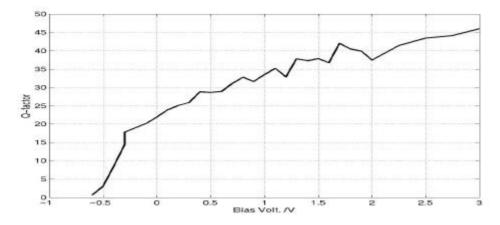

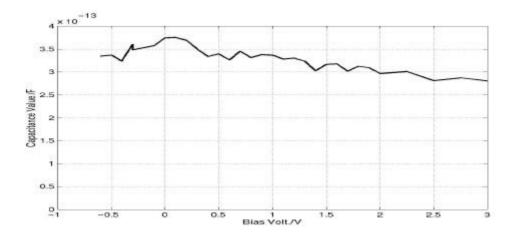

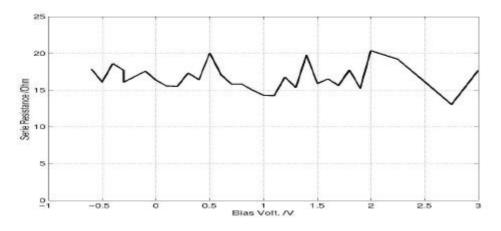

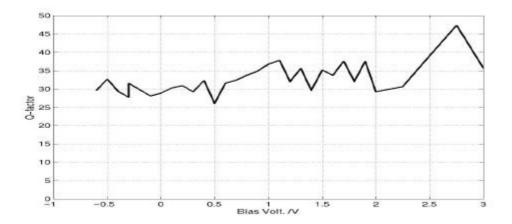

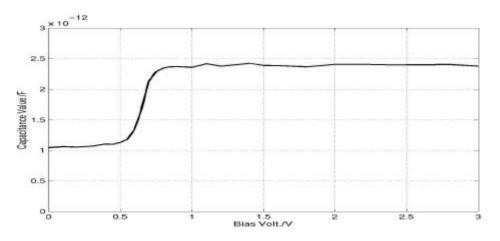

|                       | ce of the varactor vs. bias                                          |      |

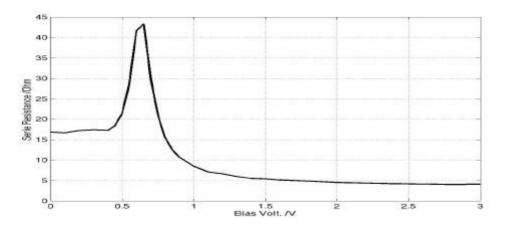

|                       | stance of the varactor vs. bias                                      |      |

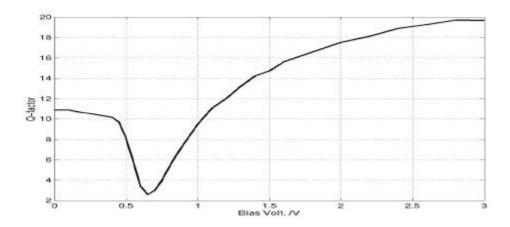

|                       | ctor of the varactor vs. bias                                        |      |

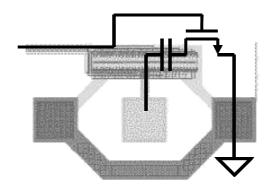

|                       | ucture of the N-well substrate parasitic diode                       |      |

|                       | ce of the N-well substrate parasitic diode vs. bias                  |      |

| Fig. 115 Series resi  | stance of the N-well substrate parasitic diode vs. bias              | 112  |

| 2  |

|----|

| 4  |

| 4  |

| 4  |

| 5  |

| 5  |

| 6  |

| 6  |

| 6  |

| 8  |

| 9  |

| 20 |

| 21 |

| 21 |

| 22 |

| 23 |

| 24 |

| 25 |

| 26 |

| 27 |

| 28 |

| 28 |

| 29 |

| 80 |

| 32 |

| 33 |

|    |

| 34 |

|    |

| 34 |

|    |

## **Chapter 1 Introduction**

### Background

Wireless communication is replacing the cable communication to become the most important part of the modern world. The most familiar wireless communication is the mobile phone. It links all people anywhere anytime. Starting from the bulky analog mobile phones to digital mobile phones, the size, the weight and the price become lower and lower while the performance becomes better and better.

Inside a mobile phone, there is basically a wireless transceiver. In the past, most of the transceivers were implemented by bulky and expensive discrete components. As the technologies are improved, some building blocks can be implemented by low-density integration technologies, e.g. BJT, GaAs, to reduce the cost and size of the transceivers. However, this is not enough to satisfy people's desire of low cost, small size and good performance. Due to the rapid development of the microprocessor and computer industries in the past years, the digital CMOS process becomes very mature. Compared to other available processes, the digital CMOS process has the strong advantages of low cost and high density. The growing density and performance of the sub-micro CMOS process make the process to be a very attractive candidate for the radio-frequency integrated circuits.

In this research, we are trying to demonstrate the possibility to implement wireless receiver and transmitter with the digital CMOS process. The first step is to implement a monolithic wireless receiver for the GSM system, which is the most popular in the world. All the building blocks of the wireless transceiver, including low-noise amplifier, RF image-rejection filter, mixer, frequency synthesizer, IF channel-selection filter and the IF analog-to-digital converter will be implemented on the same chip.

One of the major building blocks is the frequency synthesizer. The frequency synthesizer is to generate the LO frequency for the mixer to down-convert the RF signal to the IF filter. Unlike other building blocks in the receiver, the frequency synthesizer itself is already a small system including many building blocks. This makes the frequency synthesizer to be a very challenging project because the project involves system design, RF circuit design, high speed digital circuit design and low noise analog circuit design.

In this project, a monolithic frequency synthesizer is designed with a lot of efforts on both system and circuit implementation to solve the problems encountered with existing deigns.

## Challenges

In modern transceivers, a good frequency synthesizer to provide a pure local oscillator frequency is very important because of the valuable bandwidth available. Phase noise is the most basic requirement of performance for a frequency synthesizer. It affects the efficiency of air channel usage and sensitivity of small signal under the presence of large interference.

Fast switching between different frequencies is also important in TDMA and spread spectrum systems. Spread spectrum is especially important in modern wireless

applications because it can provide immunity to multipath interference and fading, and provide robust multiple access capability.

Other than phase noise and switching performance, low supply voltage, low power consumption and monolithic design are three essential features of any modern analog circuits. Low supply voltage, especially 1.5 volt from a single battery, is very important in portable applications. It allows the design to integrate with modern low-voltage digital circuits easily, reduce the weight and size of battery, and usually reduce the power consumption. Monolithic design is also important because it has lower manufacturing cost, smaller size and lower power consumption.

Most of the common frequency synthesizers are based on phase lock loop (PLL) design. Compared to direct analog synthesizer and direct digital synthesizer, it has the advantages of simpler design and smaller power consumption. But it still has its own difficulties to meet the above requirements for modern wireless applications.

### Noise

In monolithic design, the phase noise performance of the synthesizer is degraded not only by the phase noise of the voltage-controlled oscillator itself and the noise from the loop filter but also by the substrate noise. Since the substrate is conductive, any noise from other noisy circuits e.g. digital circuit, will couple through the substrate to the voltage-controlled oscillator (VCO) and degrade the phase noise. This noise source is difficult to predict and cannot be prevented or reduced by increasing power consumption. Large separation from noise sources and guard ring can only improve the problem a bit.

### Switching speed

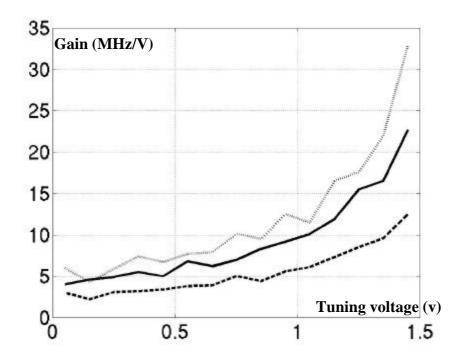

Switching speed is limited in PLL based synthesizers. In conventional design, the finest frequency resolution equals to the reference frequency. However, in order to fulfill the requirement of stability, the larger loop bandwidth is limited to approximately 1/10 of the reference frequency <sup>1</sup>. As a result, PLL synthesizers with a fine frequency resolution have a small loop bandwidth and thus a low switching speed. Moreover, at different output frequencies, the varactor of the VCO is biased with different voltages and has different gains. The loop gain is therefore not constant through out the whole output frequency range. In some frequency range, the loop bandwidth and speed are smaller than the optimum because the stability of the loop has to be ensured in all cases. Although some linearization techniques can be used<sup>2</sup>, they require the characteristic of a pre-measured varactor and thus can only provide limited linearization.

### Supply voltage

To compensate the center frequency variation in voltage controlled oscillator, a large tuning range is required. In this case, large voltage range is required to bias the varactor for large frequency range. Thus, large supply voltage is needed.

### Monolithic

To meet the tough phase noise specification, huge capacitors are needed to reduce the thermal noise in the charge-pump and loop filter. The capacitors are usually so large that they will either occupy a very large chip area or have to be put off-chip.

### Thesis overview

In this work, we will try to solve the problems mentioned above including substrate noise, frequency switching speed, supply voltage and chip area, which are faced by existing monolithic frequency synthesizers. The main emphasis of the research relies on the system improvement of the frequency synthesizer in order to solve the above problems and to relax the requirement on the circuit performance. In chapter 2, the specifications of the frequency synthesizer are discussed. In chapter 3, the proposed system and its advantages are discussed. Some detailed system parameters are also determined. Chapter 4 deals with the circuit implementations of different building blocks of the frequency synthesizer. Chapter 5 is special for the discussion on the quadrature phase and amplitude matchings in coupled-LC oscillators. In chapter 6, some layout considerations are discussed. The testing methods and experimental results are discussed in Chapter 7. Finally Chapter 8 provides a conclusion of the whole research and the contribution.

## **Chapter 2 Specifications**

### Frequency range and resolution

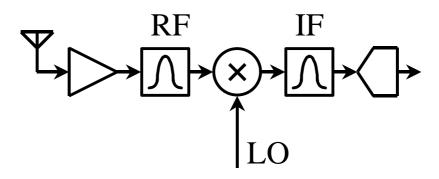

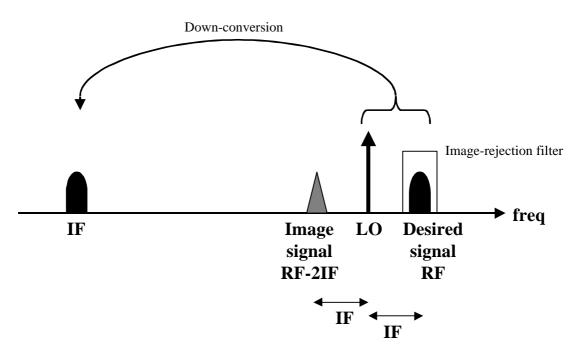

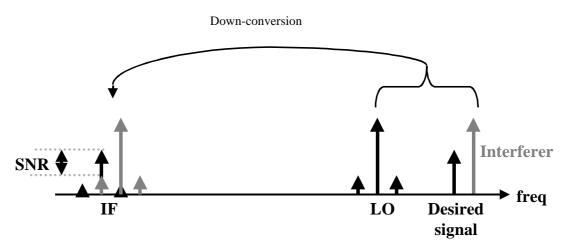

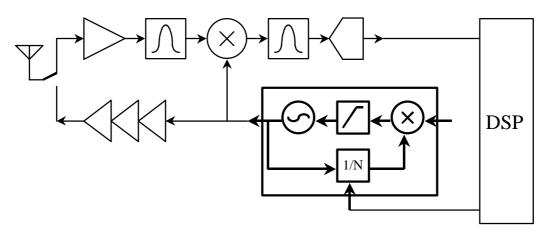

In a wireless receiver, as shown in Fig. 1, the radio-frequency (RF) signal is received through the antenna and amplified by the low-noise amplifier (LNA). Since the output frequency of the down-convert mixer is the absolute value of the difference of the two input frequencies, both the desired signal RF and the image signal RF-2IF can be mixed down to IF. Therefore RF signal is filtered by the RF image-rejection filter in order to remove the RF-2IF signal before it is down-converted as shown in Fig. 2. As the mixer performs the frequency subtraction, resultant signal of the mixer RF-LO which equals to the intermediate-frequency (IF) will pass through the channel selection filter. Only the desired channel is remained and sampled by the analog-to-digital converter.

Fig. 1 Block diagram of a receiver

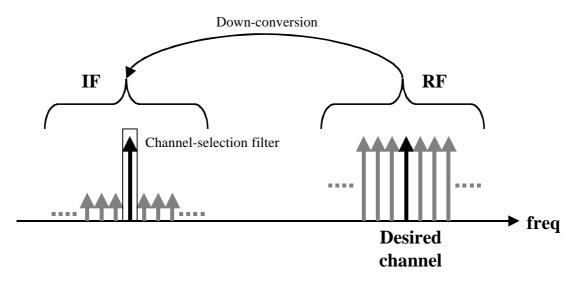

As shown in Fig. 3, the mixer will mix down the desired channel within receiver frequency band (935MHz - 960MHz) to exactly 70MHz and let the IF channel selection filter which is centered at 70MHz to filter out all other unwanted channels. As

the receiver frequency band is from 935MHz to 960MHz and the IF is 70MHz, the output frequency range of the frequency synthesizer will be from 865MHz to 890MHz. The channel spacing in the receiver band is 200kHz and therefore the frequency resolution of the frequency synthesizer is 200kHz.

Fig. 2 Frequency domain representation of the down-conversion and the relationship between RF, image, LO, and IF signals

Fig. 3 Frequency domain representation of the channel selection

## Phase noise

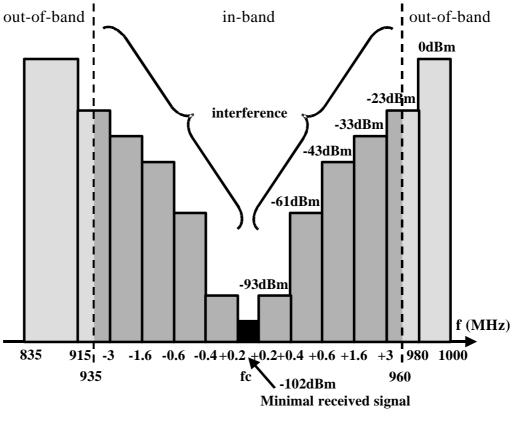

In the specification of GSM  $900^3$ , around the received signal, there is a lot of interference due to the adjacent signals.

Fig. 4 shows the profile of the maximum interference signals defined in the specifications. The power of nearest adjacent channel at 200kHz offset from the received signal can be as large as -93dBm and the maximum interference powers at 400kHz, 600kHz, 1.6MHz and 3MHz offsets are -61dBm, -43dBm, -33dBm and -23dBm. The maximum interference powers at frequency larger than 980MHz or smaller than 915MHz can be as large as 0dBm. However, since these two interference signals are outside the receiver band, most of them can be filtered out by the RF filter and they can be ignored in this case. The GSM specifications also define the minimum power level of the received signal to be -102dBm.

Fig. 4 Profile of interference signals

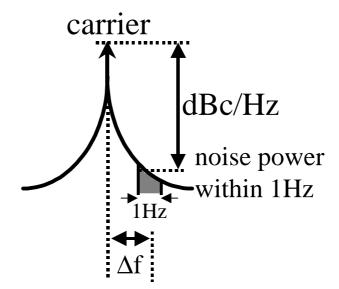

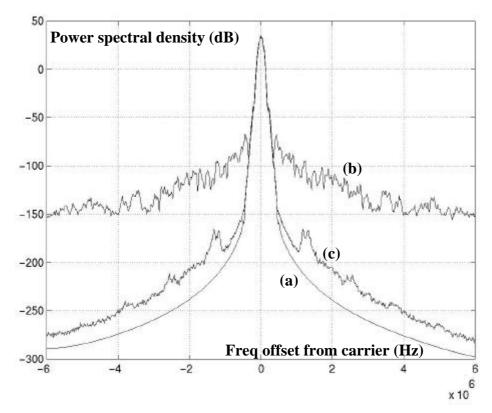

Ideally, the output of the frequency synthesizer should be a pure tone. However, due to the thermal noise of the resistors and transistors in the oscillator or some noise at the frequency tuning input of the oscillator, the phase of the oscillation will fluctuate. In frequency domain, the phase fluctuation forms a skirt of noise power around the carrier impulse as shown in Fig. 5. The phase noise is defined as the difference between the carrier power and the total noise power within 1Hz at some frequency offset  $\Delta f$  from the carrier frequency. If the noise source is white, the phase noise in the frequency domain is proportion to  $1/\Delta f^2$ .

Fig. 5 Frequency domain representation of phase noise

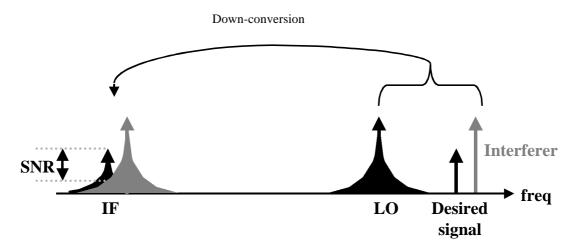

As shown in Fig. 6, if there is a large interference signal near the small desired signal and the LO signal has a phase noise skirt, both the desired signal and the interference will be mixed down to the IF. However, both signals will also have the same noise skirt as the one of the LO signal because the down-conversion is actually a convolution in frequency domain. Since the powers of the interfere signals are generally large, the noise down-converted to the frequency of the desired signals can significantly degrade the signal-to-noise ratio (SNR) of the desired signals.

Fig. 6 Effect of phase noise of LO signal

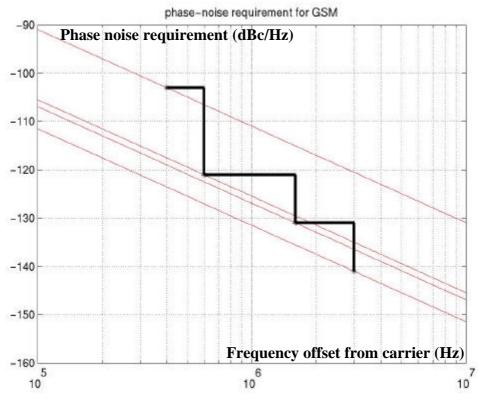

Based on the maximum interference, minimum received signal and the minimum required signal-to-noise ratio defined in the GSM specifications which is 9dB, the maximum phase noise accepted of the LO signal at different frequency offset can be calculated as following.

| required SNR   | < minimum received signal power                                              |

|----------------|------------------------------------------------------------------------------|

|                | maximum noise power                                                          |

| required SNR   | minimum received signal power                                                |

|                | maximum interference power $\times$ LO phase noise $\times$ signal bandwidth |

| LO phase noise | minimum received signal power                                                |

|                | maximum interference power×signal bandwidth×required SNR                     |

For example, at 600kHz frequency offset,

LO phase noise < -102dBm - (-43dBm) - 9dB - 53dB = -121dBc/Hz

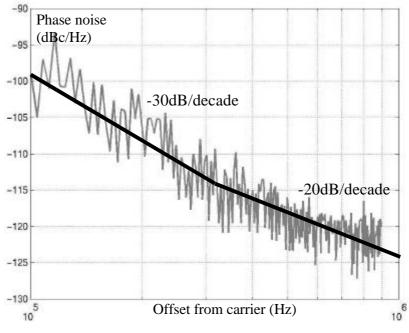

Based on this calculation, the phase noise requirements at different frequency offsets are -103dBc/Hz at 400kHz, -121dBc/Hz at 600kHz, -131dBc/Hz at 1.6MHz and -141dBc/Hz at 3MHz as shown in Fig. 7. The phase noise requirements at different frequency offset from the carrier can be compared easily by normalizing them to the same frequency offsets because the phase noise in this frequency range is proportion to  $1/\Delta f^2$ . The phase noise requirements for GSM specifications at larger frequency offsets are tougher than the ones at smaller frequency offsets. Due to the limitation of on-chip oscillators, it is impossible to meet the all the phase noise requirements. Usually, only the requirements at the two closer frequency offsets 400kHz and 600kHz are considered which is equivalent to -121dBc/Hz at 600kHz offset<sup>4</sup>.

Fig. 7 Phase noise envelope for local oscillator signal in GSM receiver

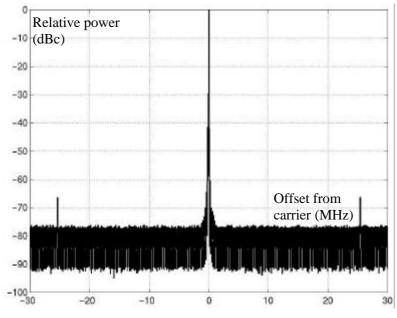

## Spurs

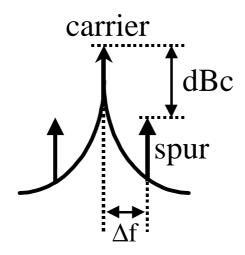

Other than the phase noise due to the internal thermal noise and external input noise, the oscillator can also be modulated by some noise of fixed frequencies due to the switching of other circuits in the synthesizer. One of the main noise sources is the switching noise of the charge pump at the reference frequency. The input noise will modulate the oscillator and be up-converted to the carrier. Two tones will appear at the upper and lower sideband of the carrier as shown in Fig. 8. These tones are called spurs and measured by the difference between powers of the carrier and the spurs at some frequency offset in the units of dBc.

Fig. 8 Frequency domain representation of spurs

Similar to the case of phase noise, as shown in Fig. 9, if there is a large interference signal near the small desired signal and the LO signal has spurs, both the desired signal and the interference will be mixed down to the IF. However, both down-converted signals will also have the spurs as the ones of the LO signal. If the spur of the down-converted inference is at the same frequency of the desired signal, it degrades the SNR of the desired signal.

Fig. 9 Effect of spurs of LO signal

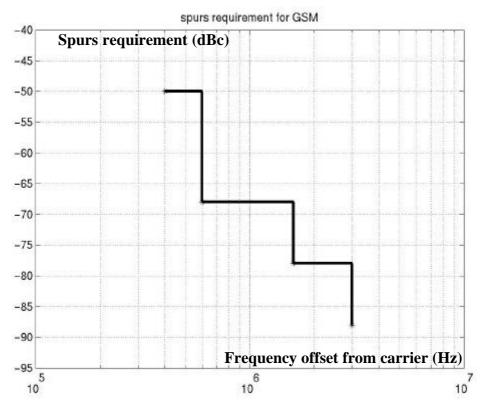

Also based on the maximum interference, minimum received signal and the minimum required signal-to-noise ratio defined in the GSM specifications, the maximum spurs accepted of the LO signal at different frequency offset can be calculated as following.

| required SNR  | < minimum received signal power                  |

|---------------|--------------------------------------------------|

|               | maximum noise power                              |

| required SNR  | < minimum received signal power                  |

|               | maximum interference power × LO spur power       |

| LO spur power | minimum received signal power                    |

|               | maximum interference power $\times$ required SNR |

For example, at 600kHz frequency offset,

LO phase noise < -102dBm - (-43dBm) - 9dB = -68 dBc/Hz

Based on this calculation, the spur requirements at different frequency offsets are -50dBc/Hz at 400kHz, -68dBc/Hz at 600kHz, -78dBc/Hz at 1.6MHz and -88dBc/Hz at 3MHz as shown in Fig. 10

Fig. 10 Spur envelope for local oscillator signal in GSM receiver

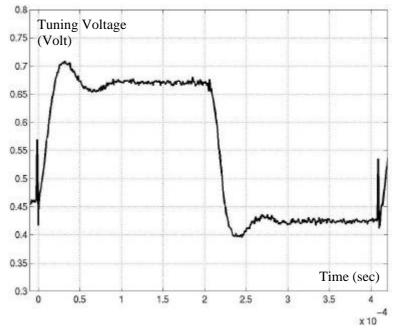

## Frequency switching time

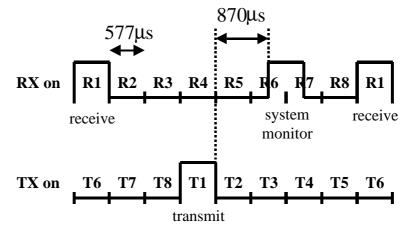

GSM uses a combination of time-division-multiple-access (TDMA) and frequencydivision-multiple-access (FDMA) schemes to provide base stations with simultaneous access to multiple users. The available frequency bands are divided into 200kHz wide channels called absolute radio frequency channel numbers (ARFCNs). Each channel is time shared among as many as eight subscribers using TDMA.

As shown in Fig. 11, the signal is received in the first time slot and the signal is transmitted in the fourth time slot. The time slot between R6 and R7 is used for system monitoring. Usually only one frequency synthesizer is used in the transceiver for both up-conversion and down-conversion in the transmitter and receiver. The minimum switching time is limited by the time to switch between the time slot for transmission

and the time slot for system monitor, in which case the frequency switching has to be finished with 1.5 time slots which is 870µs. The corresponding minimum loop bandwidth for the settling time within 870µs is around 3kHz.

Fig. 11 GSM Receive and transmit time slots

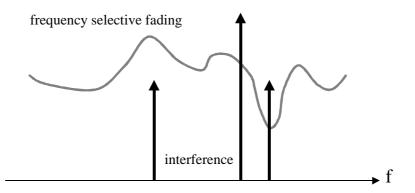

When the wireless signals are transmitted between the base station and the handsets, the signals will undergo different paths due to multi-reflection in order to reach the destination. Different paths will have different delays. The signals with different delays will interference each other constructively or destructively depended on the frequency of the signals. In this case, the wireless signals will undergo frequency selective channel as shown in Fig. 12. Signals at different frequencies will have different fading. Moreover, there are some narrowband fixed-frequency interference signals due to some near-by electronic applications.

Under the frequency selective fading and narrowband interference, some frequency slots are in deep fades or subject to large interference. One of the solutions is frequency diversity which can avoid deep-fade and narrowband interference. It is because deep-fading and interference occurs only when all the paths are in deep fades and jammed by interference.

The frequency diversity can be performed by frequency hopping. In a frequency hopping system, the frequency for the wireless signal changes from time to time. In this case, the LO signal provided by the synthesizer is required to switch between different frequencies rapidly. The switching speed of the frequency depends on different systems and purposes. In Bluetooth system<sup>5</sup>, the frequency changes around 1600 times per second.

Fig. 12 Frequency selective fading and narrowband interference

### Loop bandwidth

In addition to generating the LO signals for up-conversion or down-conversion in a receiver. The frequency synthesizer can also be used as a frequency-shift-key (FSK) transmitter<sup>6</sup>. As shown in Fig. 13, by inputting different division ratio into the prescalar of the frequency synthesizer, the output frequency of the synthesizer will changed accordingly. The output of the synthesizer can directly drive the power amplifier and the antenna. In order to directly modulating the synthesizer and using it as a transmitter, the loop bandwidth has to be larger than the bandwidth of the transmitted signals or some compensation is needed to provide a flat response for the transmitted signals <sup>6</sup>.

Fig. 13 System diagram of the proposed transceiver

## Summary of specifications

Most of the specifications of this project are based on specifications for the GSM receiver. Also some additional specifications, e.g. loop bandwidth and settling time, are partly based on specifications of the GSM transmitter and some frequency hopping systems in order to demonstrate some ideas in the frequency synthesizer. The tough specifications of supply voltage, power consumption and area are also designed to make the project challenging. Table 1 summarizes the specifications.

| Frequency range      | 865-890MHz (70MHz IF receiver)                       |

|----------------------|------------------------------------------------------|

| Frequency resolution | 200kHz (or finer for directly modulated transmitter) |

| Phase noise          | -119dBc/Hz @ 600kHz                                  |

| Spurs                | <-88dBc (in band)                                    |

| Settling time        | <865µs (or smaller for frequency hopping)            |

| Loop bandwidth       | 80kHz                                                |

| Supply voltage       | 1.5V                                                 |

| Power consumption    | <50mW                                                |

| Area                 | < 2mm x 2mm                                          |

Table 1 Summary of specifications

## **Chapter 3 System Design**

## Phase-locked loop synthesizer

There are many methods to synthesize a required frequency from a frequency reference source. The most common methods are direct analog synthesis, direct digital synthesis and phase-locked loop synthesis<sup>7, 8</sup>. However, most of the frequency synthesizer designs are dominated by phase-locked loop designs because they are simpler, smaller and less power-consuming.

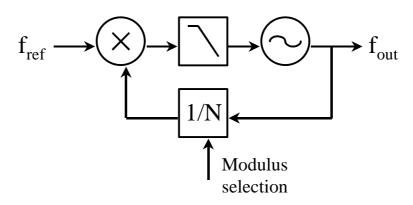

The basic block diagram is shown in Fig. 14. The voltage-controlled oscillator outputs a signal of frequency  $f_{out}$ . Then the signal  $f_{out}$  will be divided by a programmable digital counter. The frequency and phase of the resultant signal is then compared to the frequency and phase of the reference signal  $f_{ref}$  by a mixer or a frequency-phase detector. The output signal of the mixer or frequency-phase detector is filtered out by a low-pass filter. The signal at the filter output is an error signal which represents the difference of phase and frequency of the reference signal  $f_{ref}$  and the divided signal  $f_{out}/N$  and is used to control the voltage-controlled oscillator such that the signal  $f_{out}/N$  equals to  $f_{ref}$ , or  $f_{out}$  equals to N x  $f_{ref}$ .

Fig. 14 Block diagram of phase-locked loop frequency synthesizer

However, since the closed loop response of the phase-locked loop synthesizer is lowpass, the response of the phase-locked loop synthesizer for any change of the frequency of the output signal is quite slow. The fast change of the output frequency is very important in time-division dualplex and frequency-hopping systems. The change of the output frequency is done by the change of the modulus selection word.

### Existing architecture

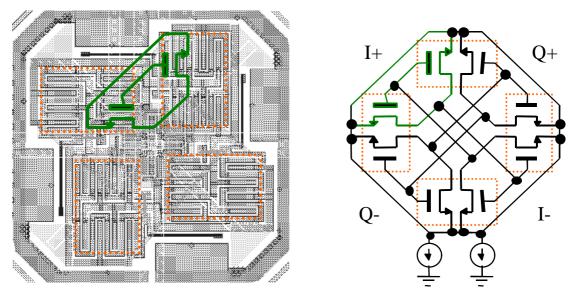

There are many different approaches to increase the frequency switching speed of the phase-locked loop synthesizer. One approach is to predict the settled tuning voltage of the VCO. By adding the predicted voltage offset from a digital-to-analog converter (DAC) to the charge pump or loop filter output as shown in Fig. 15a, the capacitance of VCO's LC tank and output frequency change immediately because the loop does not need to change and to settle down<sup>7</sup>. Although the capacitance-to-frequency relationship, which is governed by the equation  $f = \frac{1}{\sqrt{LC}}$ , is quite linear within a small range, the voltage-to-capacitance relationship of the varactor, which depends on doping and geometry, is non-linear and difficult to be predicted. Therefore, it is difficult to generate the required voltage to tune the VCO to the correct frequency. Consequently, only

coarse tuning can be provided by the DAC. The loop still has to change a lot and settle down before the desired output frequency reaches. Moreover, in order to reduce the noise from the DAC and voltage adder to the VCO, the voltage summation has to be placed before the loop filter instead of directly before the VCO. As a result, the predicted tuning voltage still has to pass through the loop filter and take time to reach the VCO.

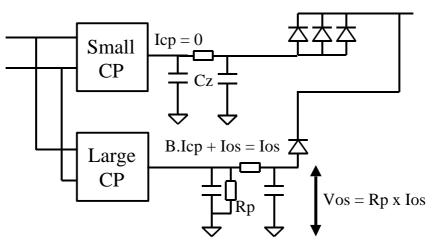

### Proposed architecture

Based on the above approach, a new architecture is proposed in this work. Instead of doing the addition in voltage domain, the addition is done in capacitance domain. The addition is implemented as easily as putting two capacitors in parallel. Originally, the voltages from the DAC and charge pump is added by a voltage adder and the resultant voltage controls the capacitance of the LC tank of the VCO through a varactor with an unknown and non-linear characteristic. In the proposed architecture, the DAC is replaced by a binary-weighted switchable-capacitor array (SCA), and the voltage adder is replaced by a parallel connection of the switchable-capacitor array and the varactor, as shown in Fig. 15b.

Channel selection

Fig. 15 The evolution of fast-switching PLL frequency synthesizer – a) two possible configurations employing DAC to increase frequency switching speed; b) employing switchable-capacitor-array to increase frequency switching speed

### Advantages

In the proposed approach, the capacitance of the varactor controlled by the loop and the capacitance of the switchable-capacitor array are added. The capacitance of the switchable-capacitor array is controlled directly and linearly without through a varactor which has a non-linear voltage-to-capacitance characteristic. As a result, the output frequency can be controlled quite linearly and fine tuning from the switchable-capacitor

array is now possible. Moreover, the addition of capacitance is simply by connecting two capacitors in parallel and no voltage adder is needed.

Since the tuning of frequency is mainly done by the switchable-capacitor array, the gain of the varactor and the change of the tuning voltage can be very small. These two features provide many other advantages of this approach.

#### Faster switching speed

Due to the linear control of the capacitance in the switchable-capacitor array, fine tuning from the switchable-capacitor array is possible. The accurate amount of capacitance added can change the output frequency close enough to the desired value and the loop can settle quickly. Moreover, the frequency change by adding of the extra capacitance is faster because the control of the addition bypasses the loop filter.

The small variation in the tuning voltage of the varactor results in a constant bias condition and gain of the varactor. The constant and optimal loop bandwidth for speed is obtained without any linearization technique.

### Lower supply voltage

In order to compensate the center frequency shift due to process variations, the tuning range of the voltage-controlled oscillator usually has to be very large and a large range of tuning voltage is required for the large tuning range. As a result, a large supply voltage is needed.

In the proposed architecture, as most of the tuning is done by the switchable-capacitor array and the variation of the tuning voltage of the varactor is very small, the tuning range of the voltage-controlled oscillator is independent of the supply voltage. Therefore, a small supply voltage can be used. The small-variant tuning voltage also prevent the PN junction varactor used from being forward biased and simplifies the circuit design of the analog signal path due to the small required dynamic range.

#### Smaller chip area

As most of the tuning is by the switchable-capacitor-array, the required tuning range and the gain of the varactors is very small. More noise from the loop filter can be tolerated in the proposed architecture because any change in the tuning voltage has very small effect on capacitance of the varactor and the frequency of the VCO. As a result, much smaller on-chip capacitors of the loop filter can be used to filter out the noise.

#### Low phase noise

Since the capacitance of the switchable-capacitor array is quite constant when the NMOS switches is fully turned on or off and the gain of the varactor is very small, the substrate noise can only change the total capacitance and the output frequency of the LC voltage-controlled oscillator very little through the varactor and switchable-capacitor array. This can reduce the phase noise of the voltage-controlled oscillator due to unpreventable substrate noise and larger tolerance to substrate noise is obtained.

In addition to smaller power consumption, the absence of the noisy digital-to-analog and voltage adder can also reduce thermal noise added in the tuning voltage which would modulate the voltage-controlled oscillator and degrade the phase noise.

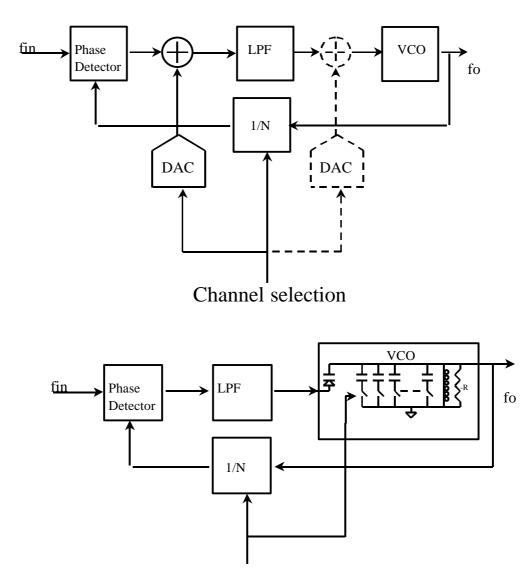

### Fractional-N synthesizer

The above-proposed architecture provides a simple solution to increase the frequency switching speed of phase-locked loop frequency synthesizers. There are also many variations of the basic phase-locked loop frequency synthesizer to increase the performance of the synthesizer <sup>9</sup>. One of the variations is the multi-loop phase-locked loop frequency synthesizer which employs two or more phase-locked loop frequency synthesizers. The most common design is dual-loop phase-locked loop frequency synthesizers. There can be a number of different configurations. One of the frequency synthesizer can generate the reference frequency to the other frequency synthesizer, as shown in Fig. 16a. Or, one of the frequency synthesizer can generate a frequency offset added or subtracted from the other frequency synthesizer, as shown in Fig. 16b.

Fig. 16 Block diagrams of some dual-loop synthesizer designs

In the original phase-locked loop frequency synthesizer (Integer-N frequency synthesizer), the output frequency  $f_{out}$ , which equals to N x  $f_{ref}$ , is an integral multiple of the reference frequency  $f_{ref}$  because the frequency divider can only have integer division ratio. However, by continuously changing the division ratio of the frequency divider, it is possible to have an average division ratio which is a fractional number. For example, if a frequency divider have the division ratio 4 in 50% of time and the division

ratio 5 in the other 50% of time. The average division ratio will be 4.5. This is referred to a fractional-N frequency synthesizer.

The fractional-N frequency synthesizer is actually an integer-N frequency synthesizer with a changing division ratio in the frequency divider. Only some additional digital circuits are needed to generate a continuously changing division ratio. This makes the design to be more simple and robust than the multi-loop frequency synthesizer as multiple hardware of the multi-loops, filters and mixers are needed in multi-loop frequency synthesizer. Therefore, this design is based on fractional-N PLL architecture.

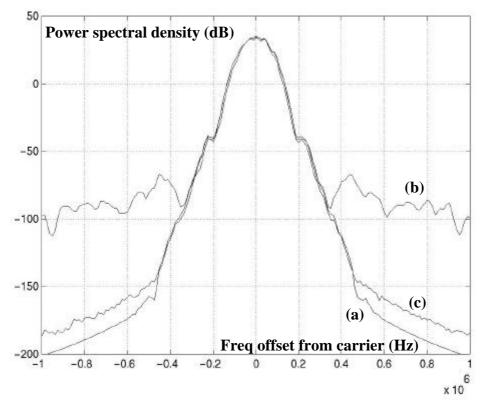

### Design criteria

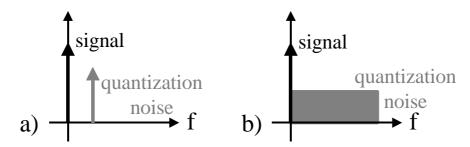

One drawback of the fractional-N synthesizer is that quantization noise is added to the loop because there are only a few division ratios (quantization level) in the frequency divider but they will represent the division ratios in between. In the case of a constant fractional division ratio required, the quantization noise generated is a single frequency tone, as shown in Fig. 17a, in which the frequency depends on the fractional division ratio. In case of a random changing division ratio required, the quantization noise generated has a white noise spectrum as shown in Fig. 17b. To solve the problem, a sigma-delta modulator can be used before the divider <sup>10</sup>. For a fractional number input (Fig. 18a), the sigma-delta modulator can redistribute the quantization noise such that the most of the noise is located at higher frequencies (Fig. 18b). The resultant high frequency noise can be filtered out by the low-pass response of the loop (Fig. 18c), and very little noise is left.

Fig. 17 Quantization noise in frequency domain

Fig. 18 Quantization noise in a sigma-delta Fractional-N synthesizer

To design a fractional-N PLL synthesizer, three parameters, including reference frequency, loop bandwidth, number of orders of the sigma-delta modulator, have to be

determined. These parameters mainly determine the switching speed, spurs and noise of the loop.

### Quantization noise

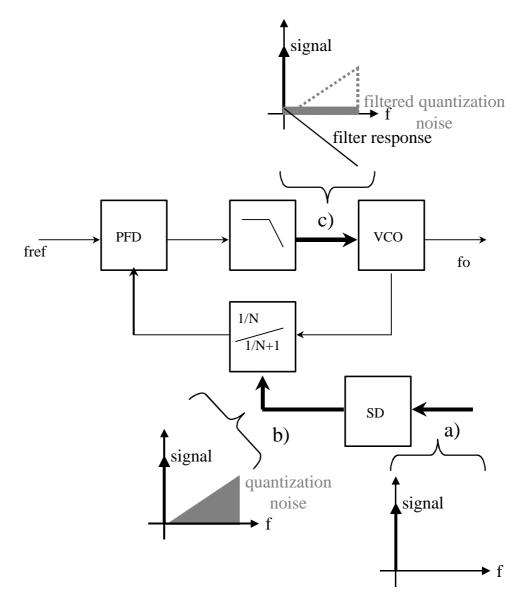

Higher clock frequency (reference frequency of the phase-locked loop) and order of the sigma-delta modulator can force more noise at higher frequencies. Lower loop bandwidth can filter out more noise at high frequencies. For the phase noise requirement of -121dBc/Hz @ 600kHz offset, the required maximal loop bandwidths and minimal reference frequencies are shown in Fig. 19 for second, third and fourth-order sigma-delta modulators used. In this design, reference frequency of 25.6MHz and third-order sigma-delta modulator can provide maximal 300kHz loop bandwidth for the required phase noise performance. The reference frequency of 25.6MHz is used because it can simplify the design of the modulator if the channel spacing (e.g. 200kHz in GSM) is the reference frequency divided by  $2^{N}$ . Moreover, since the reference frequency is 25.6MHz, any spurs in the output of the frequency synthesizer will be multiple of 25.6MHz which is already located outside the receiver band. Only the out-of-band noise which is already attenuated a lot by the RF image rejection filter can be mixed down to IF by the spurs at 25.6MHz offset.

### System parameters

The frequency synthesizer is designed for a GSM receiver. The phase noise requirements are -103dBc/Hz at 400KHz and -121dBc/Hz at 600KHz offset, respectively. The frequency range is 865-890MHz for a 70-MHz IF with 200KHz

resolution. The loop bandwidth is 80KHz. The whole synthesizer is operated with a single 1.5-V supply.

Fig. 19 Maximal loop bandwidths and minimal reference frequencies for second, third, fourth-order sigma-deltra modulators for phase noise requirement of -121dBc/Hz @ 600kHz offset

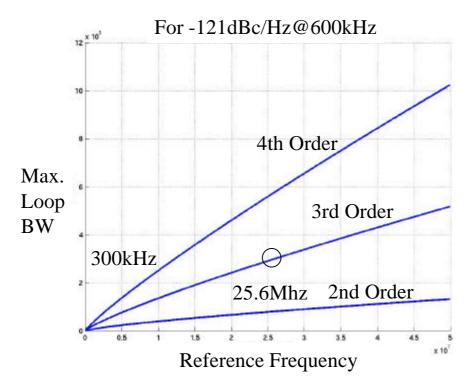

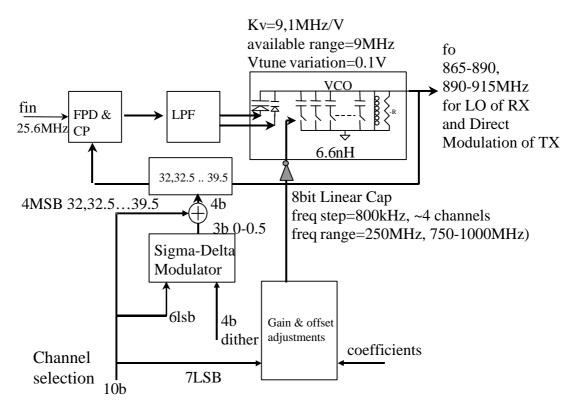

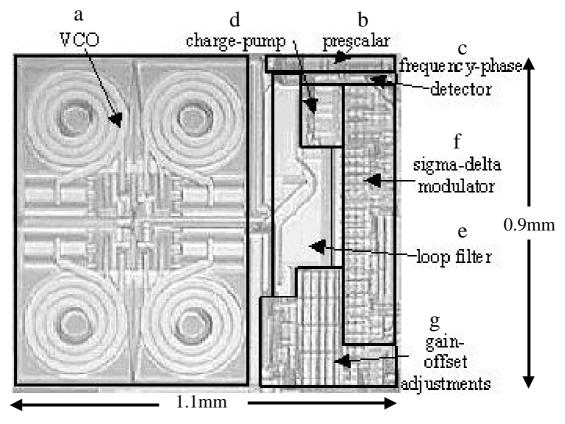

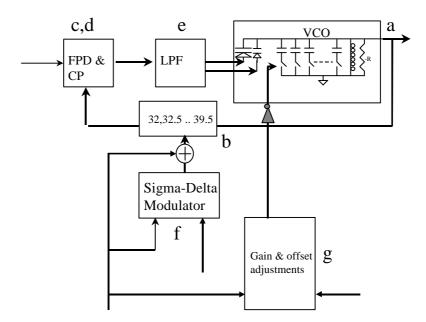

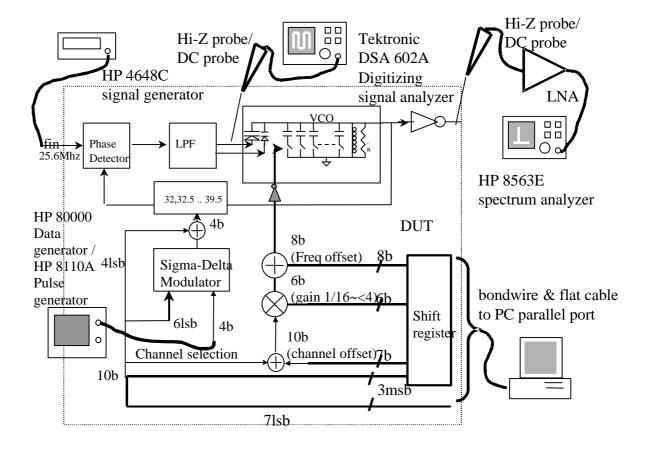

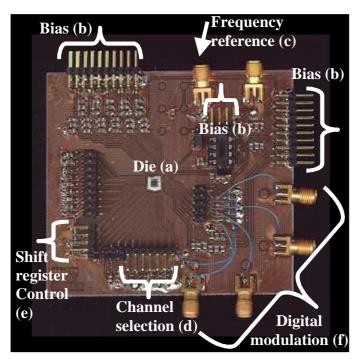

The complete system includes a fractional-N phase-locked loop synthesizer, and gain and offset adjustment circuits for the switchable-capacitor array as shown in Fig. 20. The PLL synthesizer includes a LC VCO with switchable-capacitor array, an improved loop filter, a charge-pump, a frequency-phase detector, a multi-modulus prescalar, and a third-order digital sigma-delta modulator.

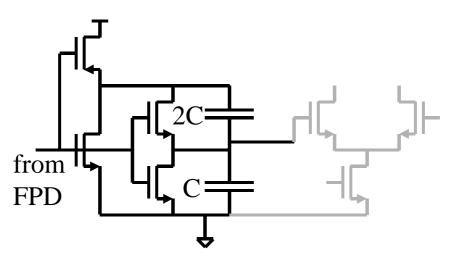

The fractional-N phase-locked loop synthesizer is based on third-order sigma-delta fractional-N design with a 25.6-MHz reference frequency. The fractional-N synthesizer includes an integer-N phase-locked loop synthesizer and a digital sigma-delta modulator. Since a 25.6-MHz reference frequency and a prescalar with the division ratios from 32 to 39.5 are used, the output frequency range is from 25.6MHz x 32 =

819.2MHz to 25.6MHz x 39.5 = 1011.2MHz and the minimal frequency resolution is 25.6MHz x 0.5 = 12.8MHz. The 16 division ratios are controlled by a 4-bit digital signal. In order to generate the channels with a 200-kHz spacing, a digital sigma-delta modulator of at least 6 bits is needed because 12.8MHz /  $2^6 = 200$ kHz. Each least significant bit of the 6-bit sigma-delta modulator represents a  $0.5 / 2^6$  in the division ratio of the prescalar. Including the four bits to directly control the prescalar, a 10-bit channel selection word is required to control the output frequency.

Fig. 20 Detailed system diagram of this design

Extra four bits added in the sigma-delta modulator are for the dither signal to random the input of the sigma-delta modulator in order to prevent the problem of pattern noise at the output of the sigma-delta modulator.

In a higher-order digital modulator, the output signal swing is larger than the available output value (it will be discussed more in Chapter 4). For a third-order modulator with the output value between 0 and 0.5, the signal swing can be up to -1 and 2. Due to the extra signal swing required, the available division ratios will be reduced. As a result, this prescalar with extra division ratios is used. The minimum and maximum division ratios with this prescalar will become 32-(-1)=33 and 39.5-2+0.5=38 which corresponds to the output frequency 25.6MHz x 33 = 844.8MHz and 972.8MHz. The available output frequency range can still cover the required frequency range (865-915MHz) in both receiver and transmitter systems.

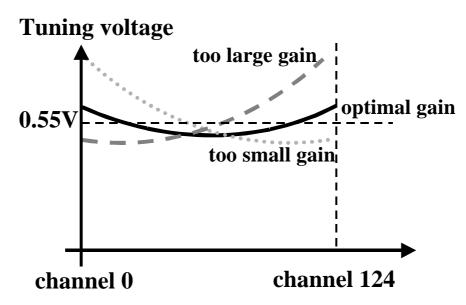

The lower seven bits of the channel selection word represents the 125 channels. These seven bits are used to control the switchable-capacitor array to obtain the correct output frequency. Since these seven bits only represent the channel number but not the exact frequency of the channel, a frequency offset is added to obtain the correct frequency for the channels. Moreover, the frequency change due to a change in the least significant bit in the switchable-capacitor array does not represent exactly a channel. A gain adjustment is required to relate the channel number and the corresponding number of the switchable capacitors.

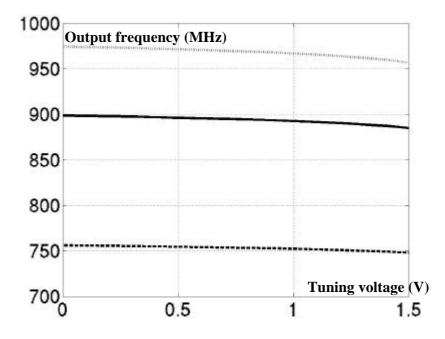

A 8-bit switchable-capacitor array is used to provide around 300-MHz tuning range (from 800MHz to 1100MHz) and 800-kHz frequency step. The varactors in the voltage-controlled oscillator can provide about 9MHz/V. As a result, the tuning voltage of the varactors will vary within 0.1V.

# **Chapter 4 Circuit Implementation**

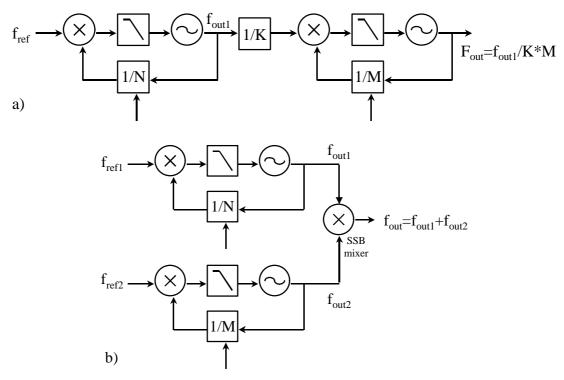

## Voltage-controlled oscillator

### Quaduature LC oscillators

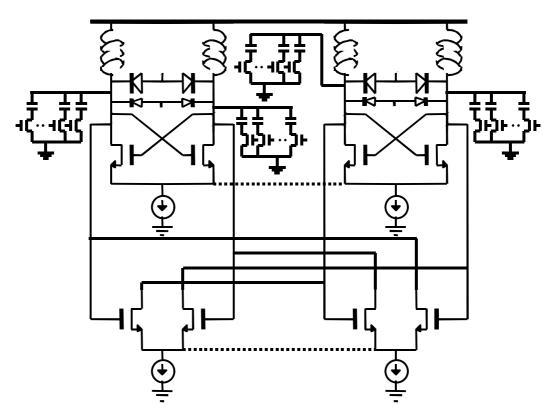

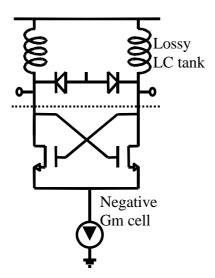

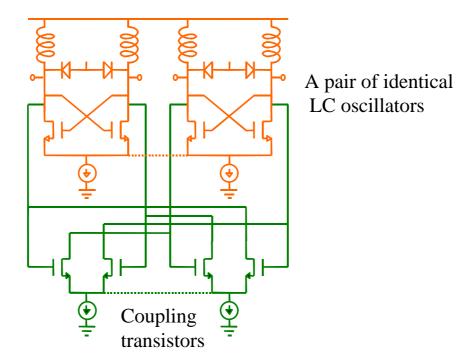

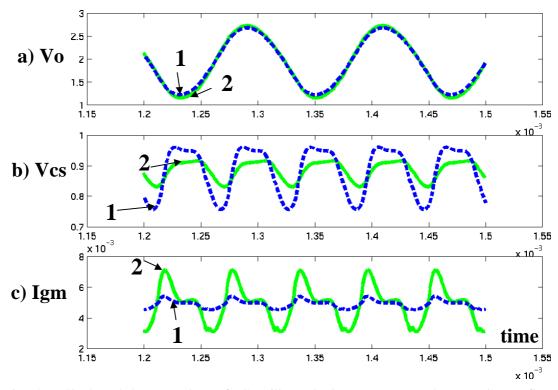

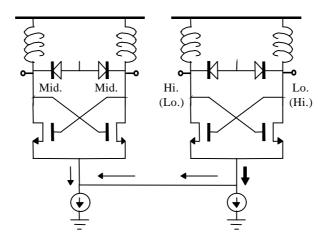

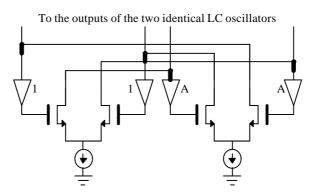

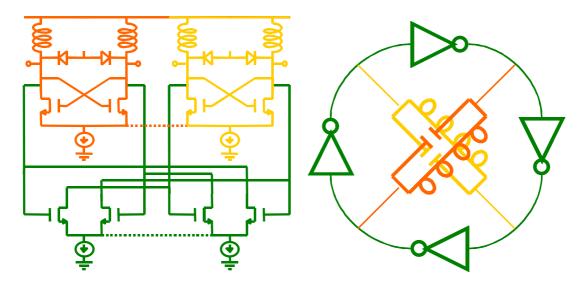

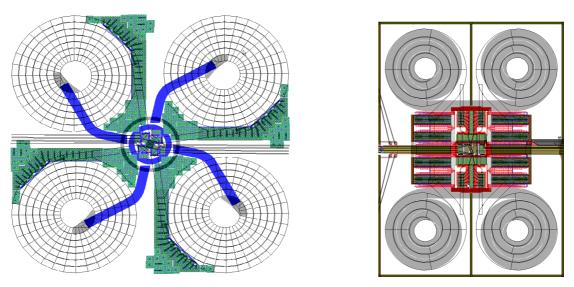

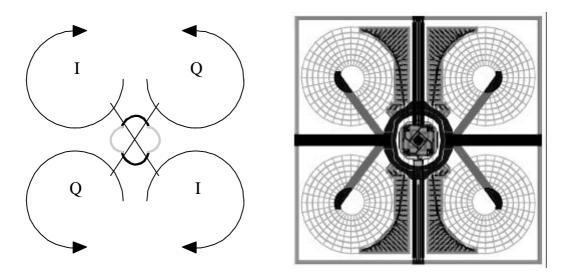

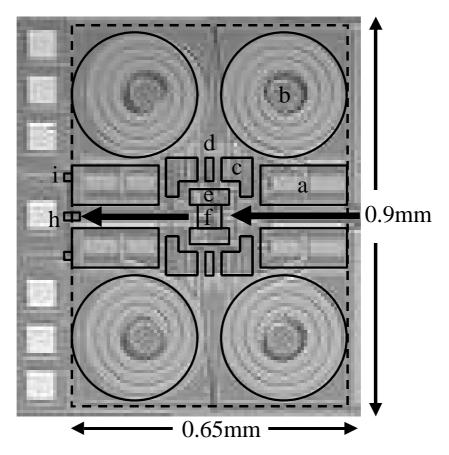

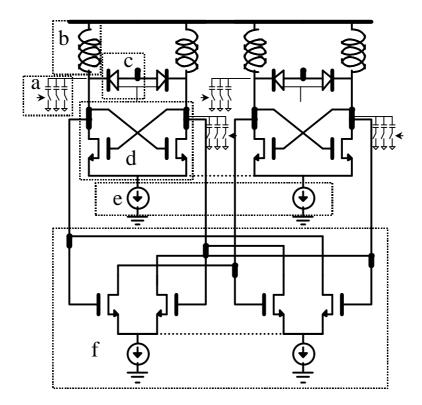

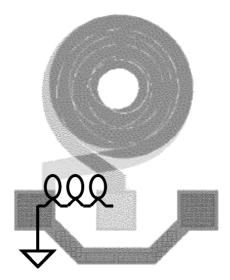

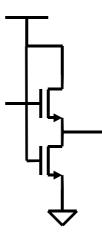

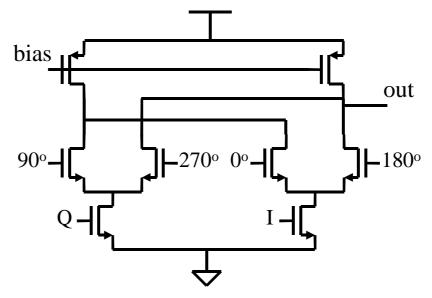

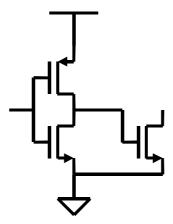

The voltage-controlled oscillator, as shown in Fig. 21, includes two identical differential LC oscillators which are mutually coupled by four coupling transistors to provide quadrature phase outputs<sup>11</sup>. The LC oscillator employs two-layer (metal 2 and metal 3) spiral inductors. Each oscillator contents an 8-bit switchable-capacitor-array as the main frequency tuning and two small varactors as the fine frequency tuning.

Fig. 21 The schematic diagram of the voltage-controlled oscillator with switchable-capacitor-array

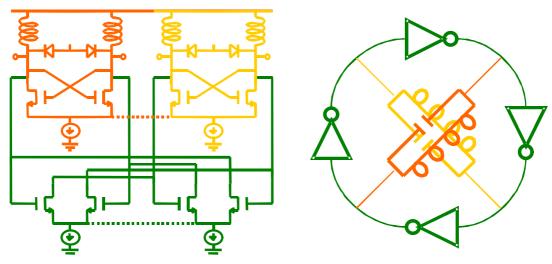

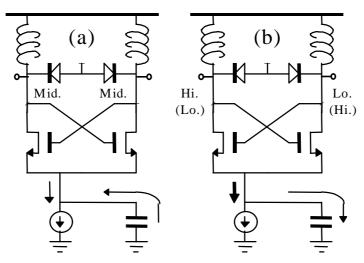

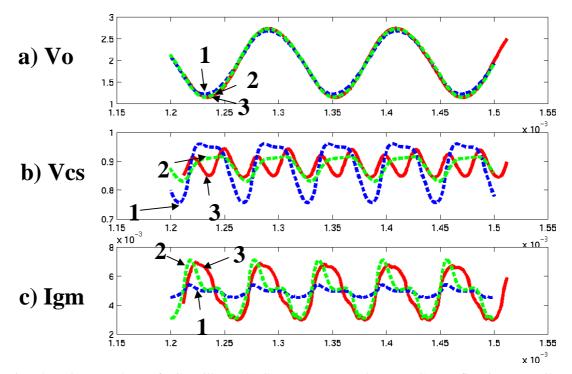

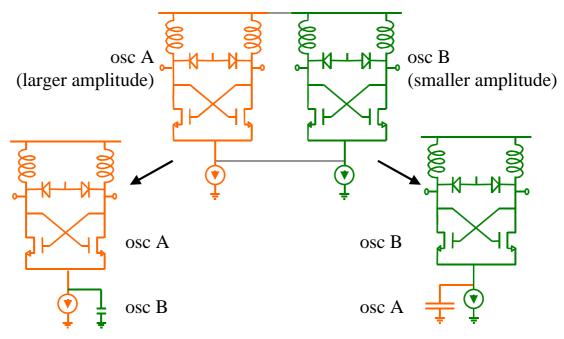

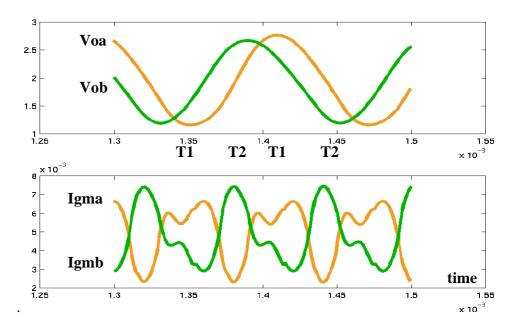

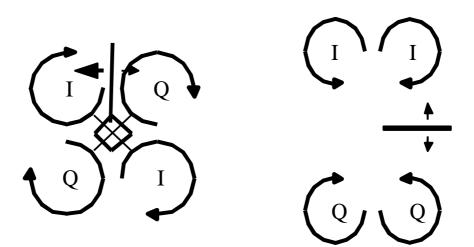

The coupled-LC oscillators can be viewed as two LC oscillators put in a four-stage ring oscillators, as shown in Fig. 22. Each stage of the ring oscillator has a phase shift of 90 degrees. Inside this frame of the ring oscillator, the two LC oscillators will have a 90-degree phase difference between their outputs. As the noisy ring oscillator maintains the quadrature phases, the two LC oscillators maintain the purity of frequency. By sharing the current sources, both amplitude and phase matchings of the outputs of the two oscillators are even better maintained<sup>12</sup> (more discussions in the coupled-LC oscillators will be in Chapter 5).

Fig. 22 Another view of coupled LC oscillators

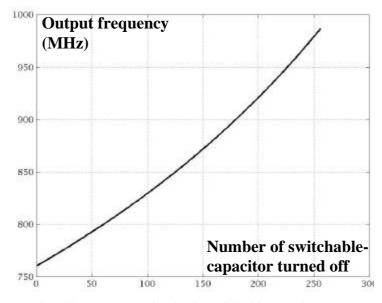

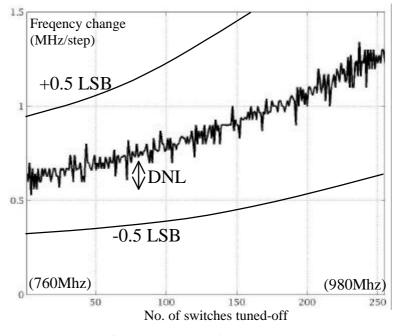

#### Switchable-capacitor-array

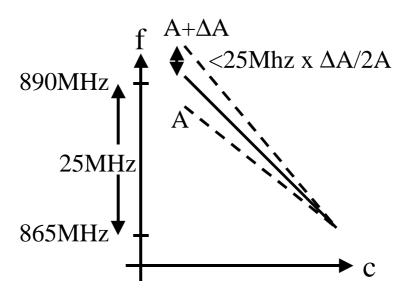

The frequency of oscillator is mainly controlled by the switchable-capacitor array. The switchable-capacitor array is used to directly control the center frequency of the oscillator for fast switching between frequencies. It should also have a large tuning range to compensate the center frequency shift of the oscillator due to the process variation and inaccurate modeling. Moreover, it can reduce the required tuning range and gain of the varactors. The most important is that it should not degrade the overall performance compared to the case of using a varactor for tuning.

The finest tuning resolution by the switchable-capacitor array depends on the nonlinearity of the relationship between the frequency and the capacitance. The relationship between the frequency and the capacitance of the switchable-capacitor array is governed by the simple relationship,

$$f = \frac{1}{\sqrt{LC}}$$

$$f + \Delta f = \frac{1}{\sqrt{L(C + \Delta C)}} = f\left(1 - \frac{1}{2}\frac{\Delta C}{C} + \frac{3}{8}\left(\frac{\Delta C}{C}\right)^2\right)$$

$$\frac{\Delta f}{f} = -\frac{1}{2}\frac{\Delta C}{C} + \frac{3}{8}\left(\frac{\Delta C}{C}\right)^2$$

As

$$\frac{\Delta f}{f} = \frac{25MHz}{890Mhz}$$

,

$$\frac{\Delta C}{C} = -0.054$$

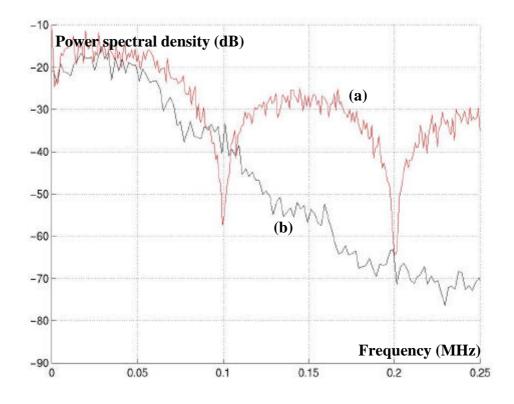

For convenience, we assume the change in frequency proportional to the change in capacitance. This assumption is valid because the relationship between the frequency and the capacitance is quite linear within a small range. In this case, a binary-weighted switchable-capacitor array can be used to change the oscillation frequency in a linear fashion.

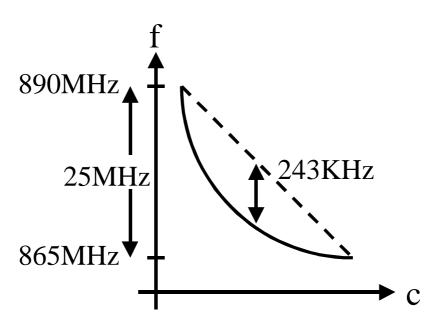

The maximal frequency deviation between the actual frequency (the solid line in Fig. 23) and the linear approximation (the dashed line) occurs when half of the capacitors are turned on.

Fig. 23 Tuning curve of the oscillator by switchable-capacitor-array

As half of the capacitors in the array is turned on,

$$\frac{\Delta C}{C} = \frac{-0.054}{2} = -0.027$$

Maximal frequency deviation

$$= 12.5Mhz - f\left(-\frac{1}{2}\frac{\Delta C}{C} + \frac{3}{8}\left(\frac{\Delta C}{C}\right)^2\right)$$

$$= 12.5Mhz - 12.257Mhz$$

= 243 Khz

The maximal frequency deviation due to the non-linear relationship between the frequency and the capacitance is 243KHz at the frequency around 890MHz. The frequency deviation is equivalent to around 1.2 channel of 200KHz. This deviation can be compensated by the change of the capacitance of the varactor when the loop is locked.

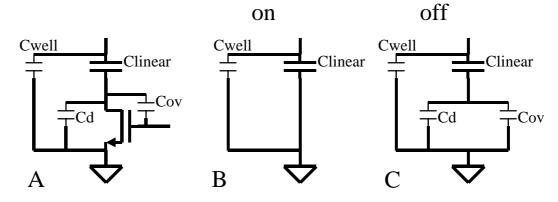

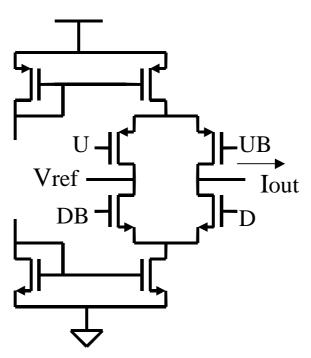

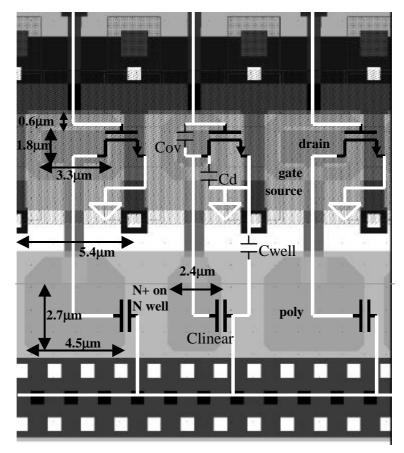

The finest tuning resolution also depends on the minimal size of the switchable capacitor. The switchable-capacitor-array employs linear capacitors and donut NMOS transistors as the switches, as shown in Fig. 24a. The donut transistor is used because of the smaller drain parasitic capacitance<sup>13</sup>. The switchable-capacitor-array includes a 7-bit binary-weighted array of unit switchable-capacitor and an extra half-size switchablecapacitor as the least significant bit. Totally, this 8-bit array can provide around 300MHz tuning range (from 800MHz to 1100MHz) and 800kHz frequency resolution which is equivalent to 4 frequency channel spacings. The available tuning range should be good enough to compensate the center frequency shift due to the process variation or the inaccurate modelings of the inductor and capacitors. Each of switchable-capacitors in the 7-bit binary-weighted array includes a 26.7fF linear capacitor and a 11.5u/0.5u donut transistor while the half-size switchable-capacitor includes a 14.3fF and a 8.5u/0.5u donut transistor. When the switches are off, there are about (2.8fF+2.8fF+3.95fF)=9.55fF and (1.5fF+1.9fF+2fF)=5.4fF remained in the normalsized and half-sized unit switchable-capacitors due to the drain parasitic capacitance (Cd), the gate-to-drain overlap capacitance (Cov) and the Nwell-to-substrate capacitance of the linear capacitors (Cwell) respectively, as shown in Fig. 24c. The changes of capacitance are about 63% of the maximum value for both switchablecapacitors of different sizes. Higher resolution of the switchable-capacitor array is also possible by using smaller unit linear capacitors and switches. However, the increase in the parasitic capacitance will limit the overall tuning range of the array.

Fig. 24 Models of an unit switchable-capacitar (A) general case (B) turn-on (C) turn-off

The quality factor of the linear capacitor is very good (>50) because it is just a parallel plate capacitor with N+ active and silicide poly of low resistance as the two plates. The quality factor of the switchable-capacitor array is mainly limited by the turn-on resistance of the transistor. There is a trade-off between the quality factor and the tuning range of array because larger switches can reduce resistance but increase parasitic capacitance at the same time. For a 11.5u/0.5u NMOS switch, the turn-on resistance with a 1.5V supply is 3400hms. The quality factor of a turn-on switchable-capacitor is designed to be 19 which does not degrade the overall quality factor of the LC tank too much because it is about 5-10 times larger than the quality factor of the spiral inductor. Further increase of the quality factor of the switchable-capacitor array by increasing the switch size has little effect on the overall qualify factor, but the increase of the parasitic capacitance will reduce the available tuning range.

#### Varactor

As the minimal frequency resolution of the switchable-capacitor array is 800kHz, the small varactors have to provide the remaining 800kHz tuning. Since only very small tuning range is needed, the voltage-controlled oscillator with small gains of 9Mhz/V can already cover the whole range while the tuning voltages need to vary by only 0.1V

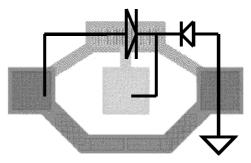

for 800KHz frequency deviation. The voltage-controlled oscillator is turned by the two varactors based on parasitic PN junction diode of P+ active and N-well, as shown in. There are totally 18 and 186 unit PN junction diodes for the two varactors. Each diode has around 2.1fF at 1V reverse bias and the capacitance changes around 15% per volt. Each diode also shares around 1.5fF Nwell-to-substrate parasitic capacitance which further reduces the tuning range of the varactor. The overall tuning range of the varactors is only about 9% per volt, from 0.74pF to 0.8pF.

Fig. 25 Cross section of the parasitic PN junction varactor

This parasitic PN junction varactor has the quality factor of around 30 by minimizing the size of unit diode in the array. As the quality factor of the diode degrades a lot when the diode is forward-biased, the available biasing range of the diode is very limited as the cathode is connected to the large-swing output. However, it is not a problem in this design because the diode is always 1V reversed-biased with variation of only 0.1V.

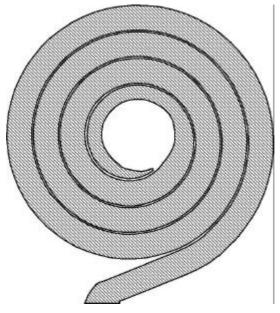

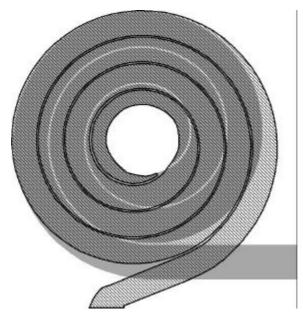

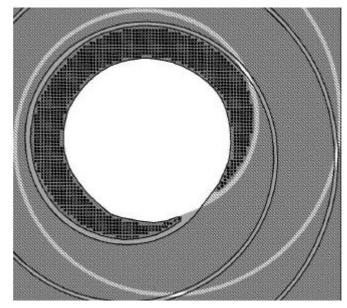

#### Inductor

The inductors used are double-layer (Metal 3 and Metal 2) circular spiral inductors. The spiral inductor is designed and simulated by the ASITIC program <sup>14</sup>. The inductance is 6.6nH and the parallel parasitic capacitance is 0.6pF. However, since the program ignores loss due to the substrate eddy current, the quality factor of the inductor calculated by the program is totally incorrect. From previous trials, the quality factor of

spirals of similar sizes is around 2-2.5 which will dominate the overall quality factor of the whole LC tanks and limit the phase noise performance of the oscillator.

#### Phase noise performance

The phase noise of a LC oscillator can be calculated by the equation,

$$L(\Delta w) = \frac{kTR_s (1+A) \left(\frac{w_o}{\Delta w}\right)^2}{\frac{V^2/2}{2}}$$

where Rs is the equivalent series resistance of the LC tank, V is the oscillation amplitude and A is the excess noise factor of the oscillator. The phase noise depends on the power of the carrier ( $V^2/2$ ), the noise power of the lossy resistance (kTRs), and the noise power of the compensation (kTRsA).

To determine the phase noise, the power of the carrier, the noise power of the lossy resistance, and the noise power of the compensation. The noise power due to the lossy resistance in the LC tanks depends on the resistance in the inductor and the varactor which is process-dependent. The carrier power (or the amplitude of oscillation) and the compensation can be calculated based on the criterion for oscillation. The simplest criterion for oscillation is:

### "Loop gain is larger than one when 360° phase shift."

In a most simple LC oscillator, as shown in Fig. 26, the criterion can be explained as follow:

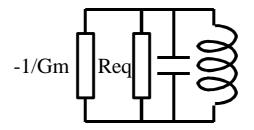

*"The product of Gm and Req is larger than one"* where the Gm is the tranconductance to compensate the loss in the LC tank, and Req is the equivalent parallel resistance of LC tank at resonance. The product of Gm and Req is the loop gain at 360° phase shift.

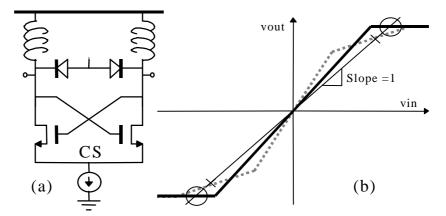

There is another theory of LC oscillator based on negative conductance to describe the oscillation. The criterion for oscillation *is "The magnitude of the negative conductance Gm is larger than the positive conductance 1/Req"*.

Fig. 26 Model of a simple LC oscillator

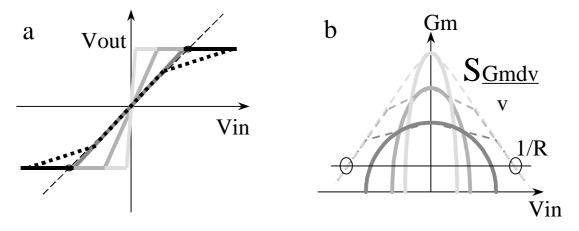

Both theories explains the oscillation but in different views. To apply these theories to determine the oscillation amplitude and the required compensation, a generalized criterion can be used – *"The average product of Gm and Req is larger than one"* or *"The average magnitude negative conductance Gm is larger than the positive conductance 1/Req"*. The region where the criterion is true determines the oscillation amplitude. The graphical representations of the criterion in the two theories are shown in Fig. 27. Based on loop gain theory, the oscillation stops when the average loop gain is smaller than one. The amplitude of oscillation will be the voltage where the loop gain (Vout/Vin) cuts the line of unity slope. Based on negative conductance, the oscillation stops when the average negative conductance  $(\int_0^V Gm dV_V)$  is smaller than the reciprocal of the resistance (1/R). The voltage (Vin=Vout when oscillation) where the average negative conductance cuts the reciprocal of resistance is the oscillation amplitude. Although there are different loop gains and different negative conductance

in Fig. 27a and Fig. 27b, the same oscillation amplitude can be obtained if their average values within the oscillation range are the same. As the loop gain and the negative conductance are usually decreasing, the loop gain and the negative conductance at the center point have to be larger than 1 and 1/R in order to start the oscillation.

Fig. 27 Graphical representations of the generalized criterion for oscillation a) based on loop gain b) based on negative conductance