## A 4-Path 60GHz CMOS Phased-Array Receiver

by

### WU Liang

A Thesis Submitted to

The Hong Kong University of Science and Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in the Department of Electronic and Computer Engineering

August 2012

#### **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Wuldow J WU Liang

August 2012

### A 4-Path 60GHz CMOS Phased-Array Receiver

by

#### WU Liang

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects,

and that any and all revisions required by

the thesis examination committee have been made.

Prof. Howard C. Luong Thesis Supervisor

**Prof. Christopher Y. H. Chao** Thesis Examination Complittee Member (Chairman)

Û

**Prof. Yi-Kuen Lee** Thesis Examination Committee Member

**Prof. Patrick Yue** Thesis Examination Committee Member

**Prof. Philip K. T. Mok** Thesis Examination Committee Member

**Prof. Ross D. Murch** Head of Department

Department of Electronic and Computer Engineering The Hong Kong University of Science and Technology

August 2012

### Acknowledgement

It is rewarding to study in HKUST. I would like to take this advantage to express my sincere thankfulness to those who have taught me, helped me and supported me during these years.

First of all, I am indebted to my research supervisor, Prof. Howard C. Luong. He brought me into the field of RF integrated circuits design; his insightful advices in my researches inspired me a lot; and his academic spirit always encourages me to pursue the best and to do the best.

I am also grateful to Mr. Frederick Kwok for his professional technical support on measurement equipment, PCB board fabrication and chip bonding, and Mr. S. F. Luk and Mr. K. W. Chan for their technical assistance.

It is fortunate to have my study in Analog Research Laboratory and meet many nice colleagues: Alan Ng, Annby Rong, Jun Yin, Shi Yuan Zheng, Alvin Li, Hiu Fai Leung, Huyen Le, Yue Chao, Peng Chong Wang and Rui Liu. I would like to thank them as well that they offered me much help in various aspects and made my life at HKUST enjoyable.

In addition, my gratitude goes to my supervision committee and thesis exam committee: Prof. Patrick Yue, Prof. Philip K. T. Mok, Prof. Amine Bermak, Prof. Yi-Kuen Lee, Prof. Christopher Y. H. Chao and Prof. Elvis Pui-In Mak.

Last but not the least, I would like to show my great appreciation to my family, in particular my parents, my parents-in-law, my elder sister and my dear wife, for their understanding, unlimited support, continuing encouragement, and care. Their unyielding love is an indispensable source of my strength.

## **TABLE OF CONTENTS**

| Title Pa | age                             | i     |

|----------|---------------------------------|-------|

| Author   | ization Page                    | ii    |

| Signatu  | ıre Page                        | . iii |

| Acknow   | wledgement                      | iv    |

| Table of | of Contents                     | v     |

| List of  | Figures                         | xii   |

| List of  | Tables x                        | vii   |

| Abstrac  | ct                              | xix   |

| СНАР     | TER 1 INTRODUCTION              | 1     |

| 1.1      | Background                      |       |

| 1.2      | Research Motivation             |       |

| 1.2      | Objective of the Dissertation   |       |

|          | iography                        |       |

| Dion     | ography                         | ,     |

| CHAP     | TER 2 SYSTEM SPECIFICATION      | 8     |

| 2.1      | Specification of IEEE 802.15.3c | 8     |

| 2.1      | 1.1 Overview                    | 8     |

| 2.1      | 1.2 Frequency Allocation        | 9     |

| 2.1      | 1.3 Transmit Power 1            | 0     |

| 2.1      | 1.4 Data Rate 1                 | 0     |

| 2.1      | 1.5 Error Vector Magnitude 1    | 1     |

| 2.1      | 1.6 Frame Error Rate 1          | 12    |

| 2.1      | 1.7 Receiver Input Power 1      | 12    |

| 2.2 L    | ink Budget 1                    | 2     |

| 2.2.1 Radiated Power                                  | . 12 |

|-------------------------------------------------------|------|

| 2.2.2 Path Loss                                       | . 13 |

| 2.2.3 E <sub>b</sub> /N <sub>0</sub>                  | . 14 |

| 2.2.4 Tolerable Path Loss and Maximum Operating Range | . 15 |

| 2.3 Receiver Specification                            | . 17 |

| 2.3.1 Conversion Gain                                 | . 17 |

| 2.3.2 Signal-to-Noise Ratio                           | . 17 |

| 2.3.3 Noise Figure                                    | . 19 |

| 2.3.4 Linearity                                       | . 19 |

| 2.3.5 Specification Summary                           | . 21 |

| Bibliography                                          |      |

|                                                       |      |

| CHAPTER 3 PHASED-ARRAY RECEIVER ARCHITECTURE          | 5  |

|-------------------------------------------------------|----|

| 3.1 Overview of Receiver Architectures                |    |

| 3.1.1 Super Heterodyne Topology                       |    |

| 3.1.2 Direct-Conversion Topology                      |    |

| 3.1.3 Dual-Conversion Zero-IF Topology 27             | ,  |

| 3.1.4 Summary on Receiver Topology for IEEE 802.15.3c |    |

| 3.2 Phased-Array Receiver Architectures               |    |

| 3.2.1 Phased-Array Principles                         | I  |

| 3.2.2 Phase Shifting Configurations                   |    |

| 3.2.2.1 RF Phase Shifting                             | ,  |

| 3.2.2.2 LO Phase Shifting                             | i. |

| 3.2.2.3 IF Phase Shifting                             |    |

| 3.2.2.4 Digital Phase Shifting                        |    |

| 3.2.2.5 Summary on Phase Shifting Configuration       |    |

| 3.   | 2.3 Phased-Array Architectures                         |

|------|--------------------------------------------------------|

|      | 3.2.3.1 Direct-Conversion with LO Phase Shifting       |

|      | 3.2.3.1 Dual-Conversion Zero-IF with LO Phase Shifting |

| 3.3  | Proposed 4-Path Phased-Array Receiver RF Front-End     |

| 3.   | 3.1 Number of Paths                                    |

| 3.   | 3.2 System Architecture 40                             |

| 3.   | 3.3 Specification of 4-Path Phased-Array Receiver      |

| 3.   | 3.4 Specification of Building Blocks 44                |

|      | 3.3.4.1 LNA                                            |

|      | 3.3.4.2 Mixer A 45                                     |

|      | 3.3.4.3 Mixer B 46                                     |

|      | 3.3.4.4 First LO 46                                    |

|      | 3.3.4.5 Second LO                                      |

|      | 3.3.4.6 Phase Shifter                                  |

| 3.   | 3.5 Behavioral System Simulation 47                    |

| Bibl | iography 49                                            |

|      |                                                        |

| CHAPTER 4 60-GHz DIVIDE-BY-4 FREQUENCY DIVIDER51 |                                                           |    |

|--------------------------------------------------|-----------------------------------------------------------|----|

| 4.1                                              | Introduction                                              | 51 |

| 4.2                                              | Conventional Divide-by-4 ILFDs                            | 52 |

| 4.3                                              | Proposed Locking Range Enhancement with Harmonic Boosting | 55 |

| 4.4                                              | Circuit Design and Implementation                         | 58 |

| 4.5                                              | Experimental Results                                      | 60 |

| 4.5.1 Measured Sensitivity Curves                |                                                           | 61 |

| 4.5.2 Measured Phase Noise 61                    |                                                           | 61 |

| 4.5.3 Measured Output Spectrum                   |                                                           | 62 |

| 4.5.4 Measured Output Transient Waveform | 63 |

|------------------------------------------|----|

| 4.5.5 Performance Summary                | 65 |

| 4.6 Conclusion                           | 65 |

| Bibliography                             | 67 |

### 5.1 5.2 5.3 5.4 5.5 5.6

| СНАРТ | ER 6 24-GHz AND 60-GHz DUAL-BAND STANDING-WAVE VCO | 82   |

|-------|----------------------------------------------------|------|

| 6.1   | Introduction                                       | . 82 |

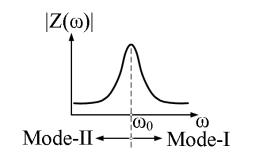

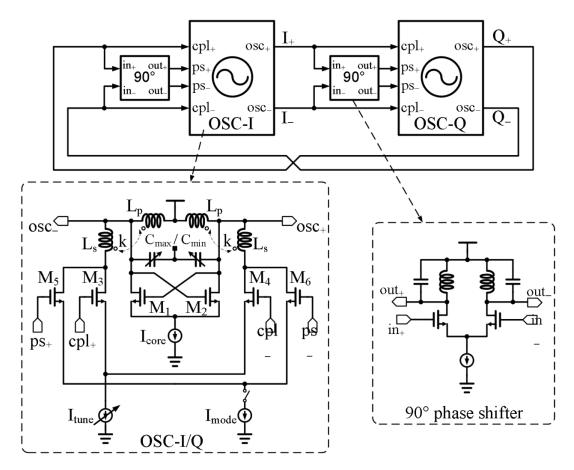

| 6.2   | Multiple-Mode Oscillation of SWO                   | . 83 |

| 6.3   | Analysis on the Stability Issue                    | . 85 |

| 6.4   | Circuit Design and Implementation                  | . 88 |

| 6.5   | Experimental Results                 | 90 |

|-------|--------------------------------------|----|

| 6.5   | 5.1 Measured Frequency Tuning Curves | 90 |

| 6.5   | 5.2 Measured Phase Noise             | 91 |

| 6.5   | 3.3 Performance Summary              | 93 |

| 6.6   | Conclusion                           | 93 |

| Bibli | ography                              | 94 |

# CHAPTER 7 LO GENERATION WITH AUTOMATIC PHASE TUNING ......95

| 7 | .1  | Introduction                                        | <del>)</del> 5 |

|---|-----|-----------------------------------------------------|----------------|

| 7 | .2  | System Architecture                                 | <del>)</del> 8 |

|   | 7.2 | 2.1 Phase Shifting Configuration                    | <del>)</del> 8 |

|   | 7.2 | 2.2 Proposed Variable Linear-Phase-Shift Chain      | )0             |

|   | 7.2 | 2.3 Proposed LO Generation System                   | )2             |

| 7 | .3  | Automatic Phase Tuning                              | )3             |

|   | 7.3 | .1 Successive-Approximation Algorithm               | )3             |

|   | 7.3 | 2.2 Port Swapping and Averaging                     | )7             |

| 7 | .4  | Circuit Design and Implementation 10                | )8             |

|   | 7.4 | .1 Phase Shifter                                    | )8             |

|   | 7.4 | .2 Injection-Locked Frequency Tripler (ILFT) 11     | 10             |

|   | 7.4 | .3 Virtual Third-Order Standing-Wave Mode Buffer 11 | 14             |

|   | 7.4 | .4 Phase Detector with Low-Pass Filter 11           | 17             |

| 7 | .5  | Experimental Results 11                             | 17             |

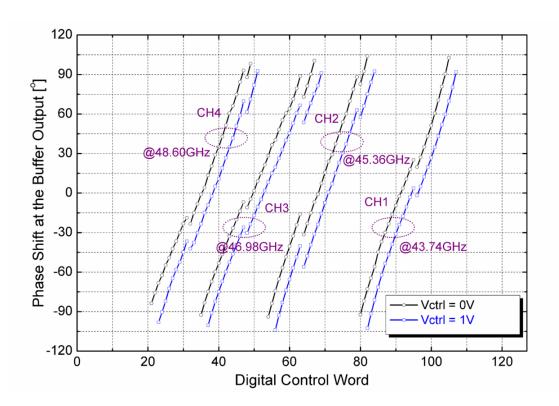

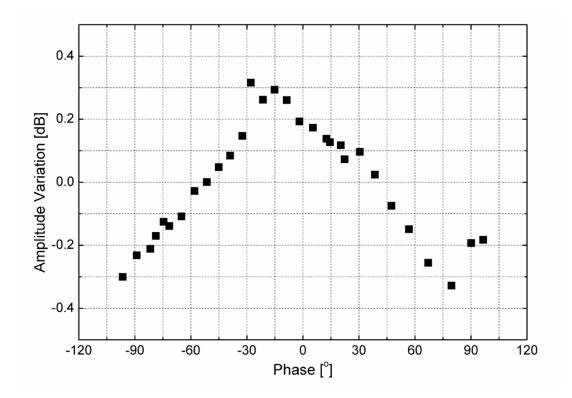

|   | 7.5 | .1 Measured Phase Shift 11                          | 18             |

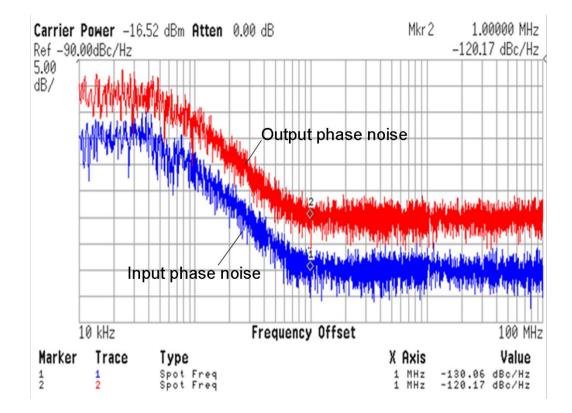

|   | 7.5 | 2.2 Measured Phase Noise                            | 20             |

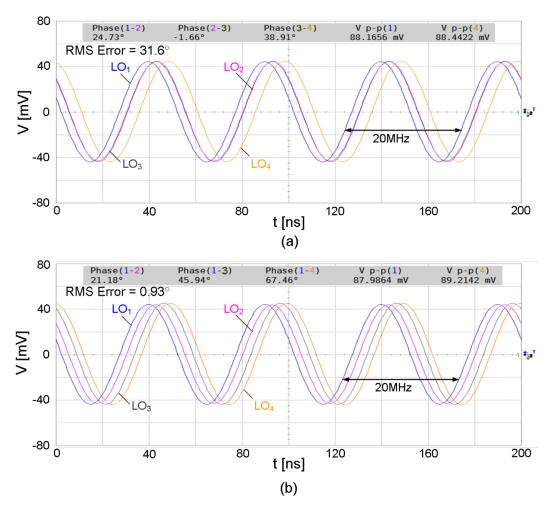

|   | 7.5 | 3.3 Measured Phase Tuning 12                        | 20             |

|   | 7.5 | .4 Mismatch Characterization                        | 21             |

| 7.5    | .5 Isolation Characterization | 123 |

|--------|-------------------------------|-----|

| 7.5    | .6 Performance Summary        | 123 |

| 7.6    | Conclusion                    | 123 |

| Biblic | Bibliography                  |     |

### CHAPTER 8 4-PATH PHASED-ARRAY RECEIVER WITH CLOSE-LOOP

| BEAN | BEAMFORMING                                                                 |  |  |

|------|-----------------------------------------------------------------------------|--|--|

| 8.1  | Introduction 129                                                            |  |  |

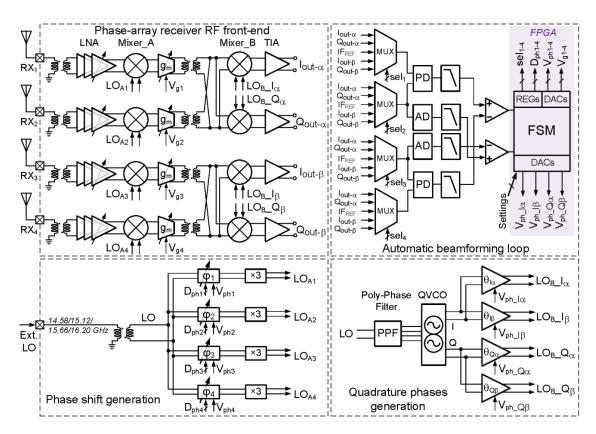

| 8.2  | Block diagram 129                                                           |  |  |

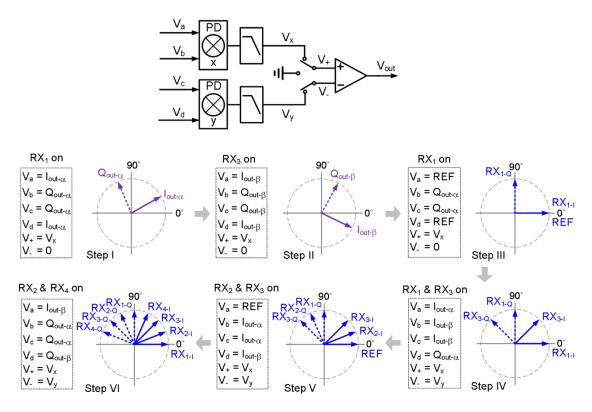

| 8.3  | Closed-Loop Beamforming 131                                                 |  |  |

| 8.4  | Proposed RF Front-End with Hybrid-Mode Mixing 133                           |  |  |

| 8    | .4.1 Circuit Design and Implementation                                      |  |  |

| 8    | .4.2 Analysis of Proposed Hybrid-Mode Architecture                          |  |  |

| 8    | .4.3 Comparison with Existing Architectures                                 |  |  |

|      | 8.4.3.1 Analysis of Voltage-Mode Mixing 137                                 |  |  |

|      | 8.4.3.2 Analysis of Current-Mode Mixing                                     |  |  |

|      | 8.4.3.3 Comparison of voltage-mode, current-mode and hybrid-mode mixing 139 |  |  |

| 8    | .4.4 Layout Floor-plan and Consideration                                    |  |  |

| 8.5  | Experimental Results 140                                                    |  |  |

| 8    | .5.1 S <sub>11</sub>                                                        |  |  |

| 8    | .5.2 Conversion Gain                                                        |  |  |

| 8    | .5.3 Input Referred 1-dB Compression Point (IP <sub>1dB</sub> ) 143         |  |  |

| 8    | .5.4 Noise Figure 144                                                       |  |  |

| 8    | .5.5 Array Pattern                                                          |  |  |

| 8    | .5.6 Statistical Result                                                     |  |  |

| 8    | .5.7 Performance Summary 148                                                |  |  |

| Bibliography | · | 149 |

|--------------|---|-----|

|              |   |     |

| CHAI | PTER 9 CONCLUSTION AND FUTURE WORK | 150   |

|------|------------------------------------|-------|

| 9.1  | Summary                            | . 150 |

| 9.2  | Contribution of the Dissertation   | . 152 |

| 9.3  | Potential Future Work              | . 153 |

|      |                                    |       |

| APPENDIX-I LIST OF PUBLICATIONS155 |

|------------------------------------|

|------------------------------------|

## **LIST OF FIGURES**

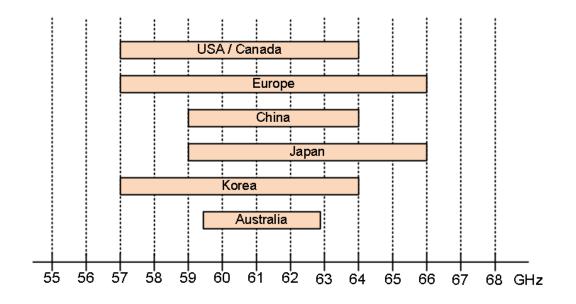

| Fig. 1.1 Bandwidth allocation of 60-GHz unlicensed band                           | 1 |

|-----------------------------------------------------------------------------------|---|

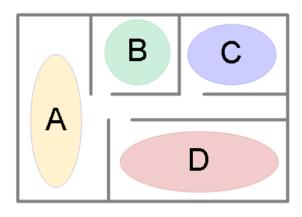

| Fig. 1.2 Secure communication of multiple wireless personal area networks (WPANs) | 2 |

| Fig. 1.3 60-GHz wireless applications                                             | 2 |

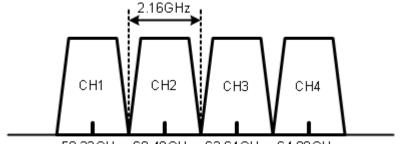

| Fig. 2.1 Frequency allocation of IEEE 802.15.3c                    | 9  |

|--------------------------------------------------------------------|----|

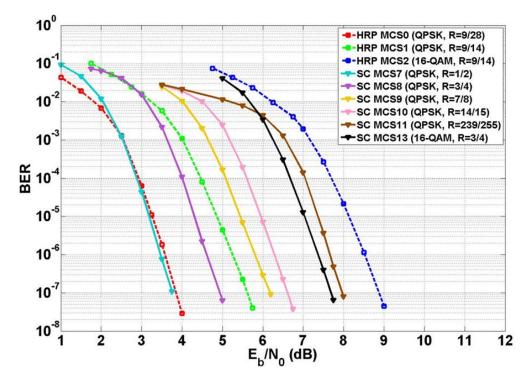

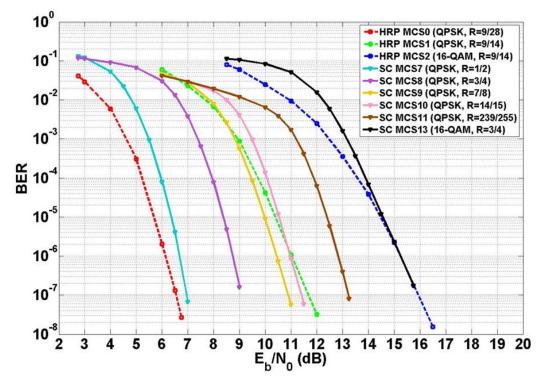

| Fig. 2.2 BER performance of SC and OFDM PHY for CM1.3 (LOS)        | 14 |

| Fig. 2.3 BER performance of SC and OFDM PHY for CM2.3 (NLOS)       | 15 |

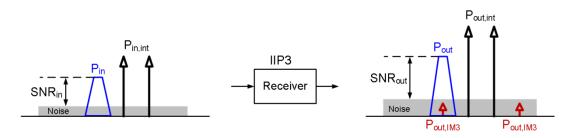

| Fig. 2.4 Intermodulation product generated by interference signals | 20 |

| Fig. 3.1 A super heterodyne receiver                                               | 6 |

|------------------------------------------------------------------------------------|---|

| Fig. 3. 2 A direct-conversion receiver                                             | 6 |

| Fig. 3.3 A dual-conversion zero-IF receiver                                        | 8 |

| Fig. 3.4 A simple receiver array                                                   | 9 |

| Fig. 3.5 A phased-array receiver                                                   | 1 |

| Fig. 3.6 RF phase shifting configuration                                           | 2 |

| Fig. 3.7 LO phase shifting configuration                                           | 4 |

| Fig. 3.8 IF phase shifting configuration                                           | 4 |

| Fig. 3.9 Baseband phase shifting configuration                                     | 5 |

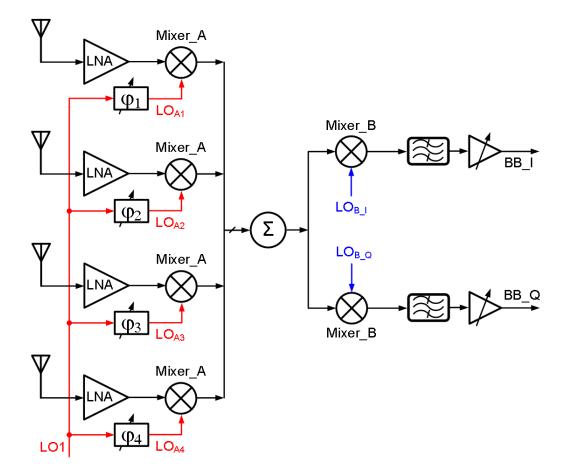

| Fig. 3.10 4-path phased-array with direct-conversion and LO phase shifting         | 7 |

| Fig. 3.11 4-path phased-array with dual-conversion zero-IF and LO phase shifting 3 | 8 |

| Fig. 3.12 Maximum operation range for different path number                        | 9 |

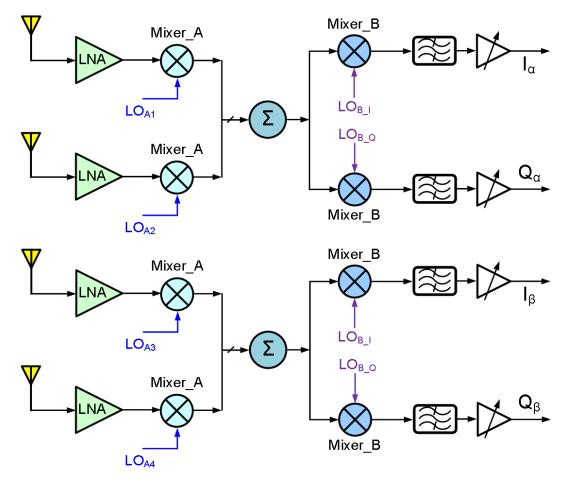

| Fig. | 3.13 Proposed phased-array receiver RF front-end | 41 |

|------|--------------------------------------------------|----|

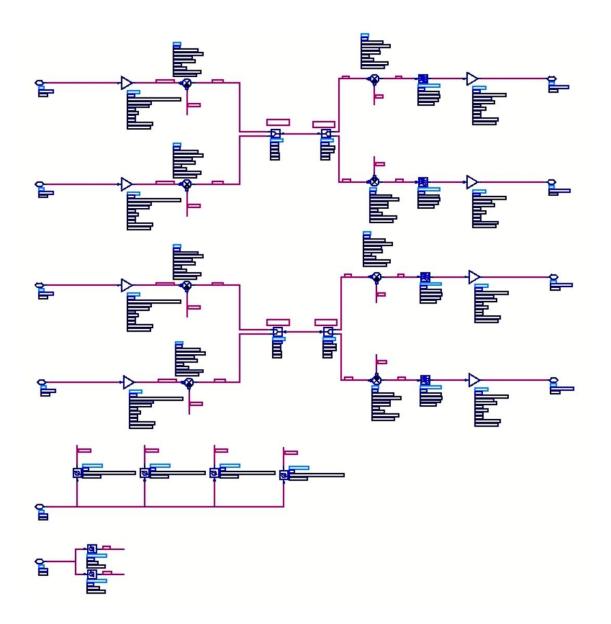

| Fig. | 3.14 System Behavioral Simulation in ADS         | 48 |

| Fig. 4.1 Conventional divide-by-4 ILFD                                                | . 52 |

|---------------------------------------------------------------------------------------|------|

| Fig. 4.2 Behavioral model of conventional divide-by-4 ILFD                            | . 53 |

| Fig. 4.3 Phasor diagram of conventional divide-by-4 ILFD                              | . 54 |

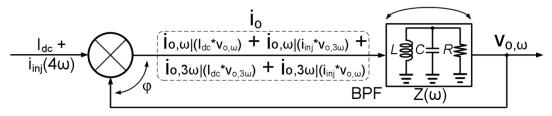

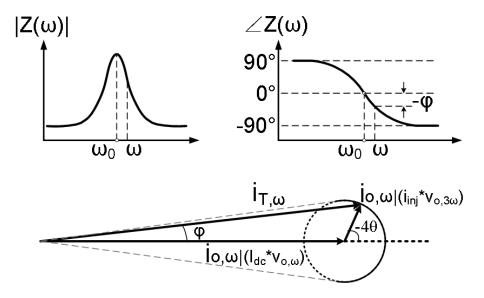

| Fig. 4.4 Behavioral model of proposed locking range enhancement                       | . 55 |

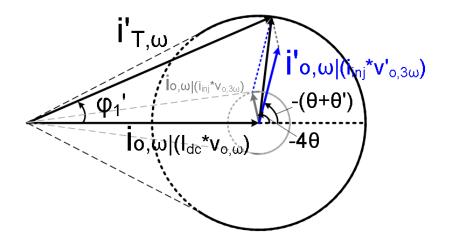

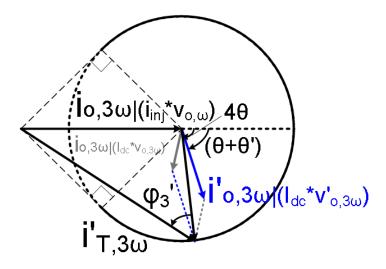

| Fig. 4.5 Phasor diagram of proposed locking range enhancement at $\omega$             | . 56 |

| Fig. 4.6 Phasor diagram of proposed locking range enhancement at $3\omega$            | . 57 |

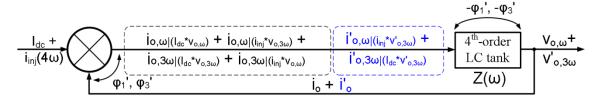

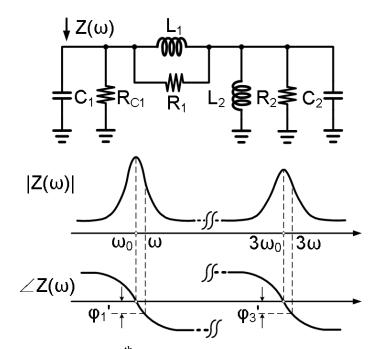

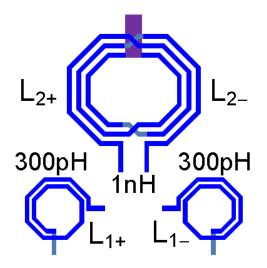

| Fig. 4.7 Proposed 4 <sup>th</sup> -order LC tank and its impedance plots              | . 58 |

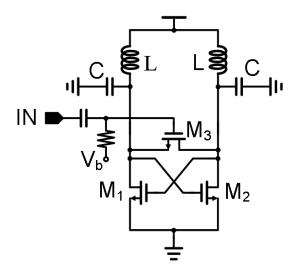

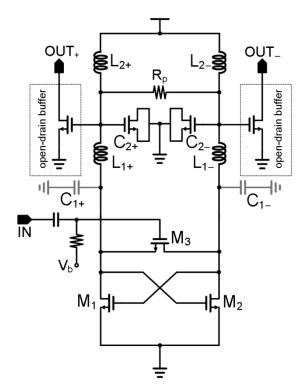

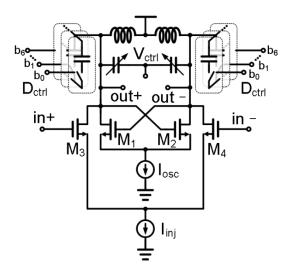

| Fig. 4.8 Schematic of the proposed divide-by-4 ILFD                                   | . 59 |

| Fig. 4.9 Layout of the inductors                                                      | . 59 |

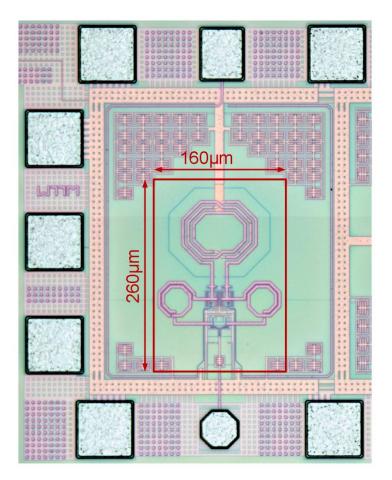

| Fig. 4.10 Chip micrograph of the proposed divide-by-4 ILFD                            | . 60 |

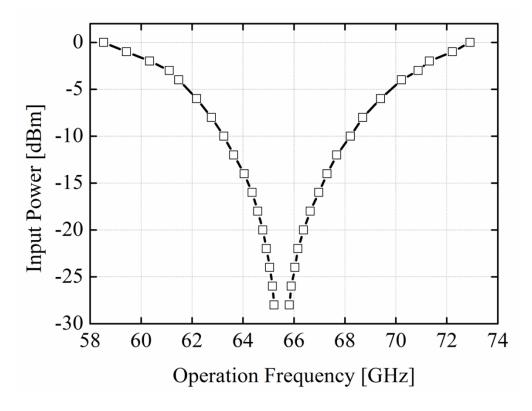

| Fig. 4.11 Measured sensitivity curves                                                 | . 61 |

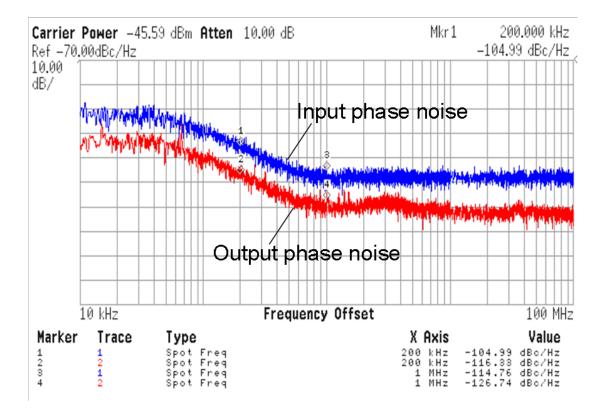

| Fig. 4.12 Measured phase noise at the proposed ILFD's input and output                | . 62 |

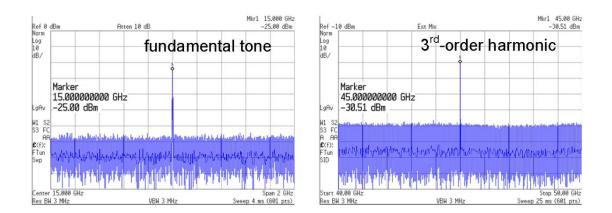

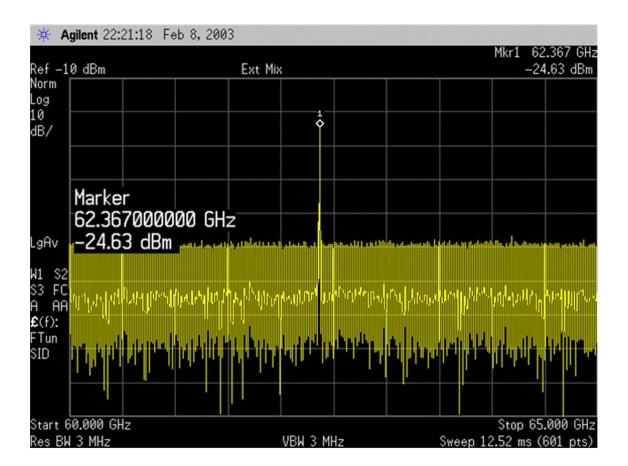

| Fig. 4.13 Measured output spectrum                                                    | . 63 |

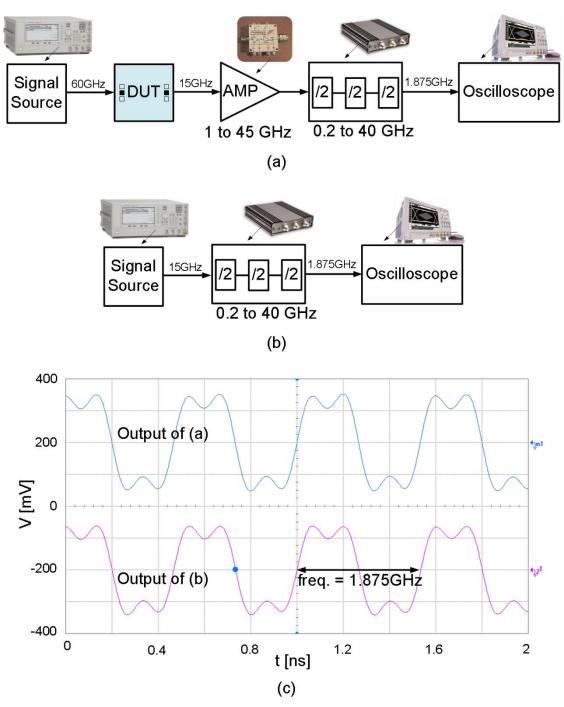

| Fig. 4.14 Setups of a divider chain driven by (a) proposed divider and (b) sinusoidal |      |

| source, and (c) their output transient waveforms.                                     | . 64 |

| Fig. 5.1 Conventional magnetic tuning                         | 69 |

|---------------------------------------------------------------|----|

| Fig. 5.2 Proposed Enhanced magnetic tuning                    | 70 |

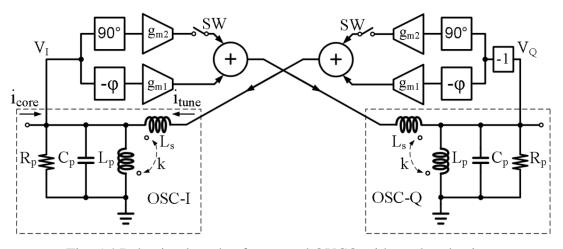

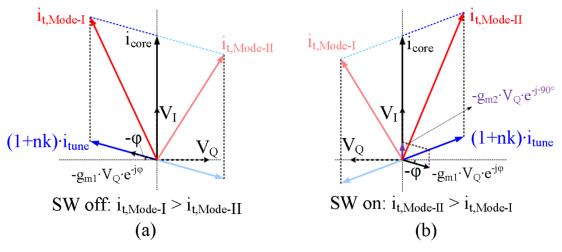

| Fig. 5.3 Two operation modes of QVCO                          | 71 |

| Fig. 5.4 Behavioral mode of proposed QVCO with mode selection | 72 |

| Fig. 5.5 Phasor diagram of Mode I and mode II operations      | 73 |

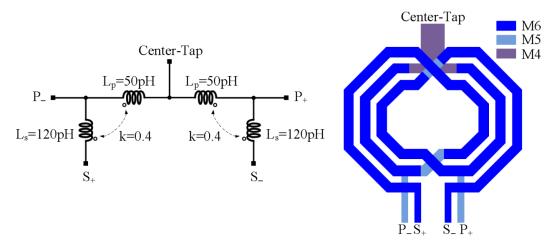

| Fig. 5.6 Schematic of QVCO with bimodal enhanced magnetic tuning | . 74 |

|------------------------------------------------------------------|------|

| Fig. 5.7 Layout of transformer                                   | . 74 |

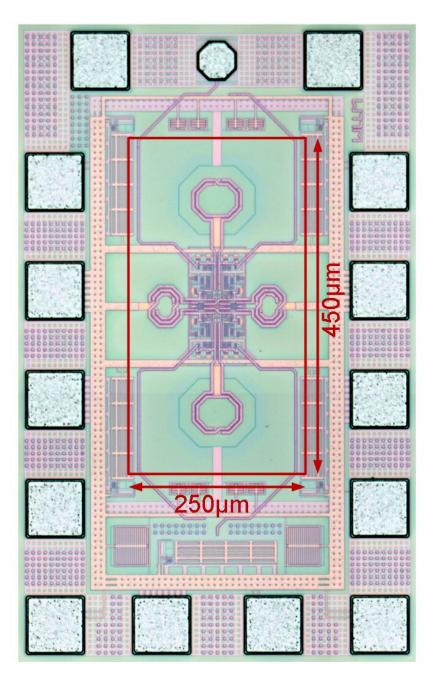

| Fig. 5.8 Chip micrograph of the proposed QVCO                    | . 75 |

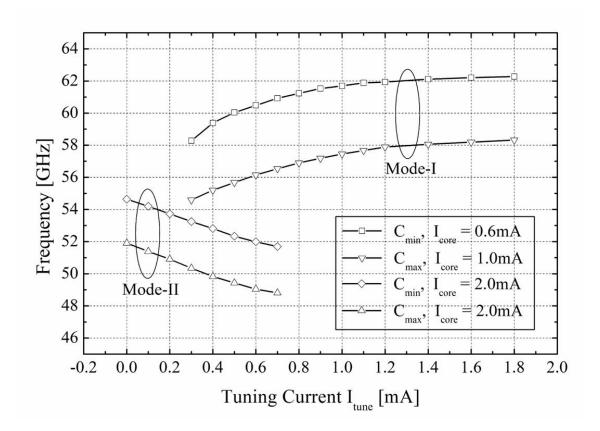

| Fig. 5.9 Measured frequency tuning curves                        | . 76 |

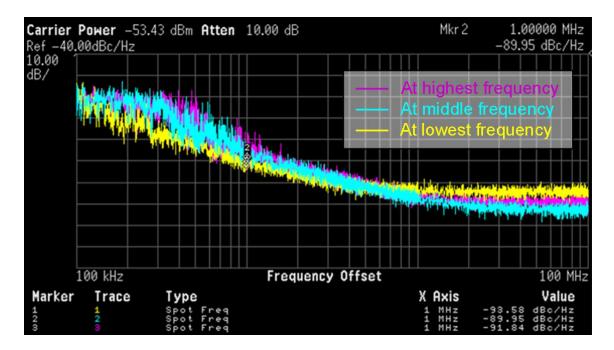

| Fig. 5.10 Measured phase noise performance                       | . 77 |

| Fig. 5. 11 Measured output spectrum                              | . 78 |

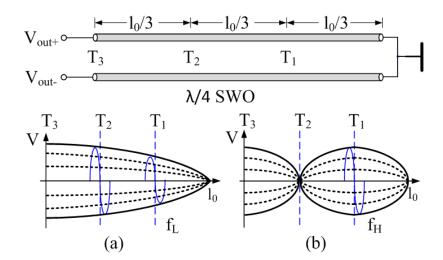

| Fig. 6.1 Voltage amplitudes of a $\lambda/4$ SWO operating in (a) the fundamental mode and | . (b) |

|--------------------------------------------------------------------------------------------|-------|

| the third-order mode                                                                       | 84    |

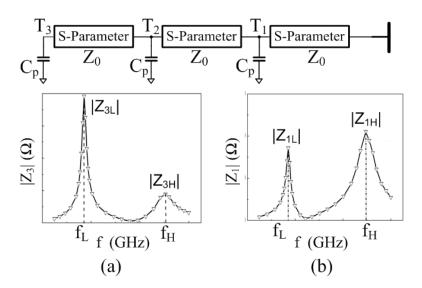

| Fig. 6.2 Impedance seen at Nodes (a) $T_3$ and (b) $T_1$                                   | 85    |

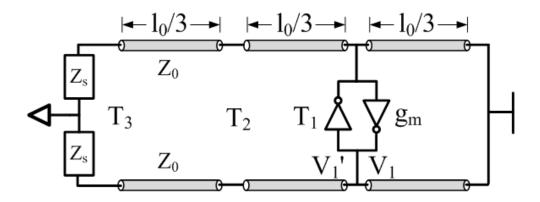

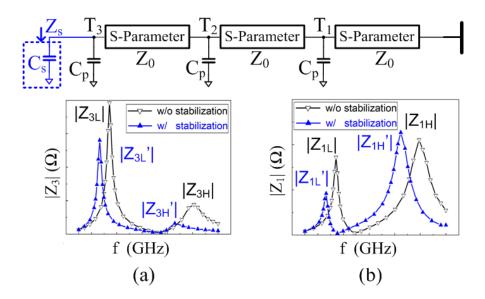

| Fig. 6.3 Simplified model of SWO operating in the high-band mode                           | 86    |

| Fig. 6.4 Impedance with and without stabilization technique seen at Nodes (a) $T_3$ and    | l (b) |

| T <sub>1</sub>                                                                             | 87    |

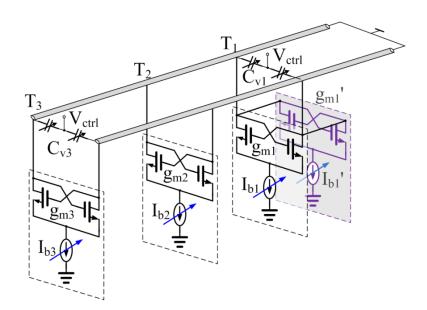

| Fig. 6.5 Proposed dual-band standing-wave VCO                                              | 89    |

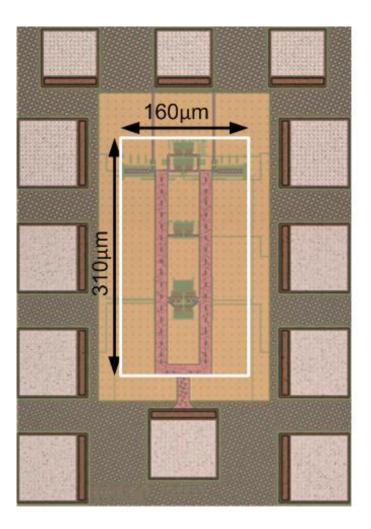

| Fig. 6.6 Chip photograph of proposed dual-band VCO                                         | 90    |

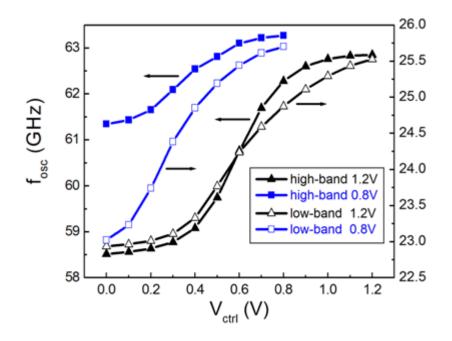

| Fig. 6.7 Measured frequency tuning curves with 0.8V and 1.2V supply voltages               | 91    |

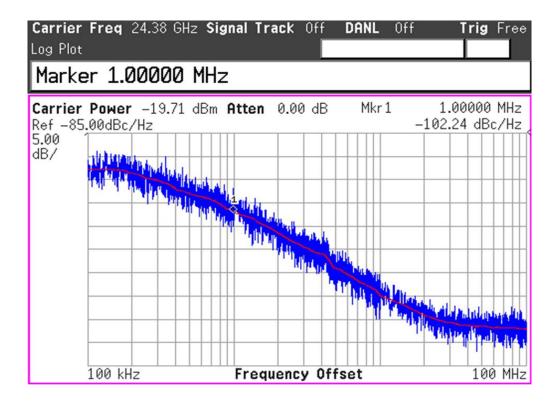

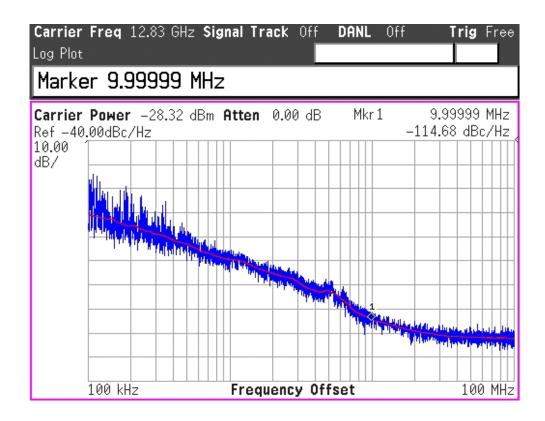

| Fig. 6.8 Measured phase noise in low-band mode at 24GHz                                    | 92    |

| Fig. 6.9 Measured phase noise in high-band mode at 60GHz                                   | 92    |

| Fig. 7.1 Phased-array receiver architecture with LO-path phase shifting                  |

|------------------------------------------------------------------------------------------|

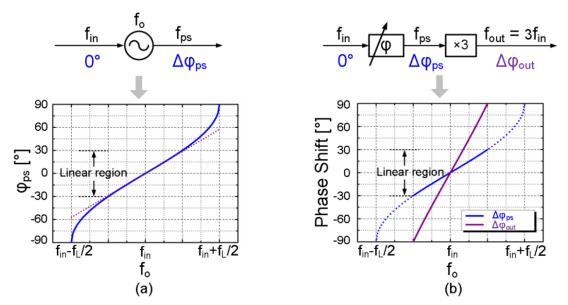

| Fig. 7.2 (a) Injection-locked oscillator based phase shifter, (b) Proposed linear-phase- |

| shift generation chain 101                                                               |

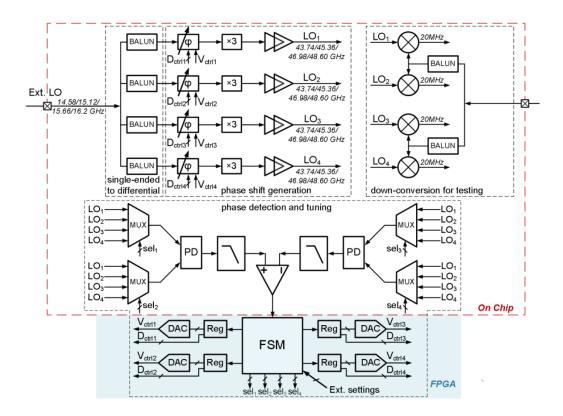

| Fig. 7.3 Block diagram of proposed LO generation scheme with automatic phase tuning      |

|                                                                                          |

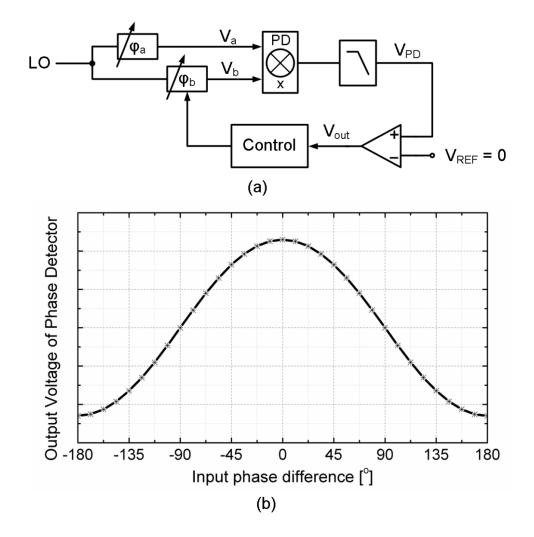

| Fig. 7.4 I/Q calibration: (a) phase detection and tuning loop, (b) input/output        |

|----------------------------------------------------------------------------------------|

| characteristic of phase detector                                                       |

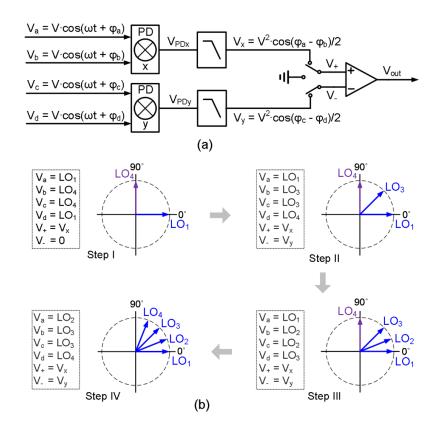

| Fig. 7.5 Proposed successive-approximation algorithm: (a) block diagram, (b) automatic |

| phase tuning of $\Delta 22.5^{\circ}$                                                  |

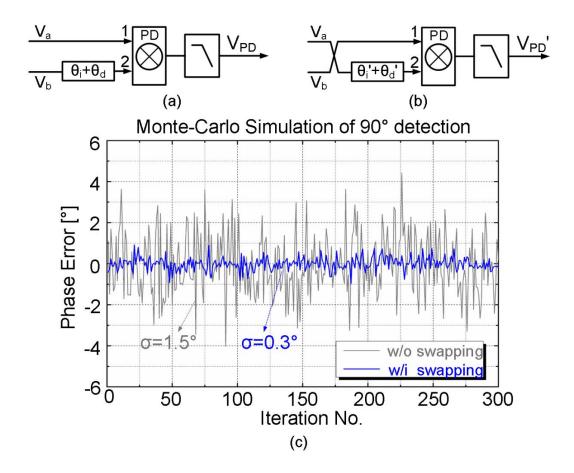

| Fig. 7.6 Proposed port swapping and averaging: (a) input sequence without swapping,    |

| (b) input sequence with swapping, (c) Monte-Carlo simulation results 108               |

| Fig. 7.7 Phase shifter based on injection-locked oscillator 110                        |

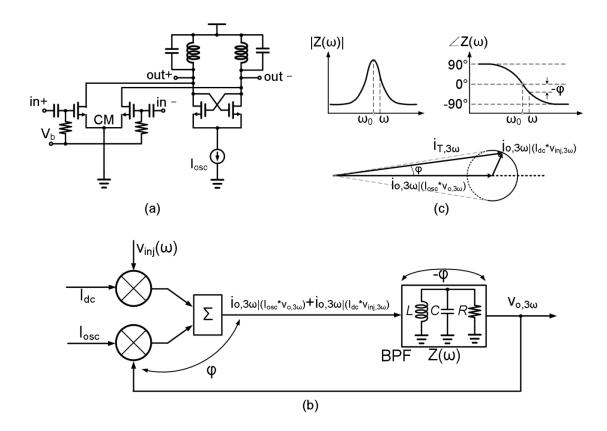

| Fig. 7.8 Conventional ILFT: (a) schematic, (b) behavioral model, (c) phasor diagram111 |

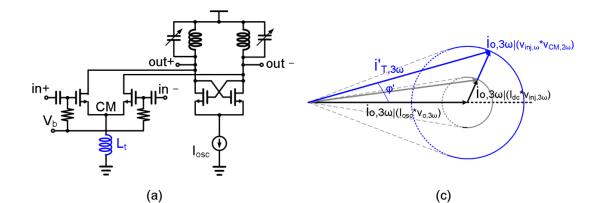

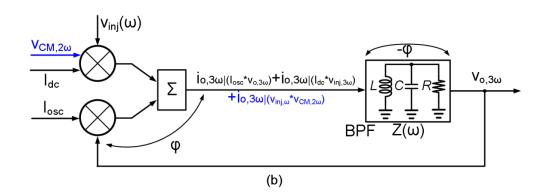

| Fig. 7.9 Proposed ILFT: (a) schematic, (b) behavioral model, (c) phasor diagram 113    |

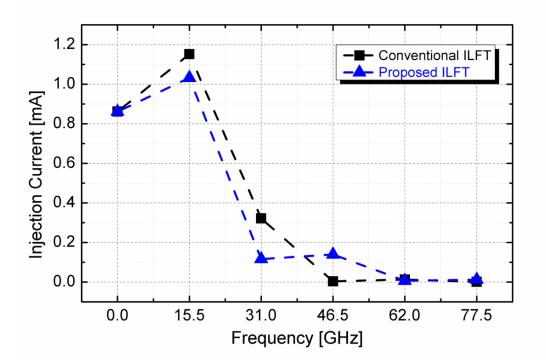

| Fig. 7.10 Injection Current of (a) Conventional ILFT, (b) Proposed ILFT 114            |

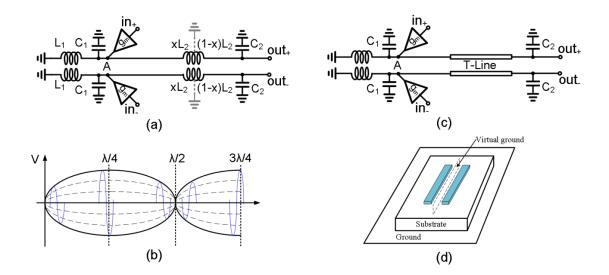

| Fig. 7.11 Proposed standing-wave mode buffer: (a) Behavioral model, (b) Standing       |

| wave, (c) Implementation, (d) Transmission line                                        |

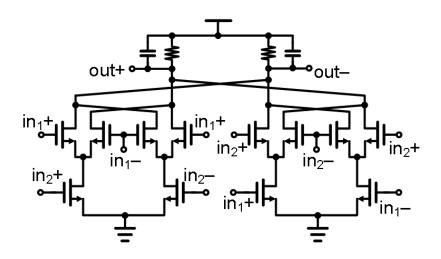

| Fig. 7.12 Highly symmetric phase detector with RC low-pass filter 117                  |

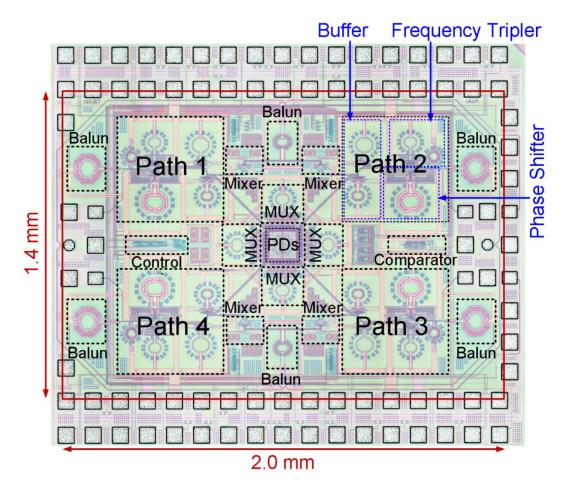

| Fig. 7.13 Chip micrograph 118                                                          |

| Fig. 7.14 Phase tuning curves 119                                                      |

| Fig. 7.15 Amplitude variations 119                                                     |

| Fig. 7.16 Measured input and output phase noise of linear-phase-shift chain 120        |

| Fig. 7.17 Measured transient waveforms: (a) before tuning, (b) after tuning 121        |

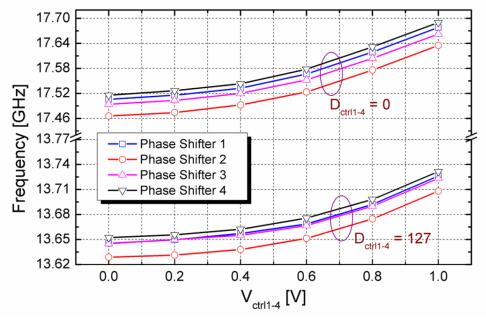

| Fig. 7.18 Measured frequency tuning curves of phase shifters to characterize           |

| mismatches 122                                                                         |

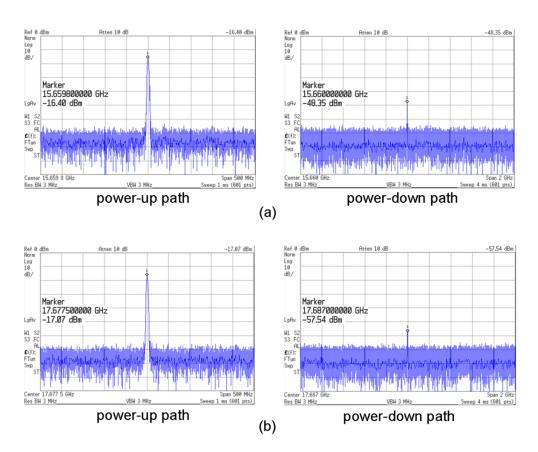

| Fig. 7.19 Measured spectrum of power-up path and its neighboring power-down path at    |

| (a) 15.66GHz and (b) 17.68GHz                                                          |

Fig. 8.1 Block diagram of proposed 4-path phased-array receiver system ...... 130

| Fig. 8.2 Proposed closed-loop beamforming mainly based on successive approaching     |

|--------------------------------------------------------------------------------------|

| algorithm                                                                            |

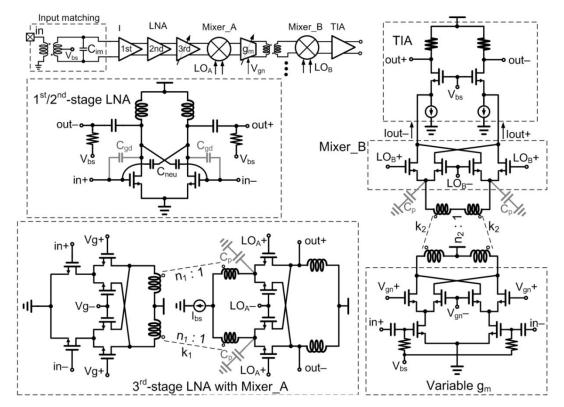

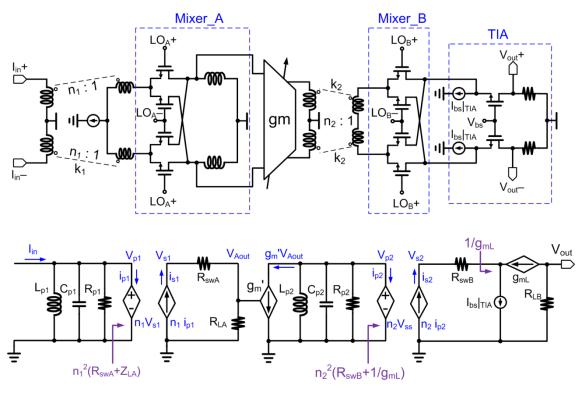

| Fig. 8.3 Schematic of proposed hybrid-mode RF front-end, including 3-stage LNA,      |

| Mixer_A, variable gm, Mixer_B and TIA 134                                            |

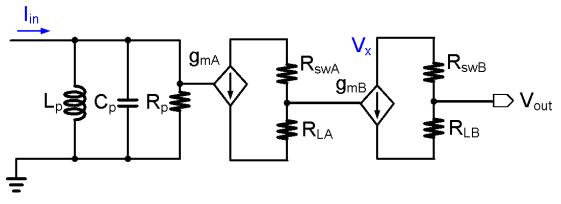

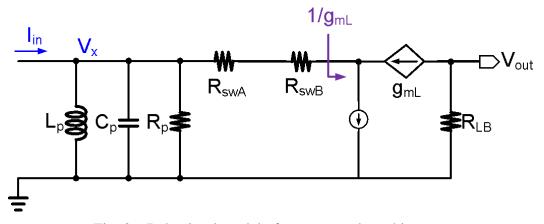

| Fig. 8.4 Analysis of proposed RF front-end with transformer based hybrid-mode mixing |

|                                                                                      |

| Fig. 8.5 Behavioral model of voltage-mode architecture 137                           |

| Fig. 8.6 Behavioral model of current-mode architecture                               |

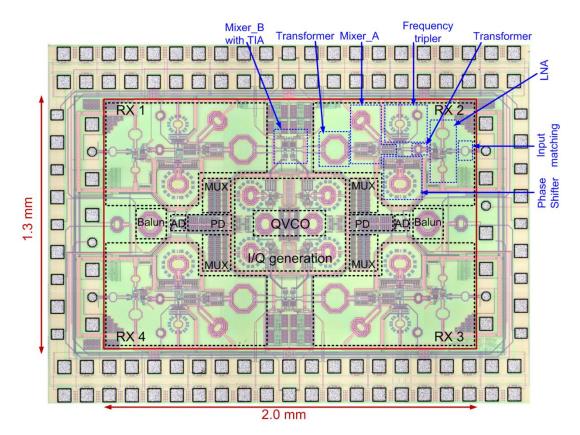

| Fig. 8.7 Layout of proposed 4-path phased-array receiver                             |

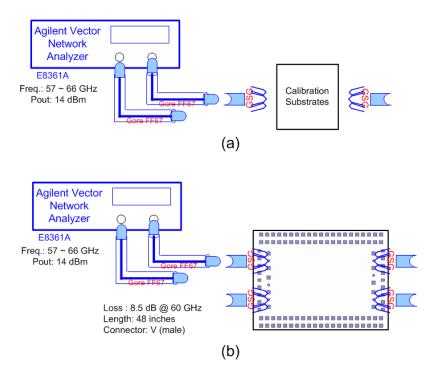

| Fig. 8.8 Setup for S11 measurement: (a) calibration, (b) measurement                 |

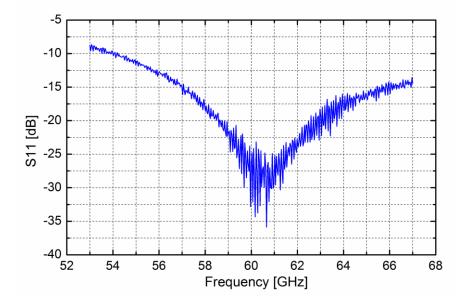

| Fig. 8.9 Measured S <sub>11</sub> 141                                                |

| Fig. 8.10 Setup for conversion gain measurement 142                                  |

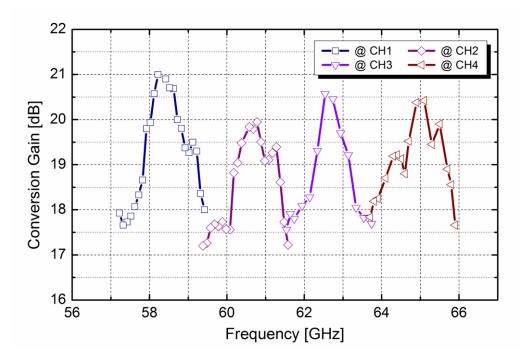

| Fig. 8.11 Measured conversion gain 142                                               |

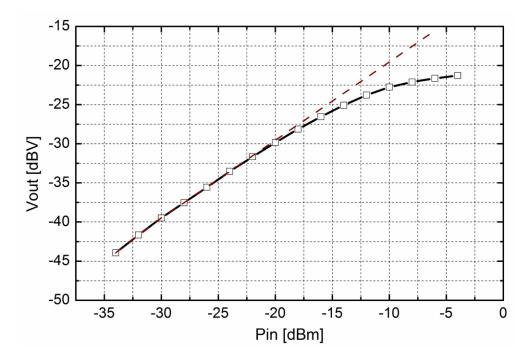

| Fig. 8.12 Measured 1-dB compression point 143                                        |

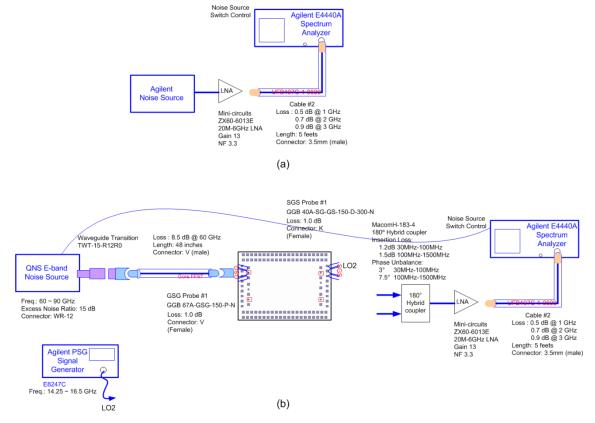

| Fig. 8.13 Setup for noise figure measurement: (a) calibration, (b) measurement 144   |

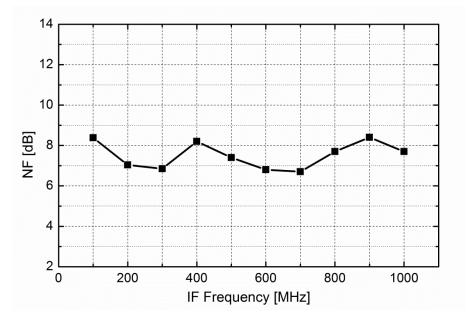

| Fig. 8.14 Measured noise figure 144                                                  |

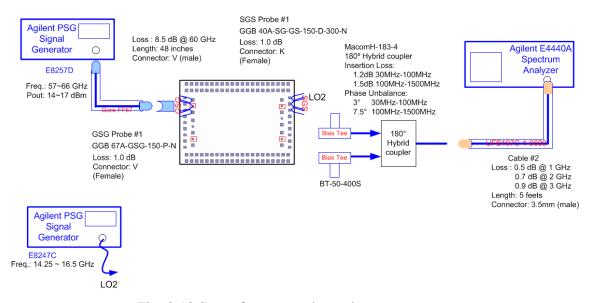

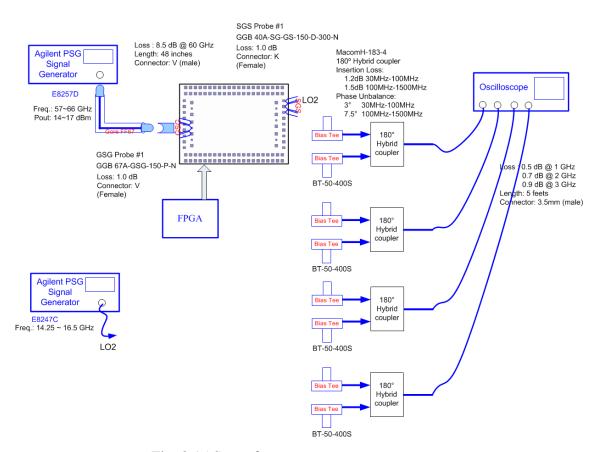

| Fig. 8.15 Setup for array pattern measurement 145                                    |

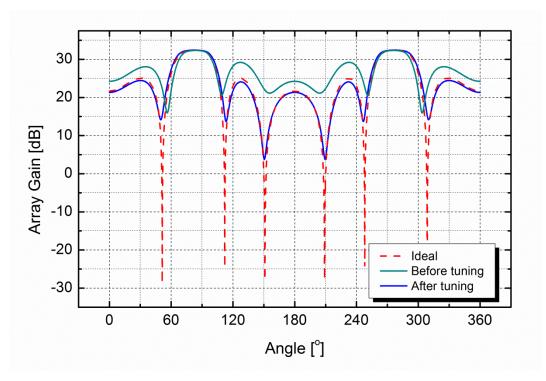

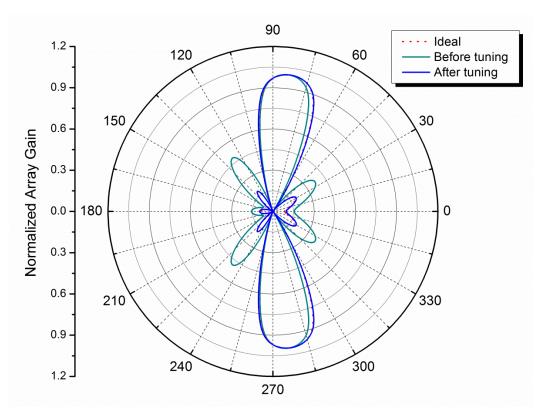

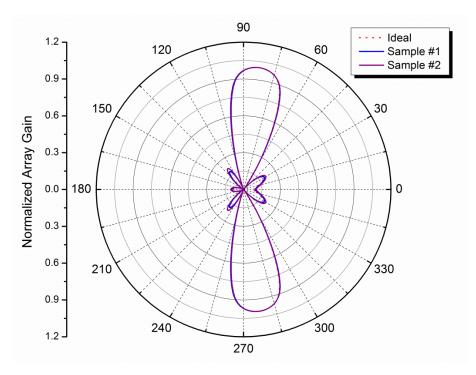

| Fig. 8.16 Synthesized array pattern 146                                              |

| Fig. 8.17 Polar plot of synthesized array pattern146                                 |

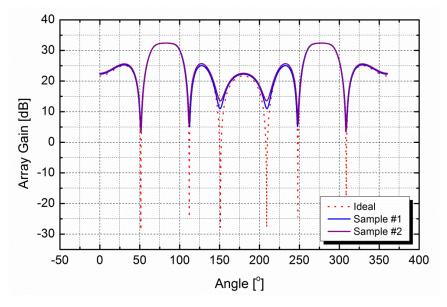

| Fig. 8.18 Synthesized array patterns of two samples147                               |

| Fig. 8.19 Polar plot of synthesized array patterns of two samples                    |

## LIST OF TABLES

| Table 2.1 RF channelization of IEEE 802.15.3c                         | . 9 |

|-----------------------------------------------------------------------|-----|

| Table 2.2 Transmit power limit in different regions                   | 10  |

| Table 2.3 Date rates for different MCS classes in single carrier mode | 11  |

| Table 2.4 EVM for MCS classes in single carrier mode                  | 11  |

| Table 2.5 Receiver sensitivity for each MCS in single carrier mode    | 13  |

| Table 2.6 Link budget for single carrier mode of IEEE 802.15.3c       | 16  |

| Table 2.7 Specification of receiver RF font-end                       | 22  |

| Table 3.1 Operation range for different path number         | . 39 |

|-------------------------------------------------------------|------|

| Table 3.2 LO frequencies for different frequency ratios     | . 42 |

| Table 3.3 Specification of 4-path phased-array receiver     | . 43 |

| Table 3.4 Specification of LNA                              | . 45 |

| Table 3.5 Specification of Mixer A                          | . 45 |

| Table 3.6 Specification of Mixer B                          | . 46 |

| Table 3.7 Specification of the first LO (LO <sub>A</sub> )  | . 46 |

| Table 3.8 Specification of the second LO (LO <sub>B</sub> ) | . 47 |

| Table 3.9 Specification of the phase shifter                | . 47 |

Table 4.1 Performance summary and comparison of mm-Wave high-division-ratio

dividers

65

| Table 5.1 Performance summary | and c | comparison | of mm | -Wave | <b>QVCOs</b> |  |

|-------------------------------|-------|------------|-------|-------|--------------|--|

|-------------------------------|-------|------------|-------|-------|--------------|--|

| Table 6.1 Performance summary ar | nd comparison |

|----------------------------------|---------------|

|----------------------------------|---------------|

| Table 7. 1 Measured performance summary and comparison with other LO generation |  |

|---------------------------------------------------------------------------------|--|

| system for phased-arrays 124                                                    |  |

| Table 8.1 Performance summar | y and comparison of 60-GHz receiver | 148 |

|------------------------------|-------------------------------------|-----|

|                              |                                     |     |

### A 4-Path 60GHz CMOS Phased-Array Receiver

by

#### **WU Liang**

Department of Electronic and Computer Engineering The Hong Kong University of Science and Technology

### Abstract

The 60-GHz worldwide unlicensed band provides up to 9-GHz bandwidth and thus enables Gb/s-data-rate point-to-point communication links and high-definition video transfer. However, implementations of circuits and systems at this frequency range are still quite challenging. This dissertation is dedicated to the design and demonstration of a high-performance 4-path 60-GHz phased-array receiver front-end (RFE) in CMOS technology with novel ideas at both system architecture and circuit implementation.

At the circuit level, several novel design techniques for the key building blocks were demonstrated. First, a 24-GHz and 60-GHz dual-band standing-wave VCO with mode-switching technique was designed in 0.13 µm CMOS process. Second, a bimodal transformer-based enhanced magnetic tuning technique was proposed to implement a quadrature VCO (QVCO) in 65nm CMOS process with an ultra-wide frequency tuning range from 48.8 GHz to 62.3 GHz (corresponding to 24 % tuning range at 60GHz) and figure-of-merit (FoM) of 181 to 184 dBc. Third, to operate the QVCO in a phased-lock loop (PLL), a harmonic-boosting technique with 4<sup>th</sup>-order LC tank was proposed to achieve a divide-by-4 injection-locked frequency divider with state-of-the-art frequency

locking range (LR) from 58.5 GHz to 72.9 GHz (21.9 % at 60GHz) and figure-of-merit (FoM) of 6.5 GHz/mW.

Furthermore, an LO generation scheme was proposed to generate LO signals with required phase shifts for a 4-path phased-array receiver. Circuit techniques include highly linear phase shifters, wide-locking-range frequency tripler, and successive-approximation phase tuning algorithm. Implemented in 65nm CMOS, the LO generation measures linear phase range larger than -90 ° ~ 90 °, amplitude variation less than  $\pm 0.35$ dB, phase resolution of 22.5 °, and phase error smaller than 1.5 °.

Finally, at the system level, a 4-path phased-array receiver front-end system was designed and integrated in a 65-nm CMOS process. With proposed hybrid-mode mixing scheme, the system performance (in terms of linearity, noise figure, gain, power consumption, and chip area) is significantly improved as compared to existing solutions. In addition, modified successive algorithm is proposed for automatic phase calibration and gain equalization to achieve beam-forming with maximum peak-signal-to-noise ratio of more than 28dB.

### **Chapter 1**

## Introduction

#### 1.1 Background

Over the last decade, wireless communication at several-GHz frequency bands has experienced explosive growth that the available frequency spectrum becomes very limited. Recently, a great deal of interest from academia, industry and standardization bodies is being attracted to higher frequency bands even at millimeter-wave (mm-Wave) region where wide channel bandwidth can be provided to enable high data rate communications. The 60-GHz band has some advantages compared to other unlicensed bands. The available bandwidth is up to 9 GHz and has been allocated in most countries, as summarized in Fig. 1.1. Thanks to the large path loss at mm-Wave frequency, not

Fig. 1.1 Bandwidth allocation of 60-GHz unlicensed band

only the transmission power level is less restricted [1], but also secure communication can be obtained, which is important when there are multiple networks close to each other, as show in Fig. 1.2. The great potential in terms of capacity and flexibility makes it fascinated for gigabit wireless applications. Particularly, IEEE standard 802.15.3c is on the way and many new applications are enabled [2], including short-range wireless links with data rate up to 5 Gb/s and high-definition video transmission [3], as shown in Fig. 1.3.

Fig. 1.2 Secure communication of multiple wireless personal area networks (WPANs)

Short-range wireless links

High-definition video transfer

Fig. 1.3 60-GHz wireless applications

However, mm-Wave communications face a number of important challenges spanning a broader range of topics that must be solved, including wave propagation, channel model, circuit design and antenna implementation. From the circuit point of view, this ultra-high frequency obviously requires high-speed active devices. Besides, the large path loss and atmosphere absorption demand transmitter with high output power and receiver with good sensitivity. Conventionally, only compound semiconductor technologies, such as gallium arsenide (GaAs) and indium phosphide (InP), can be utilized to fulfill those requirements. But their high cost is an obstacle for consumer market spreading of mm-Wave applications.

With recent advancement in nanometer scale silicon-based technology, the transition frequency ( $f_T$ ) of transistor exceeds 100 GHz, making the implementation of mm-Wave circuits in CMOS possible. Compared with compound semiconductor, CMOS solution is cheaper and offers the opportunity to realize 60-GHz system-on-chip (SoC) with RF front-end, analog baseband, digital signal processing, calibration and self-testing integrated. Thanks to the small wavelength at mm-Wave frequencies, the size of the antennas is small and can be in package [4] or on chip [5], which reducing or even eliminating the electrical interface at mm-Wave frequencies.

#### **1.2 Research Motivation**

Despite various advantages of CMOS technology, there are some challenges to fully integrate mm-Wave system, from a single device to a circuit and finally to a system. The low breakdown voltage of transistors resulting from the scaling process and the shrinking of the depletion regions limits the achievable output power of power amplifier. Silicon substrate is conductive for bulk processes and thus energy loss due to magnetically induced eddy currents is inevitably large. At higher frequency, the parasitics are more dominant, so the models of both active devices and passive components become less inaccurate, especially in the presence of process variations and environmental changes. Flicker noise increases as channel length being scaled down. From the aspect of circuit design, the performance of some critical building blocks especially in RF front-end, such as low-noise amplifier (LNA), mixer, power amplifier (PA), local oscillator (LO), frequency divider would be degraded if simply moving existing solutions at several GHz to 60-GHz. Therefore, new circuit techniques are urgently mandated. For the system, the transmitted power and receiver sensitivity need to be improved to fulfill the requirements of Gb/s communications.

One promising solution in system level is spatial power combing provided by phased-array. On transmitter side, phased-array combines power from multiple transmitters and thus can help to achieve sufficient output power for the system. On receiver side, phased-array can improve the signal noise ratio (SNR) by 10logN compared with single receiver theoretically, where N is the element number. In addition, the phase-array system is able to perform beam steering and thus features spatial selectivity to improve spectral efficiency by suppressing unwanted signals, which come from nearby devices and might be very strong.

4

#### **1.3** Objective of the Dissertation

In this dissertation, the objection is on the design and implementation of a 4-path 60-GHz phased-array receiver front-end in CMOS technology. The dissertation is organized as follows:

Chapter 2 investigates the system specification of IEEE 802.15.3c standard. Based on different channel models, the link budget is calculated for both basic transceiver and phased-array transceiver.

Chapter 3 discusses system architectures, including both basic receiver and phasedarray receiver, in order to make the performance trade-offs well understood. Based on dual-conversion zero-IF architecture, the detailed specifications of each building block are derived.

Chapter 4 presents a 60-GHz LC-type injection-locked frequency divider-by-4. Based on theoretical analysis, third-order harmonic boosting technique implemented with a 4<sup>th</sup>-order LC tank is proposed to significantly enhance the injection efficiency and thus the locking range.

Chapter 5 presents a 60-GHz QVCO with ultra-wide frequency tuning range. After the investigation and theoretical analysis of existing frequency tunings, a novel tuning mechanism named bimodal enhanced magnetic tuning is proposed and experimentally validated.

Chapter 6 discusses a 24-GHz and 60-GHz dual-band VCO based on standingwave oscillator (SWO), which is a potential solution to generate LO signals for multiple-band mm-Wave transceiver. The associated circuit implementation and stability analysis issues are addressed and validated.

Chapter 7 focuses on the LO generation with phase shift for targeted 60-GHz phased-array receiver. Linear phase shift is achieved with proposed injection-locked phase shifter cascaded with injection-locked frequency tripler. A novel successive-approximation algorithm is proposed to automatically detect and tune the LO phase difference specified by the system.

Chapter 8 presents the whole integrated 4-path phased-array receiver system. With the theoretical investigation on existing voltage-mode and current-mode RF front-ends, a new hybrid-mode mixing topology is proposed, designed, analyzed and experimentally verified. Another key feature, automatic beamforming is realized by sequentially equalizing the gain and tuning the phase with a close-loop.

Chapter 9 summarizes the research work and the contributions of the dissertation.

#### **Bibliography**

[1] S.-K. Yong, P. Xia and A. Valdes-Garcia, "60 GHz Technology for Gbps WLAN and WPAN," *John Wiley & Sons Ltd*, 2011.

[2] IEEE Standard Part 15.3: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for High Rate Wireless Personal Area Networks (WPANs), 2009.

[3] A. M. Niknejad and H. Hashemi (editors), "mm-Wave Silicon Technology: 60 GHz and Beyond", *Springer*, 2008.

[4] A. Natarajan, S. K. Reynolds, T. Ming-Da, S. T. Nicolson, J. H. C. Zhan, K. Dong Gun, L. Duixian, Y. L. O. Huang, A. Valdes-Garcia and B. A. Floyd, "A Fully-Integrated 16-Element Phased-Array Receiver in SiGe BiCMOS for 60-GHz Communications," *IEEE J. Solid-State Circuits*, vol. 46, pp. 1059–1075, May. 2011.

[5] A. Babakhani, G. Xiang, A. Komijani, A. Natarajan and A. Hajimiri, "A 77-GHz Phased-Array Transceiver With On-Chip Antennas in Silicon: Receiver and Antennas", *IEEE J. Solid-State Circuits*, vol. 41, no.12, pp. 2795-2806, 2006.

### Chapter 2

## **System Specification**

#### 2.1 Specification of IEEE 802.15.3c [1]

#### 2.1.1 Overview

The IEEE 802.15.3c standard is targeted at supporting 60-GHz wireless communications with data rate of gigabit per second (Gb/s) over a few meters. The specification defines a total of three physical layers (PHYs), namely single carrier (SC) PHY, high speed interface (HSI) orthogonal frequency division multiplexing (OFDM) PHY and audio visual (AV) PHY. Different PHYs are due to the demands of different applications, which were based on the development of the usage models for this standard. The SC PHY is designed to support low-cost and low-power mobile devices with low complexity. The HSI PHY is used for bidirectional, low-latency, non-line-ofsight high speed data transmission, such as an ad-hoc system to connect computers and devices around a conference table. The streaming of uncompressed video requires high throughput which is provided by the AV PHY. A minimum data rate is mandated by each PHY, and higher data rates are optional to best address the different market segments. In order to promote coexistence among these PHY modes, common mode signaling (CMS) with a low data rate of 25 Mb/s is defined to transmit/receive a synchronization frame in order to avoid interference between two or more operating devices.

Beamforming is supported by all the three PHY modes. A two-level mechanism is employed to find the optimum transmit and receive beams that enable high data rate transmission.

In the following discussions, SC PHY is the main focus because of its common use.

#### 2.1.2 Frequency Allocation

IEEE 802.15.3c operates in the 60-GHz unlicensed band, from 57-66 GHz. A total bandwidth of 9 GHz is allocated, which is divided into four frequency channels with each channel bandwidth of 2.16 GHz, as shown in Fig. 2.1 and Table 2.1.

58.32GHz 60.48GHz 62.64GHz 64.80GHz

Fig. 2.1 Frequency allocation of IEEE 802.15.3c

| CHNL_ID | Start frequency | Center frequency | Stop frequency |

|---------|-----------------|------------------|----------------|

| 1       | 57.24 GHz       | 58.32 GHz        | 59.40 GHz      |

| 2       | 59.40 GHz       | 60.48 GHz        | 61.56 GHz      |

| 3       | 61.56 GHz       | 62.64 GHz        | 63.72 GHz      |

| 4       | 63.72 GHz       | 64.80 GHz        | 65.88 GHz      |

Table 2.1 RF channelization of IEEE 802.15.3c

#### 2.1.3 Transmit Power

In different geographical regions, a compliant device should transmit a power with level not exceeding the power limit specified by appropriate regulatory bodies [2]. The power limit is summarized in Table. 2.2.

| Region     | Maximum<br>Transmit Power<br>(dBm) | Maximum<br>EIRP<br>(dBm) | Maximum<br>Antenna Gain<br>(dBi)    |

|------------|------------------------------------|--------------------------|-------------------------------------|

| USA/Canada | 27                                 | 43.0                     | 33.0<br>if P <sub>TX</sub> = 10 dBm |

| Europe     | 13                                 | 57.0                     | 30.0                                |

| Japan      | 10                                 | 58.0                     | 47.0                                |

| Australia  | 10                                 | 51.8                     | 41.8                                |

| Korea      | 10                                 | 27.0                     | 17.0                                |

Table 2.2 Transmit power limit in different regions

#### 2.1.4 Data Rate

Three classes of modulation and coding scheme (MCS) aiming for different wireless applications are provided by the single carrier mode specified in IEEE 802.15.3c. Class 1 is suitable for low-power low-cost mobiles with relatively high data rate of up to 1.5 Gb/s. Class 2 is able to achieve data rates up to 3 Gb/s. Class 3 features high performance with data rates exceeding 5 Gb/s.

The chip rate is constant at 1760 M chip/s corresponding to chip duration time of 0.568 ns. The data rates for different specified MCS classes are listed in Table 2.3.

| MCS<br>Class | Identifier | Data Rate<br>(Mb/s)* | Modulation      | Code Rate |

|--------------|------------|----------------------|-----------------|-----------|

|              | 0          | 25.8                 |                 | 15/1024   |

|              | 1          | 412                  |                 | 15/64     |

|              | 2          | 825                  |                 | 15/32     |

| Class 1      | 3          | 1650                 | π/2 BPSK/(G)MSK | 15/16     |

|              | 4          | 1320                 |                 | 3/4       |

|              | 5          | 440                  | -               | 1/4       |

|              | 6          | 880                  |                 | 1/2       |

|              | 7          | 1760                 |                 | 1/2       |

|              | 8          | 2640                 |                 | 3/4       |

| Class 2      | 9          | 3080                 | π/2 QPSK        | 7/8       |

|              | 10         | 3290                 |                 | 238/255   |

|              | 11         | 3300                 |                 | 239/255   |

| Class 3      | 12         | 3960                 | π/2 8-PSK       | 3/4       |

| Class 5      | 13         | 5280                 | π/2 16-QAM      | 3/4       |

Table 2.3 Date rates for different MCS classes in single carrier mode

\* With pilot word length = 0

#### 2.1.5 Error Vector Magnitude

Error Vector Magnitude (EVM) is a measure of transmitter performance. For different classes of MCS in single carrier mode, it's specified and listed in Table 2.4.

| MCS     | EVM (dB) |

|---------|----------|

| Class 1 | -7       |

| Class 2 | -14      |

| Class 3 | -21      |

Table 2.4 EVM for MCS classes in single carrier mode

#### 2.1.6 Frame Error Rate

Frame error rate (FER) is a measure of the noise performance of the receiver. In single carrier mode, the frame error rate should be less than 8% with a frame payload length of 2048 octets in AWGN channel.

The probability of a frame received without error is expressed as:

$$(1 - BER)^{2048 \times 8} = 1 - FER$$

, (2.1)

where BER is bit error rate. Therefore, BER is derived to be  $5.09 \times 10^{-6}$ .

#### 2.1.7 Receiver Input Power

The minimum power level present at the input of the receiver for which the frame error rate is met is called the sensitivity. For different MCSs in single carrier mode, the reference sensitivity is listed in Table 2.5.

On the other hand, the maximum power level input to the receiver is also specified, and it should be at least -10dBm.

#### 2.2 Link Budget

#### 2.2.1 Radiated Power

In order to meet the requirement on power limit specified by appropriate regulatory bodies as show in Table 2.2, the transmitter is designed to transmit a maximum power of 10dBm. Assuming the antennas are in package with gain of 7dBi [3], the total radiated power is 17dBm.

| MCS identifier | Receiver Sensitivity (dBm) |

|----------------|----------------------------|

| 0              | -70                        |

| 1              | -61                        |

| 2              | -58                        |

| 3              | -55                        |

| 4              | -59                        |

| 5              | -65                        |

| 6              | -62                        |

| 7              | -58                        |

| 8              | -56                        |

| 9              | -54                        |

| 10             | -53                        |

| 11             | -52                        |

| 12             | -50                        |

| 13             | -46                        |

Table 2.5 Receiver sensitivity for each MCS in single carrier mode

#### 2.2.2 Path Loss

Path loss (PL) is defined as the ratio of the output power of the transmit antenna to the input power available at the receive antenna. Basically, it's a function of the operating frequency. In free space, the path loss can be calculated by Friis Formula [4]:

$$PL = -20\log_{10}\left(\frac{\lambda}{4\pi R}\right), \qquad (2.2)$$

where  $\lambda$  is the wavelength, R is the distance between the transmitter and the receiver.

For a 60-GHz signal with distance of 1 meter, the path loss in free space ( $PL_0$ ) is 68dB. Therefore, the path loss at distance of R in practical channels can be calculated as:

$$PL = PL_0 + 10 \cdot n \cdot \log_{10} R , \qquad (2.3)$$

where n is the channel parameter. For example, n is approximately to be 2 and 2.5 for simple line-of-sight (LOS) and non-line-of-sight (NLOS) channels, respectively.

#### $2.2.3 E_b/N_0$

Bit error rate (BER) is a function of  $E_b/N_0$ . The BER would typically decrease as  $E_b/N_0$  increases in a certain channel. For different modulation and coding schemes in single carrier mode, the simulated results show the corresponding minimum required  $E_b/N_0$  to meet the specified frame error rate with two mandatory usage models in residential environment. CM 1.3 and CM 2.3 are typical LOS and NLOS channel models, whose simulated BER performance are shown in Fig. 2.2 and Fig. 2.3 [5], respectively. Particularly, the MCS 13 in SC mode which offers the highest data rate requires minimum  $E_b/N_0$  of 7.2 dB and 14.8 dB for CM 1.3 and CM 2.3 to achieve BER of  $5.09 \times 10^{-6}$ , respectively.

Fig. 2.2 BER performance of SC and OFDM PHY for CM1.3 (LOS)

Fig. 2.3 BER performance of SC and OFDM PHY for CM2.3 (NLOS)

#### 2.2.4 Tolerable Path Loss and Maximum Operating Range

The link budget corresponding to highest data rate in single carrier mode is calculated and summarized in Table 2.6. During calculation, it's assumed that both the transmit antenna and receive antenna have a gain of 7dBi [6] and the implementation loss is 6 dB, while the noise figure of the receiver is defined to be a typical value of 8dB [6]-[8].

For basic receiver, the tolerable path loss in NLOS channel is only 2.7dB, resulting operating range of 1.3m.

Fortunately, this very limited operating range can be improved by using phasedarrays. As discussed in next chapter, a 1×4 phased-array with 1 transmit elements and 4 receive elements can theoretically improve signal-to-noise ratio (SNR) by 6dB at the receiver side [9]. As a result, the maximum operation range for NLOS channel is increased to be 3.5m.

| Parameter                                             |                                                                                                     | LOS<br>Channel | NLOS<br>Channel |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|-----------------|

| Bit Rate $(R_b)$                                      |                                                                                                     | 7.04 Gb/s      | 7.04 Gb/s       |

| Power $(P_{Tx})$                                      |                                                                                                     | 10 dBm         | 10 dBm          |

| Tx Antenna Gain $(G_T)$                               |                                                                                                     | 7 dBi          | 7 dBi           |

| Center Frequency $(f_c)$                              |                                                                                                     | 60 GHz         | 60 GHz          |

| Path Loss @ 1 m ( $PL_0 = 20log_{10}(4\pi f_c/c)$     |                                                                                                     | 68.00 dB       | 68.00 dB        |

| Rx Antenna Gain $(G_R)$                               |                                                                                                     | 7 dBi          | 7 dBi           |

| Minimum $E_b/N_0(S)$                                  |                                                                                                     | 7.2 dB         | 14.8 dB         |

| Path Loss Exponent ( <i>n</i> )                       |                                                                                                     | 2.0            | 2.5             |

| Implementation Loss (IL)                              |                                                                                                     | 6 dB           | 6 dB            |

| Rx Noise Figure Referred to the Antenna Terminal (NF) |                                                                                                     | 8 dB           | 8 dB            |

| Per<br>Element                                        | Average Noise Power Per Bit at Rx Input ( $N = -174 + 10 \log R_b$ )                                | -75.5 dBm      | -75.5 dBm       |

|                                                       | Average Noise Power Per Bit at Rx Output ( $P_N = N+NF$ )                                           | -67.5 dBm      | -67.5 dBm       |

|                                                       | Tolerable Path Loss $(PL = P_{Tx} + G_T + G_R - P_N - S - IL - PL_0)$                               | 10.3 dB        | 2.7 dB          |

|                                                       | Maximum Operating Range $(d = 10^{PL/10n})$                                                         | 3.3 m          | 1.3 m           |

| 1×4<br>Phased-<br>Array                               | Number of Tx Elements $(N_T)$                                                                       | 1              | 1               |

|                                                       | Number of Rx Elements $(N_R)$                                                                       | 4              | 4               |

|                                                       | Average Noise Power Per Bit at Rx Input ( $N = -174 + 10 \log R_b + 10 \log N_R$ )                  | -69.5 dBm      | -69.5 dBm       |

|                                                       | Average Noise Power Per Bit at Rx Output $(P_N = N_R + NF)$                                         | -61.5 dBm      | -61.5 dBm       |

|                                                       | Tolerable Path Loss ( $PL = P_{Tx} + G_T + 20 \log N_T + G_R + 20 \log N_R - P_N - S - IL - PL_0$ ) | 21.4 dB        | 13.7 dB         |

|                                                       | Maximum Operating Range ( $d = 10^{PL/10n}$ )                                                       | 6.6 m          | 2.2 m           |

Table 2.6 Link budget for single carrier mode of IEEE 802.15.3c

# 2.3 Receiver Specification

## 2.3.1 Conversion Gain

Conversion gain is a measure of the amplifying capability of a device and defined as the ratio of the output power (voltage) to the input power (voltage) where the input and output frequencies may be different. The cascaded conversion gain of a receiver is the sum of the voltage or power gain of each building block in the signal path.

The input voltage amplitude for an ADC with 1-V supply is assumed to be 0.25V, which is equal to -12dBV.

When operating at the lowest data rate of 25.8 Mb/s corresponding to MCS 0, the input power to the receiver is a minimum value of -70dBm which is equivalent to voltage swing of -80dBV for 50 $\Omega$  impedance. Therefore, the maximum conversion gain is 68dB.

On the other hand, when the input power is maximum specified as -10dBm which is equivalent to voltage swing of -20dBV for  $50\Omega$  impedance, the conversion gain is minimum and derived to be 8dB.

As a result, the gain of the receiver has to be tunable from 8dB to 68dB to generate the same output power level to the ADC with different input power levels.

#### 2.3.2 Signal-to-Noise Ratio

Signal-to-noise ratio (SNR) is an important parameter of a receiver and defined as the power ratio of the desired output signal to the noise, as shown below:

$$SNR = \frac{P_{in}}{N_{in}} = \frac{P_{in}}{N_o \cdot BW} \quad , \tag{2.4}$$

where  $P_{in}$  is the input power,  $N_{in}$  is the input noise,  $N_o$  is spectral noise density, and BW is the bandwidth occupied.

In IEEE 802.15.3c standard, the required SNR is not directly specified. Instead, it should be derived from Eb/No together with modulation coding scheme.

$E_b/N_o$  is expressed as:

$$\frac{E_b}{N_o} = \frac{P_{in}}{N_o} \cdot \frac{T_c}{n_c} , \qquad (2.5)$$

where  $T_c$  and  $n_c$  are chip duration time and number of bits per chip, respectively.

From Eq. (2.4) and (2.5), the SNR is related to  $E_b/N_o$ , as shown below:

$$SNR = \frac{E_b}{N_a} \cdot \frac{1}{BW} \cdot \frac{n_c}{T_c} , \qquad (2.6)$$

Since MCS 13 offers the highest data rate in SC PHY mode, it's targeted at and its requirement is calculated. In 2.2.3,  $E_b/N_o$  has been derived to be 7.2 dB and 14.8 dB for CM 1.3 and CM 2.3 to achieve required minimum BER. BW is specified to be 2.16 GHz for each of the four channels while  $T_c$  is equal to 0.568 ns. With  $\pi/2$  16-QAM modulation,  $n_c$  of MCS 13 is 4. As a result, the required SNR is calculated to be 12.3dB and 19.9dB for LOS channel model CM 1.3 and NLOS channel mode CM 2.3, respectively.

#### 2.3.3 Noise Figure

Noise factor is a measure of the noise performance of a receiver and defined as the ratio of input SNR to output SNR. When expressed in dB scale, it's named noise figure (NF).

$$NF = P_{in} - N_{in} - SNR_{out}$$

=  $P_{in} - N_o - 10 \log BW - SNR_{out}$ , (2.7)

=  $P_{in} - 10 \log BW - SNR_{out} + 174$

For MCS 13, the minimum  $P_{in}$  is defined by the sensitivity which is -46dBm. Therefore, the noise figure is calculated as follows:

$$NF = -46 - 10\log(2.16G) - 19.9 + 174 = 14.8(dB) , \qquad (2.8)$$

To have better SNR which may be required by future more complicated channel model or higher data rate or longer operation distance, the targeted noise figure of the receiver is 8dB, which is close to the state-of-the-art value.

The cascaded noise figure of a receiver [10] is dominated by the noise figure and gain of the LNA. The contribution from the following stages diminishes thanks to the positive gain introduced by the previous stages.

#### 2.3.4 Linearity

Commonly used parameters to characterize the linearity of a receiver are 1-dB compression point ( $P_{1dB}$ ) and input referred third-order interception point (IIP3).  $P_{1dB}$  defines the input power level at which the amplifier's gain is 1dB less than the small signal gain, or is compressed by 1dB. IIP3 defines the input power level at which the output third-order product intercepts with the output fundamental tone.

In IEEE 802.15.3c standard, the maximum input power to the receiver is specified to be -10dBm, so P<sub>1dB</sub> is chosen to be -10dBm.

However, when there are interferers located at adjacent channels, their intermodulation product may reduce the SNR and even completely corrupt the desired received signal, as shown in Fig. 2.4.

Fig. 2.4 Intermodulation product generated by interference signals

The third-order intermodulation product  $P_{out, IM3}$  is related to IIP3 [10], as show below:

$$\frac{P_{out,int}}{P_{out,IM3}} = \left(\frac{IIP3}{P_{in,int}}\right)^2 .$$

(2.9)

The gain is the same for both desired signal and interference, so it's written as:

$$\frac{P_{out,\text{int}}}{P_{in,\text{int}}} = \frac{P_{out}}{P_{in}} \quad . \tag{2.10}$$

From Eq. (2.9) and (2.10), the third-order intermodulation product is derived as to be:

$$\frac{P_{out,IM3}}{P_{out}} = \frac{P_{in,int}^3}{P_{in} \cdot IIP3^2} .$$

(2.11)

In order to obtain the required SNR, the intermodulation product should be lower than the noise level when the power of desired input signal is the minimum. Therefore, Eq. (2.11) is rewritten as:

$$\frac{P_{out,IM3}}{P_{out}} = \frac{P_{in,int}^{3}}{P_{in} \cdot IIP3^{2}} \le \frac{N_{out}}{P_{out}} = \frac{1}{SNR_{out}}$$

(2.12)

As such, the requirement on IIP is derived:

$$IIP3 \ge \sqrt{\frac{P_{in,int}^3}{P_{in}} \cdot SNR_{out}} \quad , \tag{2.13}$$

which can be rewritten in dB scale as:

$$IIP3 \ge P_{in,int} + \frac{P_{in,int} - P_{in} + SNR_{out}}{2} \quad . \tag{2.14}$$

For MCS 13, the minimum input power is -46dBm and the minimum SNR<sub>out</sub> is 19.9dB for CM 2.3 channel model. Assuming that the interference signal comes from a transmitter located in 10cm away with transmit power of 10dBm and an antenna gain of 7dBi, the received signal by the receive antenna with 7dBi gain is calculated as:

$$P_{\text{interference}} = P_{TX} + G_T - PL_{@1cm} + G_R = 10 + 7 - 48 + 7 = -24 \ (dBm) \ . \tag{2.15}$$

Therefore, the corresponding required IIP3 is derived to be -3dBm.

For a 4×4 phased-array transceiver, the interference is 12dB larger due to spatial power combining. Fortunately, its beamforming nature can help to reduce the interference by properly rotating the beam direction. For example, a phased-array with peak-to-null ratio of 25dB can ideally reduce the power received interference to be - 37dBm. As a result, the required IIP3 is ideally relaxed to be -22dBm.

## 2.3.5 Specification Summary

Similar to the above steps, specification for more cases such as different MCS classes in SC mode and different input power levels are calculated and derived. Finally, the detailed specification is summarized in Table 2.7.

| Parameters              | IEEE 802.15.3c                                | Specification                                 |

|-------------------------|-----------------------------------------------|-----------------------------------------------|

| Frequency [GHz]         | 57~66                                         | 57~66                                         |

| Voltage Gain[dB]        | 8 (low gain)<br>68 (high gain)                | 8 (low gain)<br>74 (high gain)                |

| Noise Figure [dB]       | 50.0 (low gain)<br>14.0 (high gain)           | 44.0 (gain=8)<br>8.0 (gain=74~50)             |

| IIP3 [dBm]              |                                               | -3 (gain=8)                                   |

| P <sub>1dB</sub> [dBm]  | -10                                           | -10                                           |

| Sensitivity [dBm]       | -70 for MCS0<br>-58 for MCS7<br>-46 for MCS13 | -76 for MCS0<br>-64 for MCS7<br>-52 for MCS13 |

| Input Matching S11 [dB] |                                               | -10                                           |

Table 2.7 Specification of receiver RF font-end

## **Bibliography**

[1] IEEE Standard Part 15.3: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for High Rate Wireless Personal Area Networks (WPANs), 2009.

[2] S.-K. Yong, P. Xia and A. Valdes-Garcia, "60 GHz Technology for Gbps WLAN and WPAN," *John Wiley & Sons Ltd*, 2011.

[3] L. Duixian, J. Akkermans and B. Floyd, "A superstrate patch antenna for 60-GHz applications," *European Conference on Antennas and Propagation*, pp. 2592-2594, Mar. 2009.

[4] H.T. Friis, "A Note on a Simple Transmission Formula," *Proceeding of the IRE*, vol.34, pp. 254-256, May. 1946.

[5] O. Hoffmann, R. Kays and R. Reinhold, "Coded Performance of OFDM and SC PHY of IEEE 802.15.3c for Different FEC Types," *GLOBECOM Workshops, IEEE*, pp. 1-3, Nov. –Dec. 2009.

[6] A. Natarajan, S. K. Reynolds, T. Ming-Da, S. T. Nicolson, J. H. C. Zhan, K. Dong Gun, L. Duixian, Y. L. O. Huang, A. Valdes-Garcia and B. A. Floyd, "A Fully-Integrated 16-Element Phased-Array Receiver in SiGe BiCMOS for 60-GHz Communications," *IEEE J. Solid-State Circuits*, vol. 46, pp. 1059-1075, May. 2011.

[7] S. Emami, R. F. Wiser, E. Ali, M. G. Forbes, M. Q. Gordon, G. Xiang, S. Lo, P. T. McElwee, J. Parker, J. R. Tani, J. M. Gilbert and C. H. Doan, "A 60GHz CMOS Phased-Array Transceiver Pair for Multi-Gb/s Wireless Communications," *ISSCC Dig. Tech. Papers*, pp.164-165, Feb. 2011.

[8] V. Vidojkovic, G. Mangraviti, K. Khalaf, V. Szortyka, K. Vaesen, W. Van Thillo, B. Parvais, M. Libois, S. Thijs, J. R. Long, C. Soens and P. Wambacq, "A Low-Power 57-to-66GHz Transceiver in 40nm LP CMOS with -17dB EVM at 7Gb/s," *ISSCC Dig. Tech Papers*, pp.268-269, Feb. 2012.

[9] H. J. Visser, "Array and Phased-Array Antenna Basics," *John Wiley & Sons Ltd*, 2005.

[10] B. Razavi, "RF Microelectronics," Prentice-Hall Inc., 1998.

# **Chapter 3**

# **Phased-Array Receiver Architecture**

# 3.1 Overview of Receiver Architectures [1]

To implement 60-GHz receiver, the existing system architectures have to be studied carefully to know the trade-offs and thus choose the optimal architecture. Moreover, basic architectures are the foundations to construct phased-array systems. In this subsection, some commonly used receiver architectures are investigated, including super heterodyne topology, direct-conversion topology and dual-conversion zero-IF topology.

## **3.1.1 Super Heterodyne Topology**

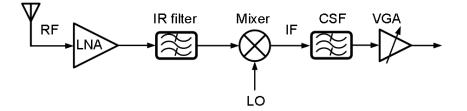

A super heterodyne receiver is shown in Fig. 3.1. The RF signal is amplified and down-converted to IF, whose frequency is much lower than the RF frequency. As such, the channel selection filter (CSF) is with reasonable quality factor and realizable. Super heterodyne topology features several advantages. LO leakage to the antenna and LO pulling by the power amplifier are typically trivial as long as LO frequency is quite different from the RF frequency. The DC offset due to LO leakage and hence LO self-mixing don't affect the IF.

Fig. 3.1 A super heterodyne receiver

However, the image signal is also down-converted and the IF signal may be corrupted. Therefore, an image-rejection filter (IR filter) is necessary to sufficiently suppress the unwanted harmful image signal. Moreover, the baseband operates at IF frequency and thus high power consumption is expected. In targeted IEEE 802.15.3c standard, the signal bandwidth is already 2.16GHz that any additional IF frequency would significantly increase the power consumption of the ADC.

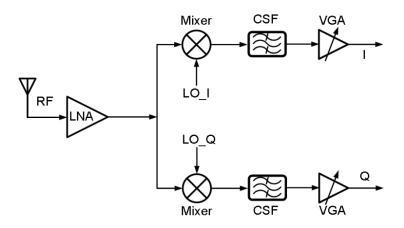

### **3.1.2 Direct-Conversion Topology**

The direct-conversion architecture is shown in Fig. 3.2. The LO frequency is the same as RF frequency and thus the IF frequency is at DC. As long as there is no image signal, image rejection filter is eliminated. Besides, a simple low-pass filter can be used for channel selection.

Fig. 3. 2 A direct-conversion receiver

However, to avoid information loss due to positive and negative spectrum overlapping, quadrature paths should be employed and accurate I/Q phases are required for the LO. Unlike super-heterodyne topology, a direct-conversion receiver suffers from LO leakage, LO pulling and LO self-mixing induced DC offsets, because the LO frequency is the same as RF frequency. DC offsets generated in the mixer due to mismatches are amplified and would saturate the following stages, including the CSF, VGA and ADC.

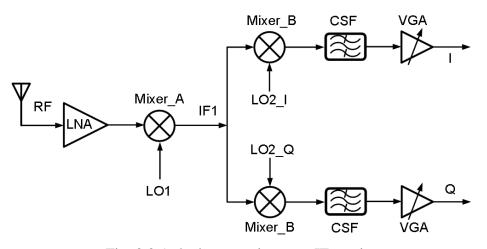

### 3.1.3 Dual-Conversion Zero-IF Topology

In this architecture, two frequency conversions are utilized, as shown in Fig. 3.3. The RF signal is first down-converted to an IF1 frequency and then down-converted by a second mixer. The resultant IF frequency is located at zero. To avoid information loss which is the same scenario as direct-conversion, quadrature paths are necessary. It needs no image-rejection filter, since the IF1 is relatively high that the image signal is very far from the desired signal and thus can be easily filtered out by the band-pass filtering characteristic of the LNA. Frequency pulling, LO leakage and self-mixing is not important because the frequencies of RF, first LO and second LO are totally different. Although more components are needed than direct-conversion architecture, smaller power consumption is possible because of the lower frequency they are operating at. Besides, by properly locating the frequencies, the LOs required can be generated with one frequency synthesizer.

Fig. 3.3 A dual-conversion zero-IF receiver

#### 3.1.4 Summary on Receiver Topology for IEEE 802.15.3c

The channel bandwidth of IEEE 802.15.3c is 2.16 GHz. Therefore, super heterodyne architecture is not suitable due to the need of ultra-high-speed ADC. The operation frequency of ADC can be relaxed by using I/Q paths with two ADCs. As such, direction-conversion or dual-conversion zero-IF architectures are widely used in literatures [2]-[3].

# 3.2 Phased-Array Receiver Architectures

Phased-arrays are a special class of multiple antenna systems that exhibit spatial power combining and electronic beamforming by time delay compensation in the signal paths of different elements [4]. Phased-arrays have played a key role in boosting signal quality through spatial diversity, interference mitigation via spatial filtering, and data rates with spatial multiplexing. [5]

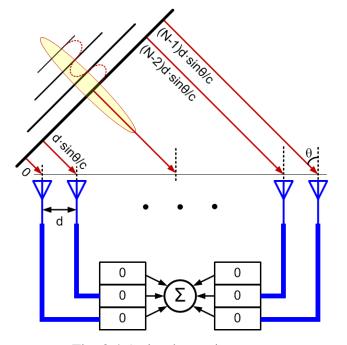

### 3.2.1 Phased-Array Principles [5]-[6]

An N-element simple antenna array with antenna distance of d is shown in Fig. 3.4. A plane wave impinges on each element at an angle  $\theta$  relative to the array normal. The signal at the Element k is then given by:

$$x_k(t) = \operatorname{Re}\left[\tilde{x}_1(t - k\Delta_0) \exp\left(j2\pi f_c(t - k\Delta_0)\right)\right], \qquad (3.1)$$

where  $\Delta_0$  is the relative time of flight between two adjacent elements and expressed as:

$$\Delta_0 = d\sin\theta/c \quad . \tag{3.2}$$

$\theta$  is the incident angle and c is the propagation velocity.

For a narrowband signal with bandwidth much smaller than the carrier frequency, the array output for the system in Fig. 3.4 can be written as:

$$y(t) = \operatorname{Re}\left\{\sum_{k=0}^{N-1} \tilde{x}_{1}(t - k\Delta_{0}) \exp\left[j2\pi f_{c}(t - k\Delta_{0})\right]\right\}$$

$$\approx \operatorname{Re}\left\{\left[\sum_{k=0}^{N-1} \exp\left(-j2\pi f_{c}k\Delta_{0}\right)\right] \tilde{x}_{1}(t) \exp\left(j2\pi f_{c}t\right)\right\}.$$

(3.3)

Fig. 3.4 A simple receiver array

By defining  $\psi$  as:

$$\psi = 2\pi f_c \Delta_0 \quad , \tag{3.4}$$

which can be interpreted as equivalent to an "electrical envelope phase shift" for each element, the complex envelope of the array output is derived as:

$$\tilde{y}(t) = \left[\sum_{k=0}^{N-1} \exp\left[-jk\psi\right]\right] \tilde{x}_1(t) \quad .$$

(3.5)

As a result, the array gain is derived to be:

$$G(\psi) = \left[\sum_{k=0}^{N-1} \exp\left(-jk\psi\right)\right] = e^{-\frac{j(N-1)\psi}{2}} \frac{\sin\left(\frac{N\psi}{2}\right)}{\sin\left(\frac{\psi}{2}\right)} \quad . \tag{3.6}$$

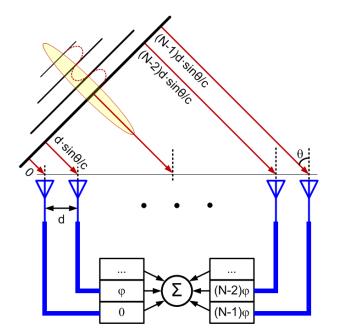

As shown in Fig. 2.5, if variable phase shifts are introduced, the signal received by each element is electrically phase shifted by an angle  $\varphi$  relative to its neighboring element. Therefore, the array output can be expressed as:

$$\tilde{y}(t) = \left[\sum_{k=0}^{N-1} \exp\left[-jk\left(\psi + \varphi\right)\right]\right] \tilde{x}_1(t) = A\left(\psi + \varphi\right) \cdot \tilde{x}_1(t) \quad . \tag{3.7}$$

/

Accordingly, the array gain is derived to be:

$$G(\psi) = \left[\sum_{k=0}^{N-1} \exp\left(-jk\left(\psi + \varphi\right)\right)\right] = e^{-\frac{j(N-1)\psi}{2}} \frac{\sin\left(\frac{N\left(\psi + \varphi\right)}{2}\right)}{\sin\left(\frac{(\psi + \varphi)}{2}\right)} \quad . \tag{3.8}$$

Fig. 3.5 A phased-array receiver

Clearly, the beam direction is rotated by an angle of  $\varphi$ , which is equivalent to a spatial angle of:

$$\theta_0 = \sin^{-1} \left[ -\left( \varphi / 2\pi \right) \left( \lambda / d \right) \right] . \tag{3.9}$$

Therefore, the array gain now has a peak in the direction of the angle  $\theta_0$ .

If the spacing d is too large compared to a wavelength, the array pattern will have a grating lobe, which happens at an angle of  $\theta_0$ ' expressed as:

$$\frac{2\pi}{\lambda}d\sin\theta_0' - \varphi = \pm 2\pi \quad . \tag{3.10}$$

From Eq. (3.9) and (3.10), it can be derived that:

$$\sin \theta_0' = \sin \theta_0 \pm \frac{\lambda}{d} \quad . \tag{3.11}$$

To prevent a grating lobe, the following condition should be satisfied:

$$\frac{d}{\lambda} \le \frac{1}{1 + |\sin \theta_0|} \quad , \tag{3.12}$$

which indicates that the spacing d should not be larger than half of the wavelength. As such, the elements are so close to each other that the received signals are tightly correlated in amplitude. Thus, the signals add in amplitude while any uncorrelated noise signals add in power. Consequently, SNR gets improved by  $10\log_{10}N$  as the element number N increases.

On the transmit side, the output power gets increased by  $20\log_{10}N$  due to special power combining. Overall, an N×N phased-array with N transmit elements and N receive element improves the link budget by  $30\log_{10}N$ .

## 3.2.2 Phase Shifting Configurations

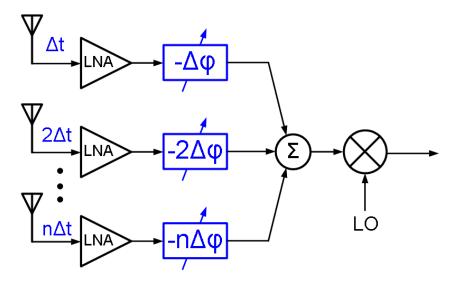

To steer the beam direction of a phased-array receiver, phase shifters can be implemented in different stages: RF, LO, IF or digital baseband [7]-[8].

## 3.2.2.1 RF Phase Shifting

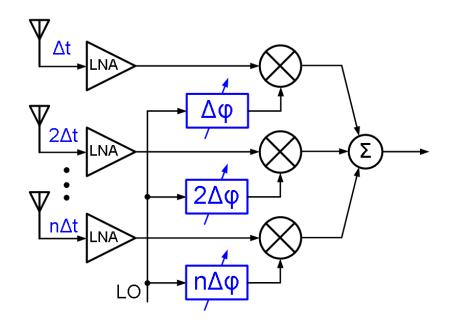

In RF phase shifting architecture [2]-[3], the RF signals get phase shifted and combined at RF, and further down-converted to IF or baseband, as shown in Fig. 3.6.

Fig. 3.6 RF phase shifting configuration

There is only one down-conversion path, including mixers, analog and digital baseband. Moreover, the unwanted signals are suppressed before going to the mixers, so that the dynamic range requirement of the mixers is relaxed. However, the performance of the phase shifters in terms of loss, noise figure, linearity and mismatches directly affects the system since the phase shifters are in signal path, let alone with high frequency and process variation taken into account. Particularly, the phase shifter should have sufficient dynamic range to tolerate the signal level fluctuations.

## 3.2.2.2 LO Phase Shifting

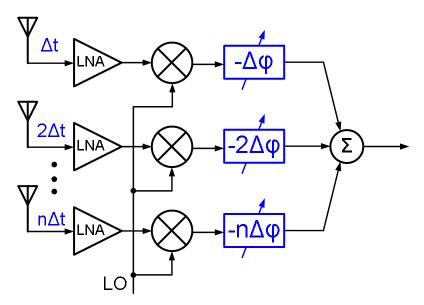

In LO phase shifting, the LO signals are phase shifted [7, 9], as shown in Fig. 3.7.

The main advantage over RF phase shifting is that the system performance is not sensitive to the performance of phase shifter. Therefore, the requirement of the phase shifter in terms of noise figure, linearity, loss and amplitude mismatches gets much relaxed. However, more mixers are needed as compared with RF phase shifting, and those mixers should have high dynamic range to tolerate the interference signals. Besides, the large LO signals must be routed and distributed to different paths, introducing issues such as cross-talk and phase coherence.

Fig. 3.7 LO phase shifting configuration

# 3.2.2.3 IF Phase Shifting

Phase shift can be implemented in the IF path, as shown in Fig. 3.8.

Fig. 3.8 IF phase shifting configuration

However, this approach also requires multiple mixers and still suffers from the system performance degradation due to the phase shifter appearing in signal paths. This architecture is not a proper option for low cost and low power phased-array [3].

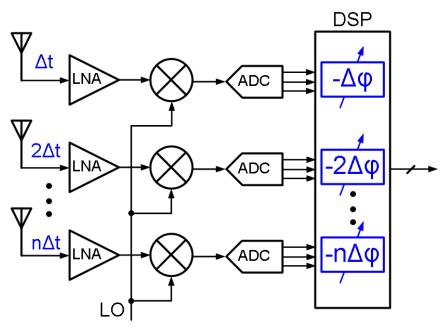

#### 3.2.2.4 Digital Phase Shifting

The phase shifting can be implemented in digital baseband, as shown in Fig. 3.9.

Fig. 3.9 Baseband phase shifting configuration

This configuration features high flexibility and high phase shift accuracy while no dedicated hardware for phase shifters is needed. Concurrent independent multiple beams are allowed. However, multiple mixers and high speed ADCs are required, so substantial complexity and high power consumption are resulted in.

### 3.2.2.5 Summary on Phase Shifting Configuration

The phase shifting configuration should be designed carefully according to the requirement of applications. RF phase shifting requires the least number of hardware but suffers from system performance degradation. It's more proper to be used to implement phased-array with a large number of elements, since the complexity is a main concern while the performance degradation could be compensated by more elements. LO phase shifting is popular when the element number is small, which is

typically not more than 8. Digital domain phase shifting offers the unique capability of concurrent beams. IF phase shifting has comparable complexity with LO phase shifting but the system performance is very sensitive to the phase shifter.

## 3.2.3 Phased-Array Architectures

From the above discussions, the phased-array architecture is more proper to be based on direct-conversion topology or dual-conversion zero-IF topology.

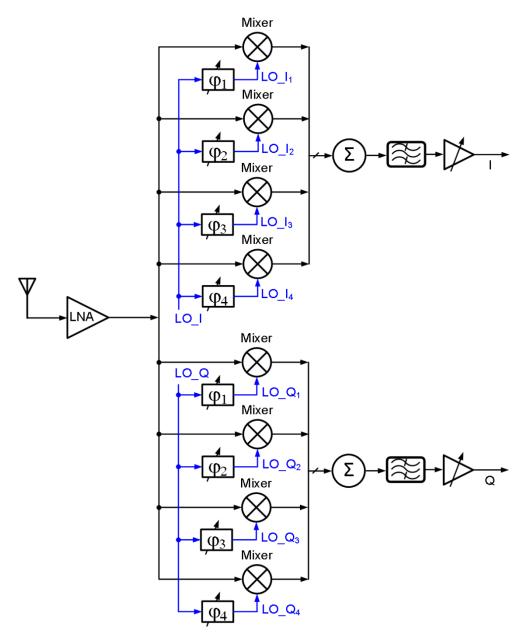

## 3.2.3.1 Direct-Conversion with LO Phase Shifting

A 4-path phased-array receiver based on direct-conversion architecture with LO phase shifting configuration is shown in Fig. 3.10.

8 mixers, 8 phase shifters and 8 LO distribution trees are required. Both the LO and the phase shifters operate at 60 GHz, and thus they are power hungry and area consuming. In addition, routing multiple 60-GHz signals with different phases is quite challenging.

Fig. 3.10 4-path phased-array with direct-conversion and LO phase shifting

# 3.2.3.1 Dual-Conversion Zero-IF with LO Phase Shifting

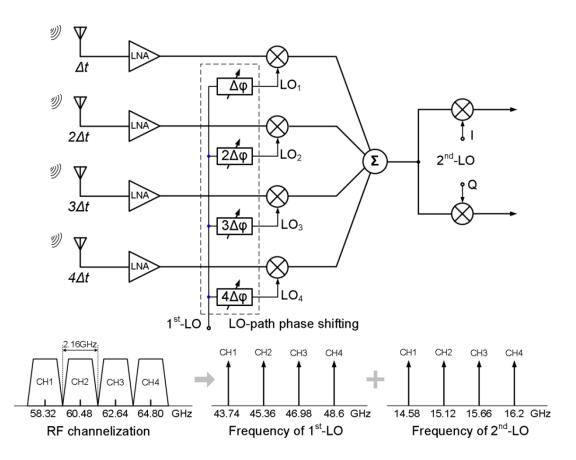

A 4-path phased-array receiver based on dual-conversion zero-IF architecture with LO phase shifting configuration is shown in Fig. 3.11.

Obviously, compared with direct-conversion, the components needed are less and they are working at lower frequencies. Therefore, dual-conversion zero-IF architecture is more suitable to be employed for the 4-path phased-array receiver.

Fig. 3.11 4-path phased-array with dual-conversion zero-IF and LO phase shifting

# 3.3 Proposed 4-Path Phased-Array Receiver RF Front-End

## **3.3.1 Number of Paths**

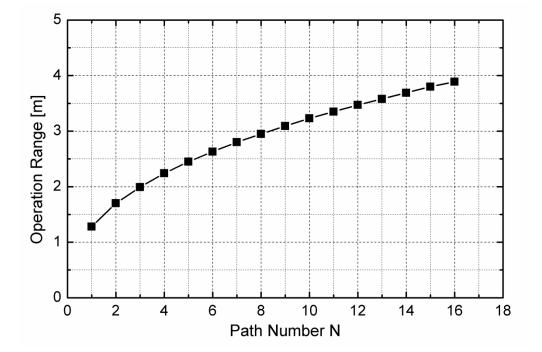

An N-path phased-array receiver improves the link budget by  $10\log_{10}$ N. Targeted at IEEE 802.15.3c, Table 3.1 and Fig. 3.12 show the corresponding operation range at NLOS channel for different path number N.

| Path No. | Max. Operation Range (m) |

|----------|--------------------------|

| 1        | 1.28                     |

| 2        | 1.70                     |

| 3        | 1.99                     |

| 4        | 2.24                     |

| 5        | 2.45                     |

| 6        | 2.63                     |

| 7        | 2.80                     |

| 8        | 2.95                     |

| 9        | 3.09                     |

| 10       | 3.23                     |

| 11       | 3.35                     |

| 12       | 3.47                     |

| 13       | 3.58                     |

| 14       | 3.69                     |

| 15       | 3.80                     |

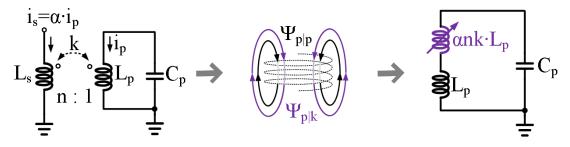

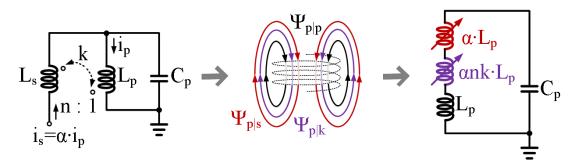

| 16       | 3.89                     |