# A 900-MHz CMOS Bandpass Amplifier for Wireless Receivers

A thesis submitted to

The Hong Kong University of Science and Technology

in partial fulfillment of the requirements for

the Degree of Master of Philosophy in

Electrical and Electronic Engineering

by

Lap Chi LEUNG

Department of Electrical and Electronic Engineering

B.Eng. (Hons), HKUST

August 1999

## A 900-MHz CMOS Bandpass Amplifier

## for Wireless Receivers

by

#### Lap Chi LEUNG

Approved by:

Dr. Howard Cam LUONG Thesis Supervisor

Dr. Wing Hung KI Thesis Examination Committee Member (Chairman)

Dr. Philip Kwok Tai MOK Thesis Examination Committee Member

Prof. Philip C. H. CHAN Head of the Department

Department of Electrical and Electronic Engineering The Hong Kong University of Science and Technology 9 August, 1999

#### A 900-MHz CMOS Bandpass Amplifier for Wireless Receivers

by

Lap Chi LEUNG

for the Degree of

Master of Philosophy in Electrical and Electronic Engineering at The Hong Kong University of Science and Technology in August, 1999

#### Abstract

This dissertation describes the design of a CMOS 900-MHz bandpass amplifier that is suitable for RF transceivers. The work employs the state-of-art inductive degeneration techniques to minimize the noise figure and explores the use of lossy spiral inductors in high frequency circuit to realize input matching networks on-chip. A Q-compensation circuit is included to achieve a 25-MHz 3-dB bandwidth. Besides, a center frequency tuning circuit is also embedded to compensate for frequency deviations due to process variations.

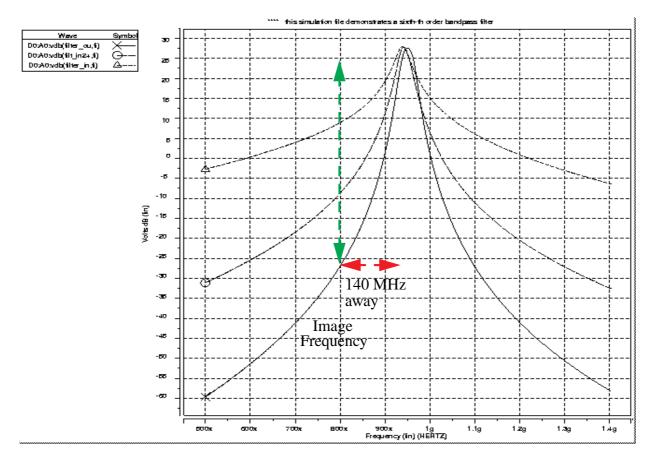

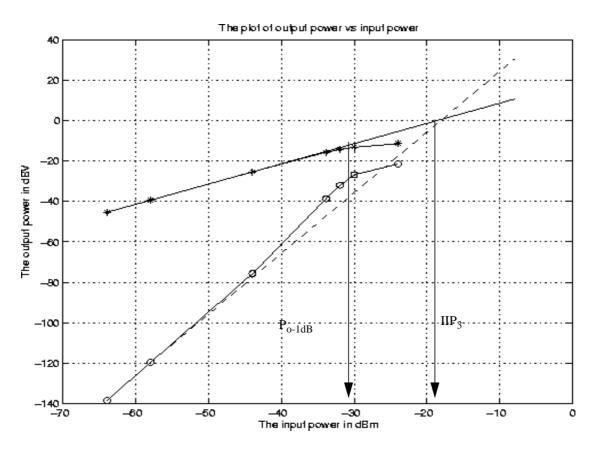

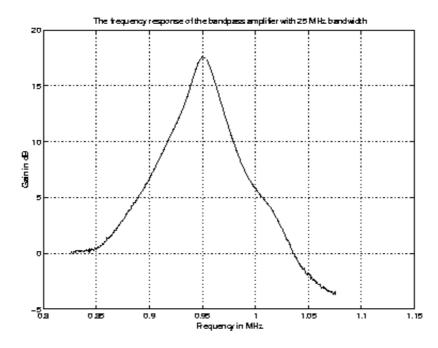

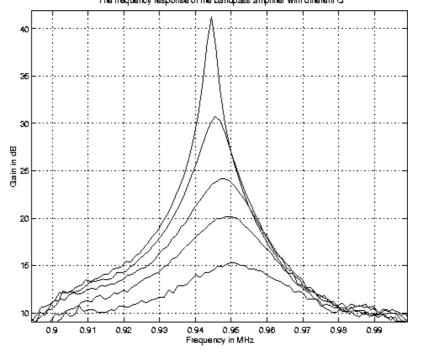

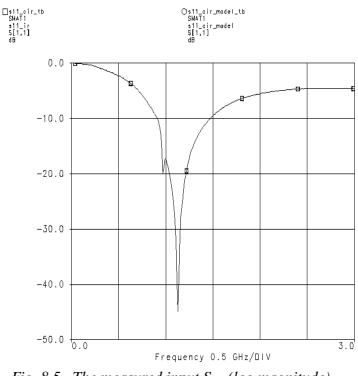

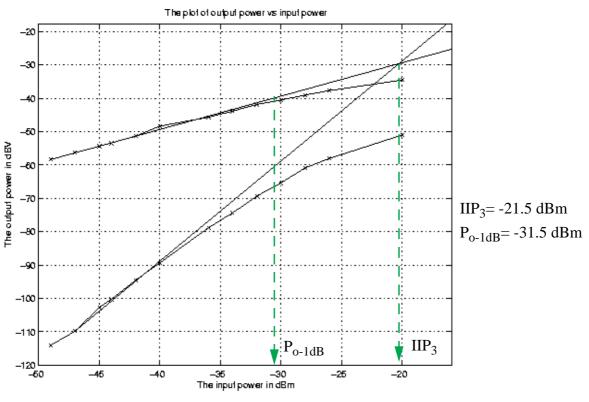

In the first prototype, a second-order bandpass amplifier had been fabricated in standard 0.8  $\mu$ m single-poly, triple-metal CMOS process (HP SCN26G) provided by MOSIS<sup>®</sup>. With a 3-V supply, at 950-MHz and a 3-dB bandwidth of 25-MHz, the measured voltage gain is 26 dB and the input S<sub>11</sub> is -13 dB. Under the same baising condition, the input third-order intermodulation product (IIP<sub>3</sub>) and input-referred 1-dB compression point (P<sub>0,1-dB</sub>) are - 21.5 dBm and -31.5 dBm respectively. The image rejection at 140-MHz away from the desired signal is 20 dB. In addition, the Q of the amplifier can be tuned from around 2 to infinity and the center frequency can also be varied from 930 MHz to 1040 MHz. On the grounds that the measured on-chip spiral's quality factor is merely around 2 (compared to around 3 to 5 in recent literatures), the measured noise figure of the whole amplifier is around 10 dB. The power dissipation and the die area of the first prototype are 90 mW and 1.2  $mm \times 0.8$  mm respectively.

So as to enhance the image rejection ability and to reduce the power consumption, a sixth-

order bandpass amplifier had been implemented and fabricated in standard 0.5µm CMOS process using 2-V supply. In this second prototype, a bandpass amplifier was cascaded with two identical second-order bandpass filters to realize the sixth-order bandpass response.

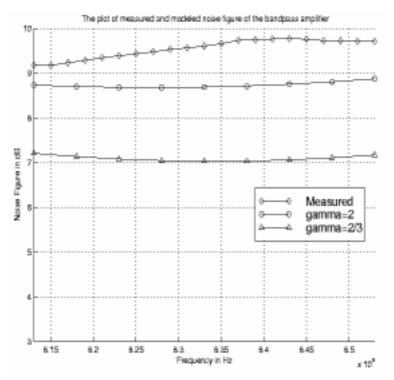

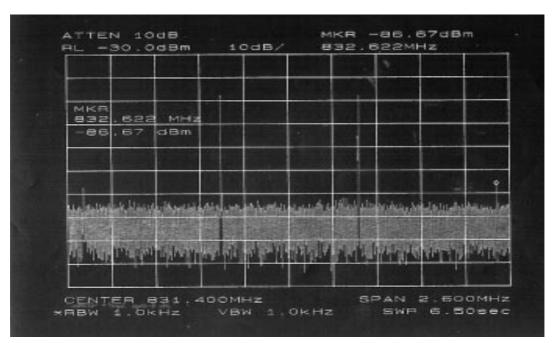

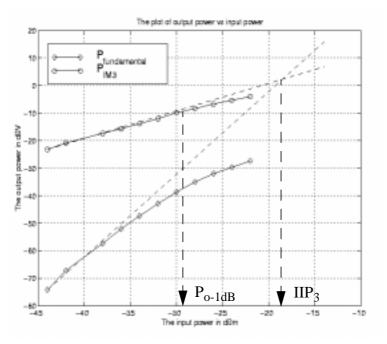

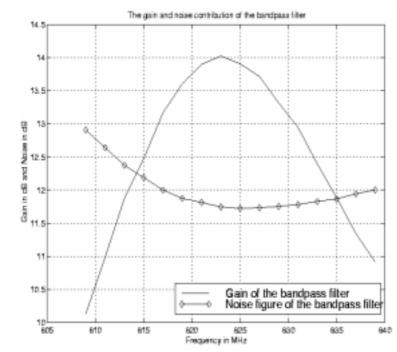

For the bandpass amplifier in the second prototype, the measured voltage gain is 26 dB at 832 MHz and a  $S_{11}$  of -14 dB. With an overall 3-dB bandwidth of 25-MHz, the measured IIP<sub>3</sub> and the 1-dB compression point of the bandpass amplifier are -18.5 dBm and -29 dBm respectively. Besides, the center frequency can be varied between 760 MHz and 832 MHz. The measured noise figure is 9.6 dB, which is much higher than the simulation due to inadequate modeling of the thermal noise in short-channel MOSFETs and the use of low-quality inductors.

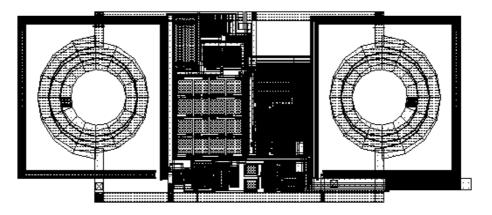

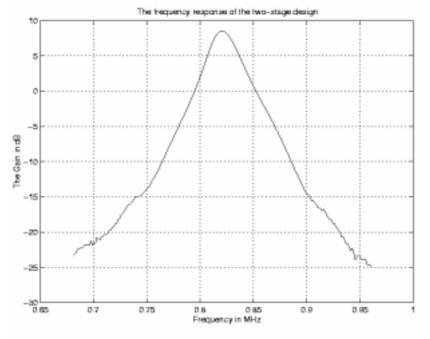

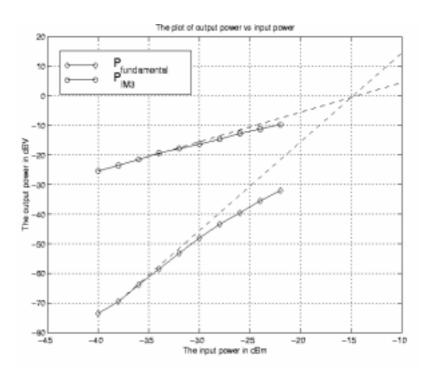

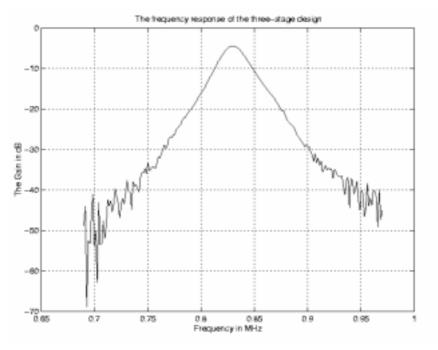

Meanwhile, the performance of the three-stage design in the second prototype was tested, the measured center frequency of the design is located at 830 MHz with a gain of 16 dB. The corresponding 3-dB bandwidth is 25 MHz and the image rejection at 140 MHz away from the desired signal is around 45 dB. In addition, the input third-order intermodulation product (IIP<sub>3</sub>) and the input-referred 1-dB compression point are -15 dBm and -26 dBm respectively. The total current consumption of the three-stage design is 90 mA and the die area of the circuit is only 1.2  $mm \times 0.8$  mm as two-layer inductors were utilized in the design.

### Acknowledgment

At this moment, I believe, is the most suitable time for me to express my heartfelt gratitude to the people who have helped me and supported me during this two-year of studies. Without their help, I can not complete this work on time.

Dr. Howard Luong, my supervisor, introduced me some basic analog circuit theory in my undergraduate studies and aroused my interest in the field. I am deeply indebted to him for his constant support and guidance during my final year project in the Bachelor degree and during the research work in the Master degree. Everytime I encountered difficulties on the design and became discouraged, his suggestion and encouragement help me to regain my confidence and to overcome the obstacles in front of me.

I wish to thank the laboratory technicians, Frederick Kwok, for his technical support on measurement equipments and PCB board making, Jack Chan and S. F. Luk for their assistance in chip tape-out and CAD tools. Meanwhile, I am indebted to H. Y. Pang, who taught me valuable probing techniques and RF issues.

My colleagues, Thomas Choi, Vincent Cheung, Issac Hsu, Ronny Hui, C. B. Guo, Toby Kan, Bob Lo, Brian Ma and William Yan, in the Analog Research Laboratory provided me a lot of useful discussion related to my work. They shared their fun and excitement with me during my hard time.

I had faced a lot of troubles in measuring differential noise figure. Prof. Thomas Lee of Stanford University, Jeff J. J. Ou of University of California Berkeley and John Leete & Dr. Abidi of University of California Los Angeles had provided valuable advice and suggestions on measurement setups and components suitable for low-noise measurement. I would like to express my appreciation for their help.

I would also like to express my gratitude to Dr. W. H. Ki and Dr. Philip Mok for being the thesis chairman and the thesis committee of my presentation and offer me valuable suggestions.

Finally I wish to thank my family for their support during my undergraduate and my postgraduate studies.

## Table of Contents

| Abstract                 |    |  |

|--------------------------|----|--|

| Acknowledgments          |    |  |

| Table of Contents        | i  |  |

| List of Figures          | vi |  |

| List of Tables           |    |  |

|                          |    |  |

| CHAPTER 1 Overview       |    |  |

| 1.1 Motivation           | 1  |  |

| 1.2 Technical Challenges | 2  |  |

| 1.3 Research Goals       | 3  |  |

| 1.4 | Thesis Outline |  |  |

|-----|----------------|--|--|

Analog Research Laboratory

4

#### **CHAPTER 2 RF Fundamentals**

| 2.1 | Introduc | tion                                           | 5  |

|-----|----------|------------------------------------------------|----|

| 2.2 | Basic RI | F Fundamentals                                 | 5  |

|     | 2.2.1    | Sensitivity                                    | 5  |

|     | 2.2.2    | Noise Figure (NF)                              | 6  |

|     | 2.2.3    | Linearity                                      | 7  |

|     |          | 2.2.3.1 1-dB compression point                 | 8  |

|     |          | 2.2.3.2 Third-order Intermodulation Distortion | 9  |

|     |          | 2.2.3.3 Desensitization and Blocking           | 11 |

|     | 2.2.4    | Quality Factor (Q-Factor)                      | 11 |

| 2.3 | GSM sta  | andards and System architecture                | 13 |

|     | 2.3.1    | Minimum and Maximum Tolerable Signals          | 15 |

|     | 2.3.2    | Noise Figure                                   | 15 |

|     | 2.3.3    | Image Rejection                                | 16 |

### CHAPTER 3 Design of Low-Noise Amplifier (LNA) and Bandpass Amplifier

| Introduc               | tion                                                                                                     | 18                                                                                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 Basic LNA Design   |                                                                                                          | 20                                                                                                                                                    |

| 3.2.2<br>3.2.3         | LNA Topology<br>Parallel RLC resonant circuit                                                            | 20<br>25<br>27<br>29                                                                                                                                  |

| 3.3 Monolithic Spirals |                                                                                                          | 29                                                                                                                                                    |

|                        | 1 1                                                                                                      | 29<br>29                                                                                                                                              |

| Design of              | of a bandpass amplifier                                                                                  | 32                                                                                                                                                    |

| 3.4.2                  | Center-frequency tuning circuit                                                                          | 32<br>35<br>40                                                                                                                                        |

|                        | Basic Ll<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Monoliti<br>3.3.1<br>3.3.2<br>Design o<br>3.4.1<br>3.4.2 | <ul> <li>3.2.1 Input Matching</li> <li>3.2.2 LNA Topology</li> <li>3.2.3 Parallel RLC resonant circuit</li> <li>3.2.4 Noise Considerations</li> </ul> |

#### CHAPTER 4 Noise Analysis and Measurement of a bandpass amplifier

| 4.1 | Introduction                                                                                                                                                                                                                                   | 46                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.2 | Noise Analysis                                                                                                                                                                                                                                 | 46                   |

|     | <ul><li>4.2.1 Noise contribution from a resistor</li><li>4.2.2 Thermal Noise in MOSFETs</li></ul>                                                                                                                                              | 47<br>47             |

| 4.3 | Noise Analysis of the basic LNA                                                                                                                                                                                                                | 48                   |

|     | <ul> <li>4.3.1 Noise Analysis of the Q-compensation Circuit</li> <li>4.3.2 Noise Analysis of the Frequency tuning circuit</li> <li>4.3.3 Noise Analysis of the Output Buffer</li> <li>4.3.4 Noise Figure Simulation and Calculation</li> </ul> | 51<br>51<br>52<br>54 |

| 4.4 | Noise Figure Measurement                                                                                                                                                                                                                       | 57                   |

## **CHAPTER 5** Linearity Considerations

| 5.1 Introduction |                                                             |    |  |  |  |

|------------------|-------------------------------------------------------------|----|--|--|--|

| 5.2              | 5.2 Current Situation                                       |    |  |  |  |

| 5.3              | Origins of non-linearity in bandpass amplifiers             | 65 |  |  |  |

| 5.4              | Requirements on the linearity                               | 71 |  |  |  |

| 5.5              | Different types of linearization techniques                 | 74 |  |  |  |

|                  | 5.5.1 Source-Degeneration                                   | 75 |  |  |  |

|                  | 5.5.2 Unbalanced Transconductance pair/ Multi-tanh Approach | 75 |  |  |  |

|                  | 5.5.3 Modified unbalanced gm-pair                           | 78 |  |  |  |

|                  | 5.5.4 Linearity                                             | 81 |  |  |  |

| CHAPTI           | CR 6 High-Order Bandpass Amplifier Design                   | 83 |  |  |  |

| 6.1              | Introduction                                                | 83 |  |  |  |

| 6.2              | Bandpass Filter Design                                      | 84 |  |  |  |

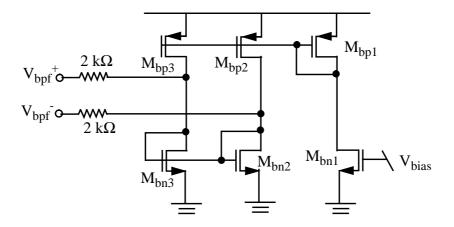

|                  | 6.2.1 Biasing Circuit                                       | 84 |  |  |  |

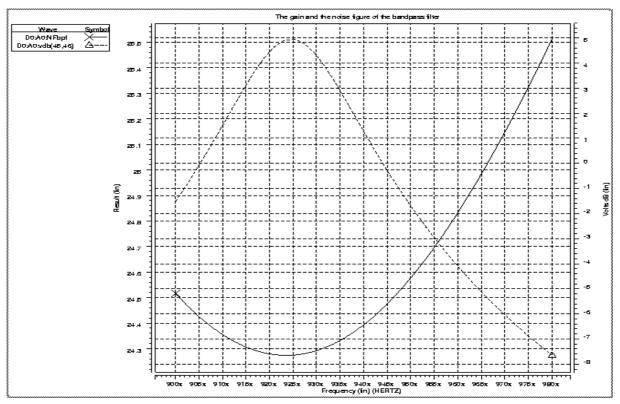

6.2.2 Simulation Result of the bandpass filter

86

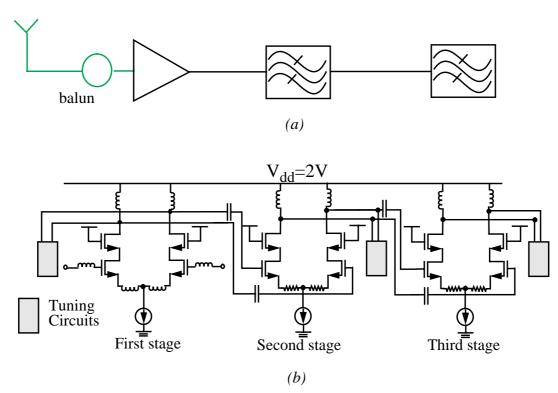

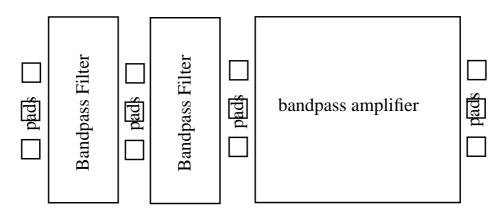

| 6.3 Three-stage, sixth-order Bandpass Amplifier Design           | 86 |

|------------------------------------------------------------------|----|

| 6.3.1 Gain Consideration                                         | 87 |

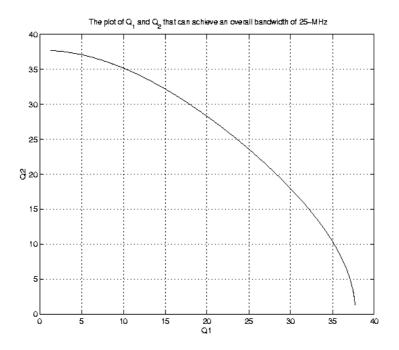

| 6.3.2 Distribution of the Quality Factor                         | 89 |

| 6.3.2.1 Equal Center frequencies                                 | 89 |

| 6.3.2.2 Unequal Center Frequencies                               | 90 |

| 6.4 Simulation Results of the three-stage design                 | 92 |

| 6.4.1 Design with Three Stages Having Same Center Frequencies    | 92 |

| 6.4.2 Design with Three Stages Having Unequal Center Frequencies | 94 |

### **CHAPTER 7** Layout Considerations

| 7.1 | Introduction                                                                    | 100        |

|-----|---------------------------------------------------------------------------------|------------|

| 7.2 | Inductor Layout                                                                 | 101        |

| 7.3 | Capacitor                                                                       | 104        |

|     | <ul><li>7.3.1 Metal-to-Metal Capacitor</li><li>7.3.2 Linear capacitor</li></ul> | 105<br>106 |

| 7.4 | Transistor Layout                                                               | 106        |

| 7.5 | Pad Layout                                                                      | 107        |

| 7.6 | Layout of the actual circuits                                                   | 108        |

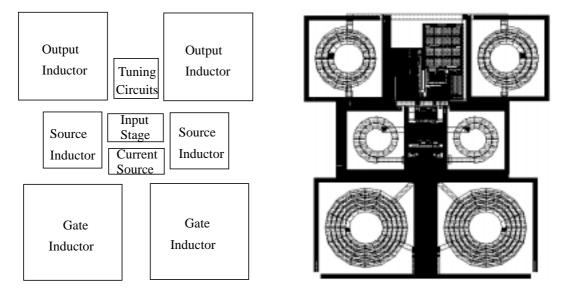

|     | 7.6.1 Layout of the bandpass amplifier                                          | 108        |

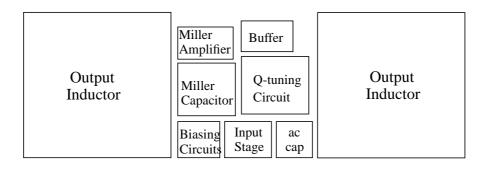

|     | 7.6.2 Layout of the bandpass filter                                             | 109        |

|     | 7.6.3 Complete Layout of the design                                             | 109        |

#### **CHAPTER 8** Measurement Results

| 8.1 | Introduc | tion                                                                                                          | 111               |

|-----|----------|---------------------------------------------------------------------------------------------------------------|-------------------|

| 8.2 | Bandpas  | s Amplifier (First prototype)                                                                                 | 112               |

|     | 8.2.1    | Frequency Response Test Setup<br>8.2.1.1 Center frequency, Gain and Image Rejection<br>8.2.1.2 Tuning ability | 112<br>113<br>114 |

|     |         | Input Matching                                                                                                | 114<br>115        |

|-----|---------|---------------------------------------------------------------------------------------------------------------|-------------------|

|     |         | Linearity Measurement<br>Noise Figure Measurement                                                             | 115               |

| 8.3 | Bandpas | ss Amplifier (Second Prototype)                                                                               | 118               |

|     |         | Inductor Measurement<br>Frequency Response of the bandpass amplifier                                          | 118<br>120        |

|     |         | 8.3.2.1 Tuning range<br>8.3.2.2 Input Matching                                                                | 122<br>123        |

|     |         | Noise Figure Measurement<br>Linearity                                                                         | 124<br>128        |

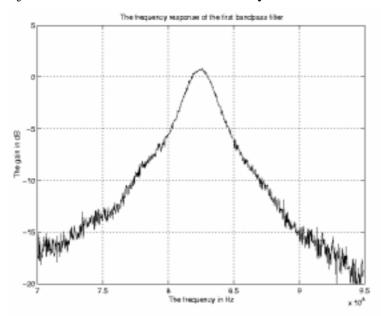

| 8.4 | Bandpas | ss Filters                                                                                                    | 130               |

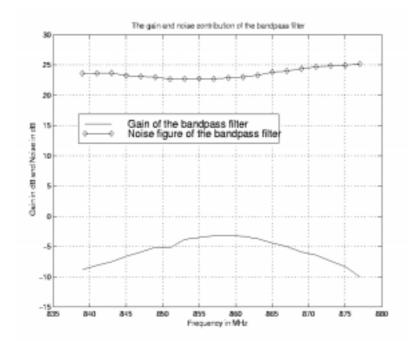

|     | 8.4.1   | First bandpass filter<br>8.4.1.1 Frequency Response<br>8.4.1.2 Noise Performance of the first bandpass filter | 130<br>130<br>130 |

|     |         | Measurement Results of the second filter<br>8.4.2.1 Noise Measurement of the second filter                    | 131<br>131<br>122 |

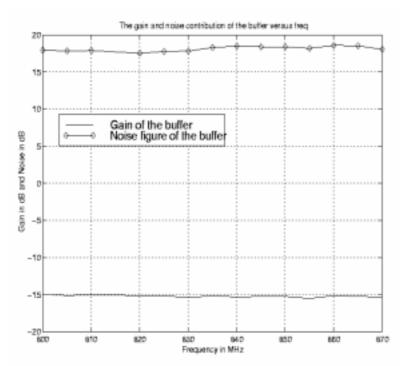

| 8.5 |         | Measurement Result of the buffer<br>ement Results of the two-stage and three-stage design                     | 133<br>134        |

|     | 8.5.1   | Two-stage measurement Results<br>Three-stage amplifier measurement results                                    | 134<br>135        |

## **CHAPTER 9** Conclusion

#### REFERENCES

Analog Research Laboratory

v

## List of Figures

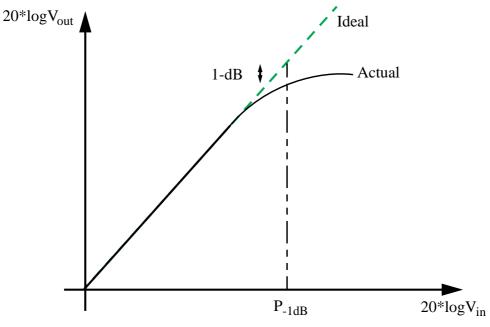

| Figure 2.1. | The plot of 1-dB compression point                                       | 9  |

|-------------|--------------------------------------------------------------------------|----|

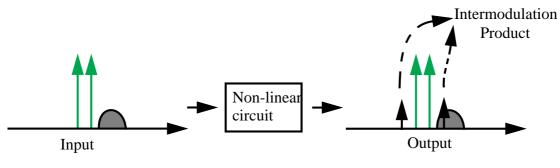

| Figure 2.2  | Illustration of the intermodulation product                              | 10 |

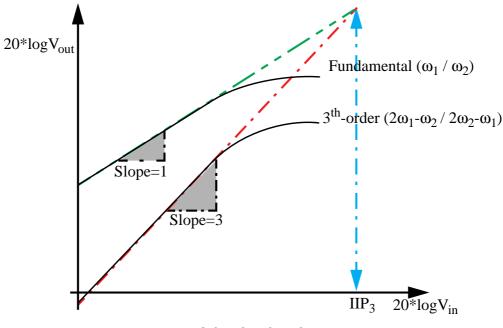

| Figure 2.3  | The plot of IIP <sub>3</sub>                                             | 10 |

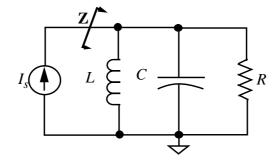

| Figure 2.4  | A general second-order parallel resonant circuit                         | 11 |

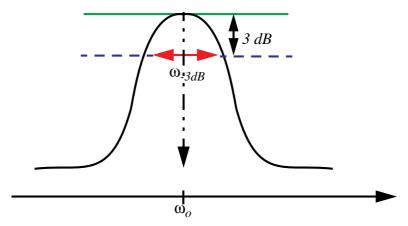

| Figure 2.5  | The frequency response of a bandpass transfer function                   | 12 |

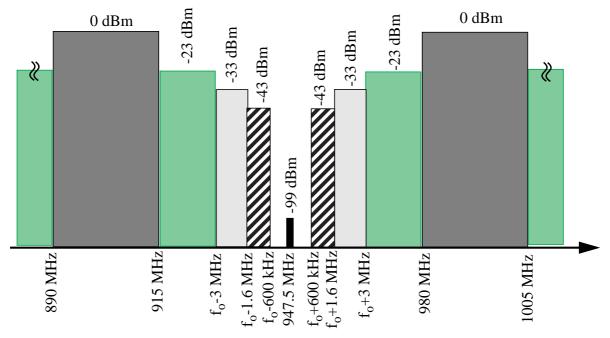

| Figure 2.6  | Blocking signals levels of the GSM Standard                              | 13 |

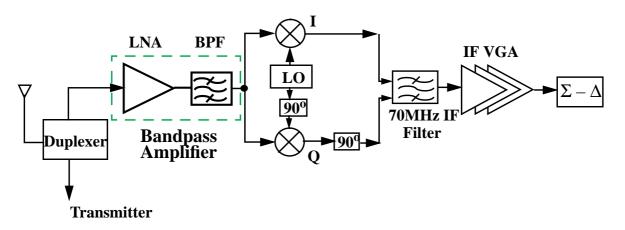

| Figure 2.7  | A superheterodyne receiver architecture with single IF and I & Q channel | 15 |

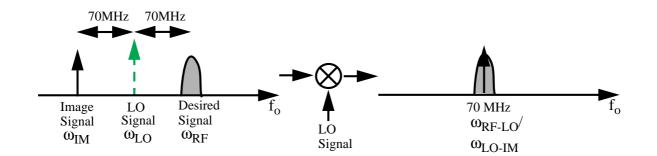

| Figure 2.8  | Illustration of the effect of image signal                               | 16 |

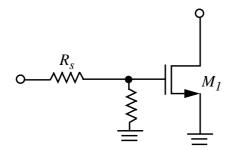

| Figure 3.1. | Input matching using 50- $\Omega$ resistor                               | 20 |

| Figure 3.2  | Input matching using common-gate configuration                           | 21 |

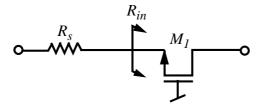

| Figure 3.3  | Input matching using inductive source degeneration                       | 22 |

| Figure 3.4  | The magnitude of the input matching under different inductor's Q         | 24 |

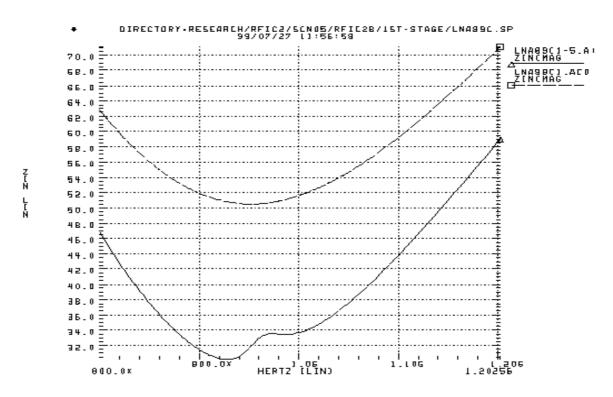

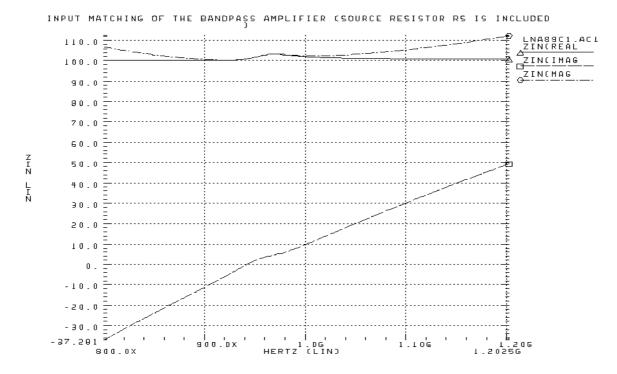

| Figure 3.5  | The simulated input matching of the amplifier                            | 26 |

A 900-MHz CMOS Bandpass Amplifier for GSM Receivers

| Figure 3.6  | The basic architecture of a common-cascoded LNA                                 | 26 |

|-------------|---------------------------------------------------------------------------------|----|

| Figure 3.7  | A parallel lossy LC circuit                                                     | 28 |

| Figure 3.8  | A complete inductor model                                                       | 30 |

| Figure 3.9  | General process information of a typical 0.8 µm CMOS (HP SCN26G)                | 31 |

| Figure 3.10 | A parallel LC resonant tank compensated with negative conductance               | 33 |

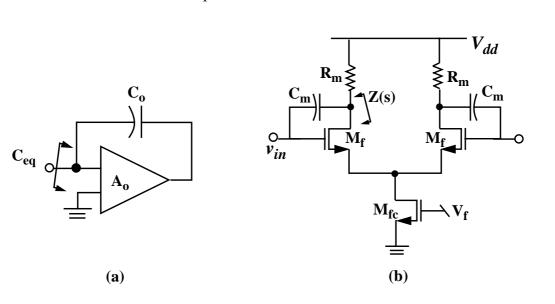

| Figure 3.11 | Q-compensation circuit                                                          | 35 |

| Figure 3.12 | Circuit diagram of impedance multiplication                                     | 36 |

| Figure 3.13 | Circuit diagram of Miller capacitance                                           | 38 |

| Figure 3.14 | The 50- $\Omega$ output buffer                                                  | 40 |

| Figure 3.15 | The gain and the noise figure of the output buffer                              | 42 |

| Figure 3.16 | The complete schematic of the bandpass amplifier                                | 42 |

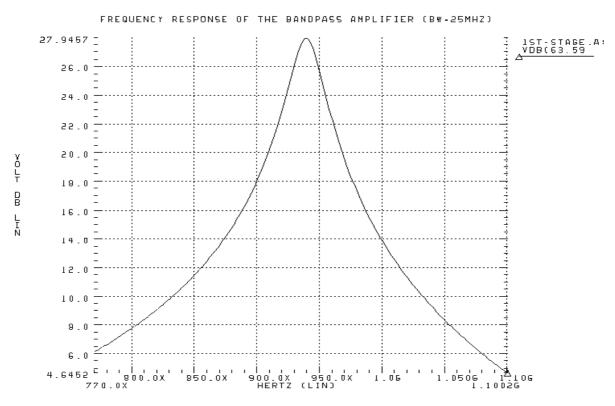

| Figure 3.17 | The simulated frequency response of the amplifier                               | 43 |

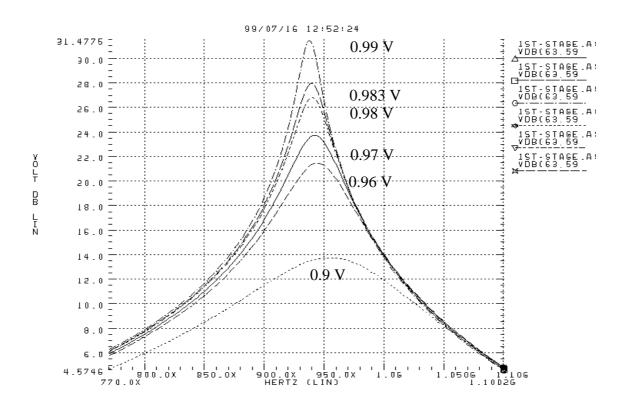

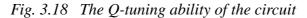

| Figure 3.18 | The Q-tuning ability of the circuit                                             | 44 |

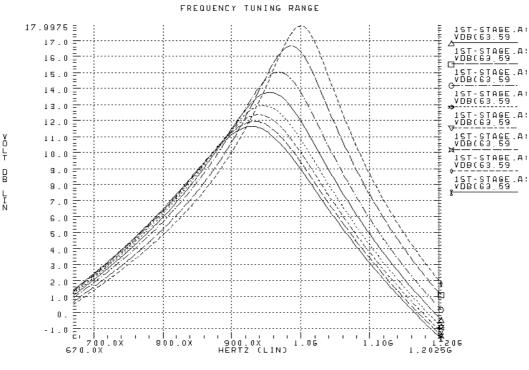

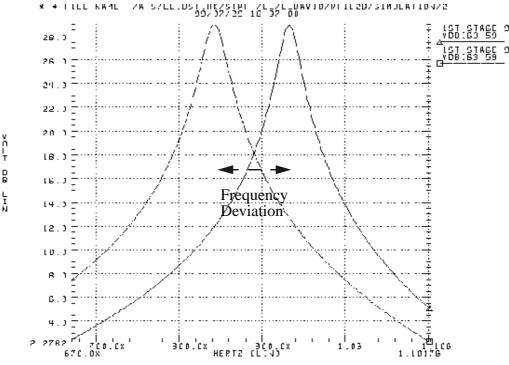

| Figure 3.19 | The frequency tuning ability of the circuit                                     | 44 |

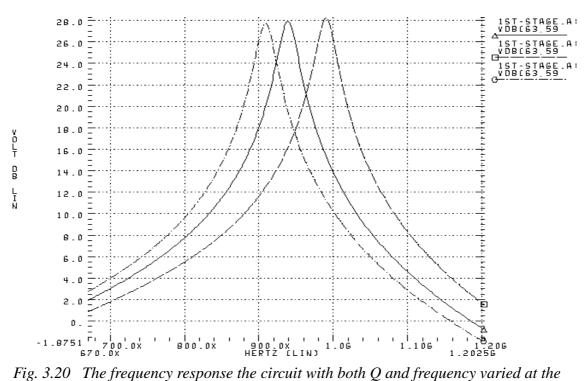

| Figure 3.20 | The frequency response the circuit with both Q and frequency varied at the same |    |

|             | time                                                                            | 45 |

| Figure 4.1. | Resistor thermal noise model                                                    | 47 |

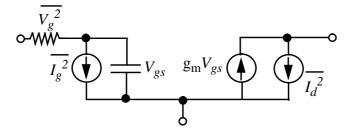

| Figure 4.2  | Complete transistor noise model                                                 | 48 |

| Figure 4.3  | The LNA including the resistive losses                                          | 48 |

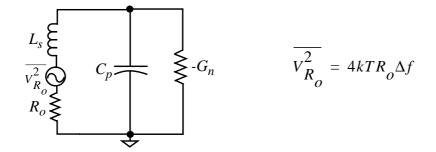

| Figure 4.4  | The output resonant tank                                                        | 50 |

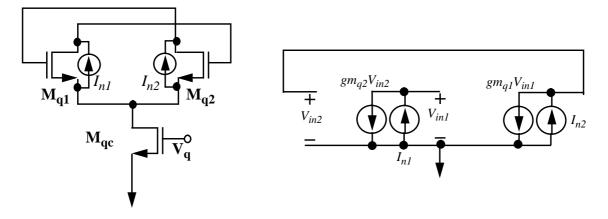

| Figure 4.5  | The small-signal analysis of the Q-compensation circuit                         | 51 |

| Figure 4.6 The frequency tuning circuit                                                           | 52    |

|---------------------------------------------------------------------------------------------------|-------|

| Figure 4.7 Noise Analysis of the output buffer                                                    | 53    |

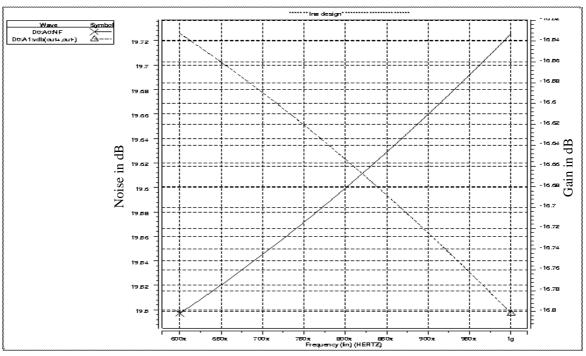

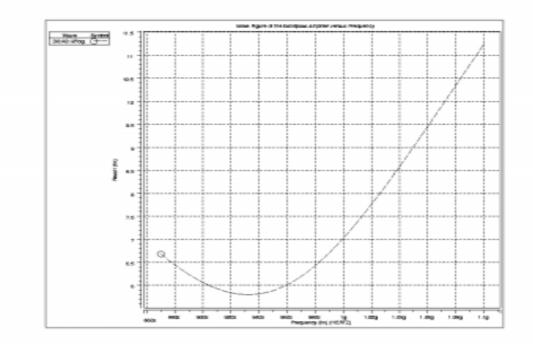

| Figure 4.8 The noise figure of the bandpass amplifier versus frequency                            | 55    |

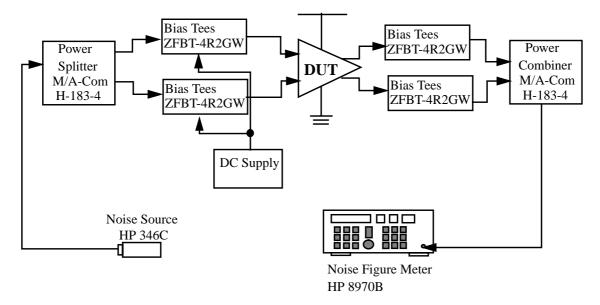

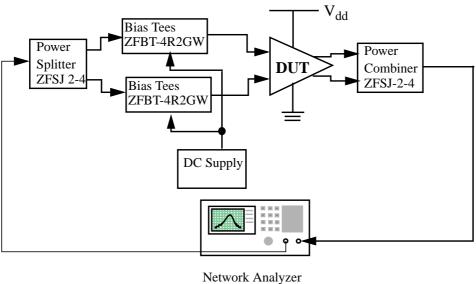

| Figure 4.9 Noise Figure Measurement Setup                                                         | 58    |

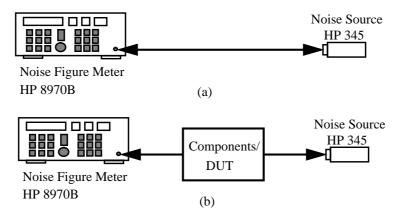

| Figure 4.10 (a). Calibration Setup; (b). Actual Measurement of the components                     | 59    |

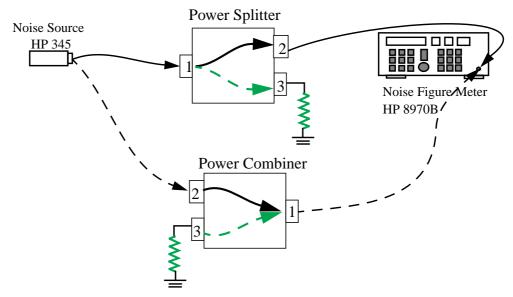

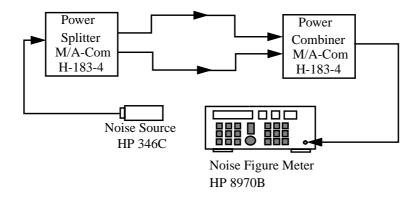

| Figure 4.11 (a). Measurement Setup for the power splitter / power combiner                        | 60    |

| Figure 4.12 Noise Figure Measurement Setup (Configuration 1)                                      | 62    |

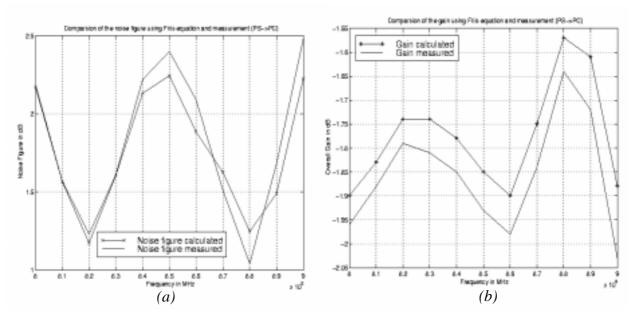

| Figure 4.13 Comparison of (a), the noise figure and (b), the gain between the measurement r       | esult |

| and the result based on Friis's equation (Configuration 1)                                        | 62    |

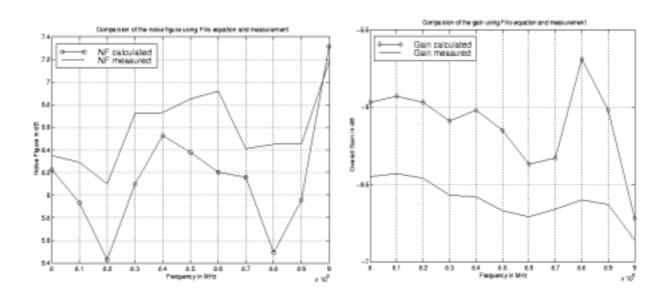

| Figure 4.14 Comparison of the noise figure and the gain between the measurement result an         | d the |

| result based on Friis's equation (Configuration 2)                                                | 63    |

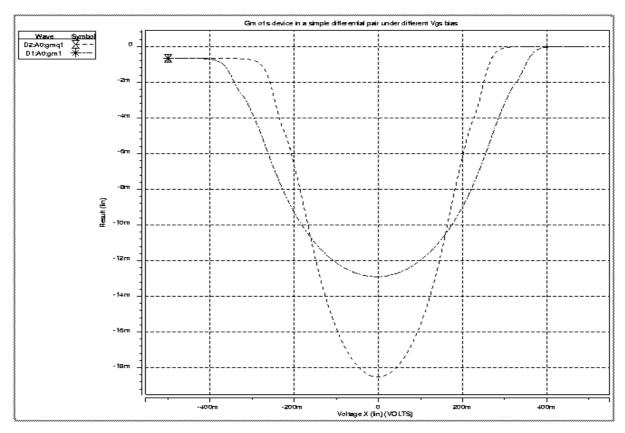

| Figure 5.1. The simulated $IIP_3$ of the bandpass amplifier using simple differential pair as the | ne Q- |

| compensation circuit                                                                              | 65    |

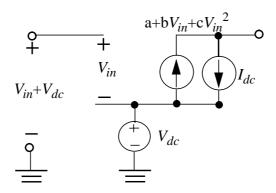

| Figure 5.2 The simplified Q-compensated bandpass amplifier                                        | 68    |

| Figure 5.3 The model of a gm-cell                                                                 | 69    |

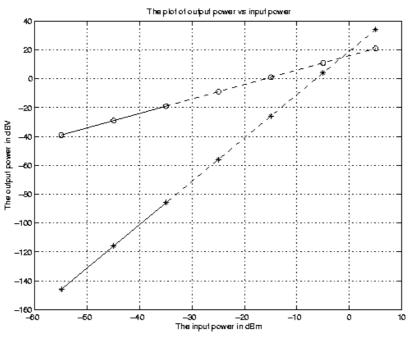

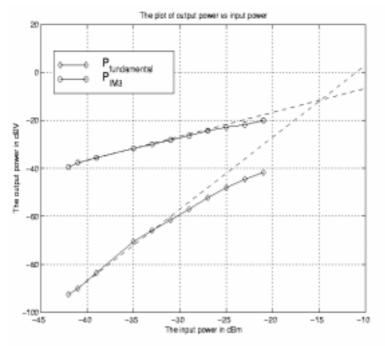

| Figure 5.4 The relationship between $P_{fund}$ , $P_{IM}$ and $P_{in}$                            | 70    |

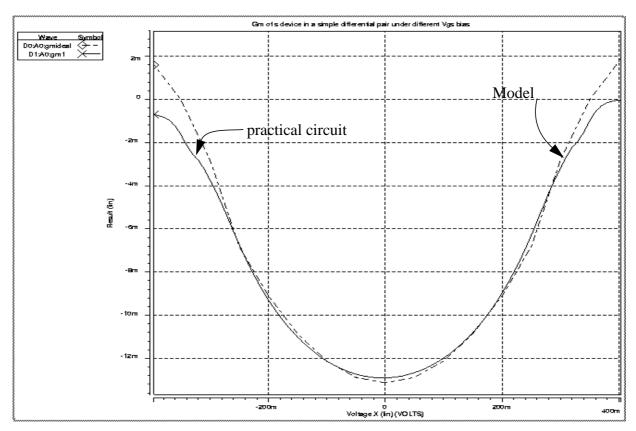

| Figure 5.5 The comparison of the modeled and actual gm value                                      | 71    |

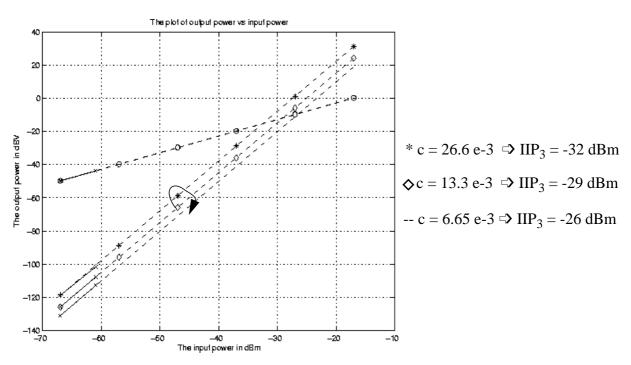

| Figure 5.6 The simulated $IIP_3$ of the bandpass amplifier with different degrees of non-linear   | rity  |

|                                                                                                   | 72    |

| Figure 5.7 A plot of the gm value versus input $V_{in}$ with different gate bias                  | 73    |

| Figure 5.8 Q-compensation with source degeneration                                                | 75    |

|                                                                                                   |       |

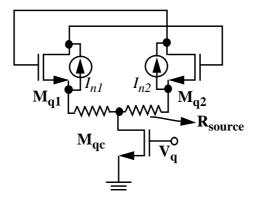

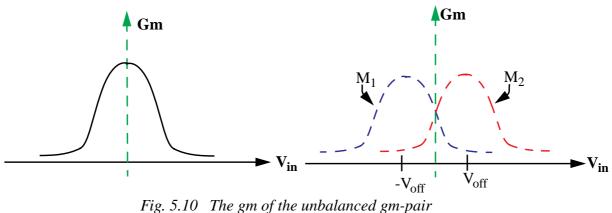

| Figure 5.9 The circuit diagram of an unbalanced gm-pair                                           | 76  |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 5.10 The gm of the unbalanced gm-pair                                                      | 76  |

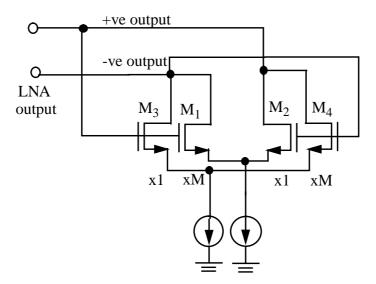

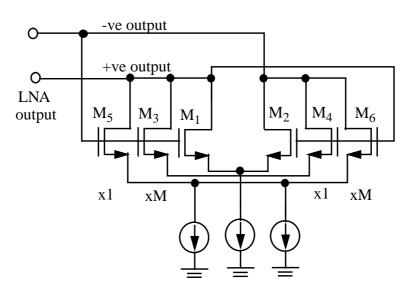

| Figure 5.11 The Q-compensation circuit with 2 pairs of unbalanced gm cells                        | 78  |

| Figure 5.12 Gm curves with and without unbalanced coupled pairs                                   | 80  |

| Figure 5.13 The relationship between fundamental output power, third-order intermodulation and    | nd  |

| input power                                                                                       | 81  |

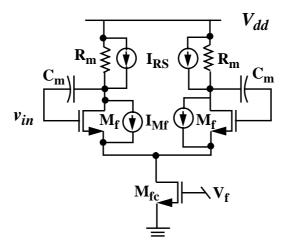

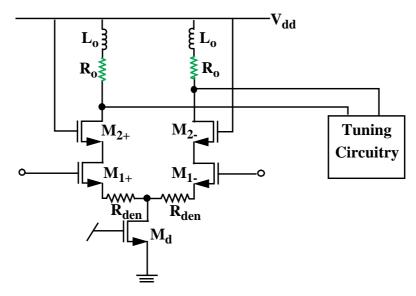

| Figure 6.1. The schematic of a bandpass filter                                                    | 84  |

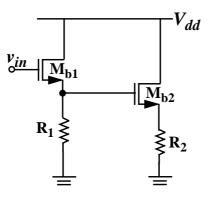

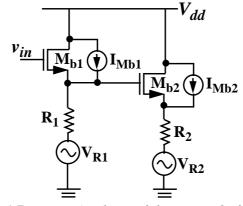

| Figure 6.2 The dc biasing circuit                                                                 | 85  |

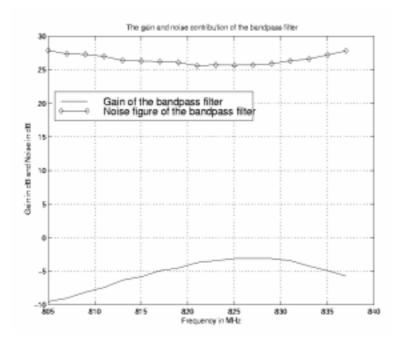

| Figure 6.3 The frequency response and the noise of the bandpass filter                            | 87  |

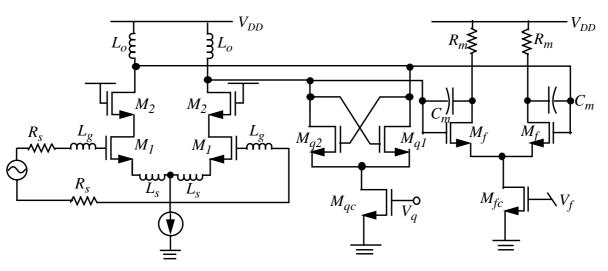

| Figure 6.4 Block diagram and schematic of the sixth order Bandpass Amplifier                      | 88  |

| Figure 6.5 A plot of the possible $Q_1$ and $Q_2$ that can achieve 25-MHz 3-dB BW                 | 90  |

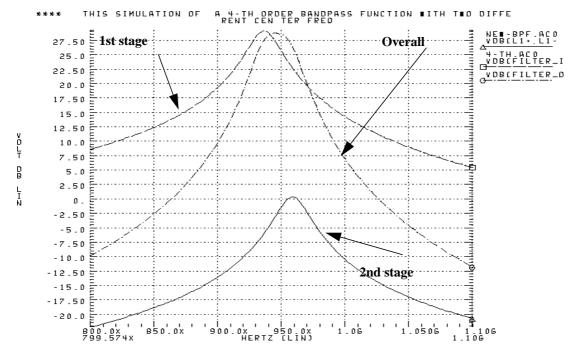

| Figure 6.6 The frequency response of the first stage, the second stage and the overall circuit    | 91  |

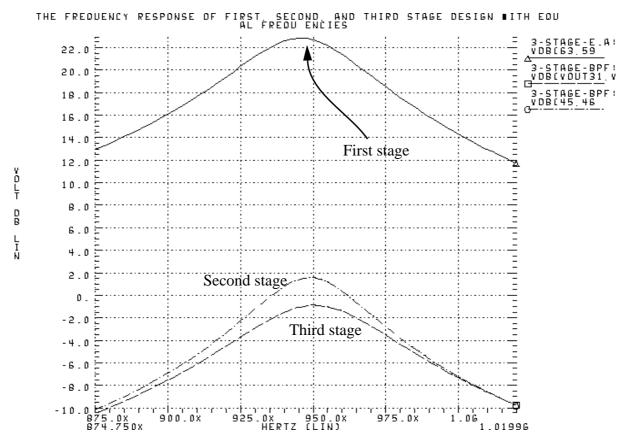

| Figure 6.7 The frequency response of the sixth-order bandpass amplifier                           | 93  |

| Figure 6.8 The frequency response of the sixth-order bandpass amplifier (with equal center free   | e-  |

| quencies                                                                                          | 94  |

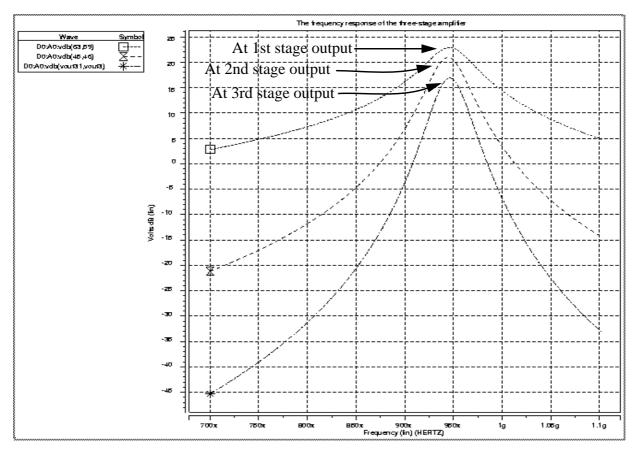

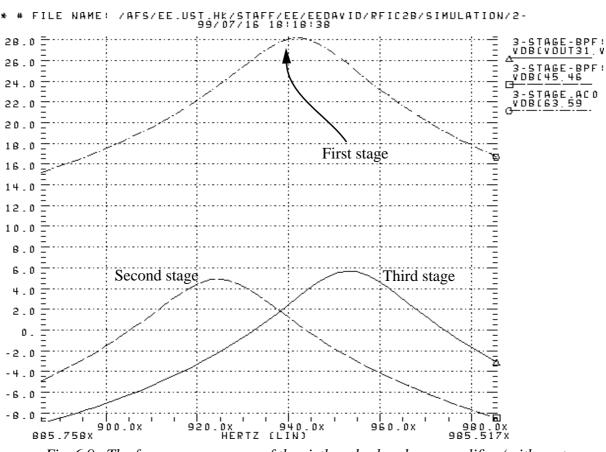

| Figure 6.9 The frequency response of the sixth-order bandpass amplifier (with center frequencies  | es  |

| of the three stages to be slightly different)                                                     | 95  |

| Figure 6.10 The frequency response of the sixth-order bandpass amplifier with unequal center fr   | re- |

| quencies                                                                                          | 96  |

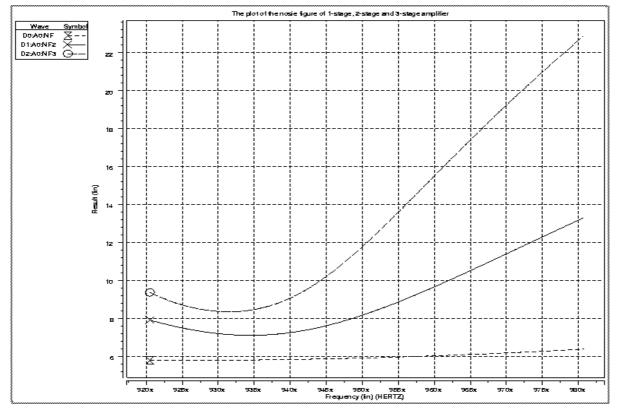

| Figure 6.11 The plot of the noise figure of 1-stage, 2-stage and 3-stage bandpass amplifier verse | us  |

| frequency                                                                                         | 97  |

|                                                                                                   |     |

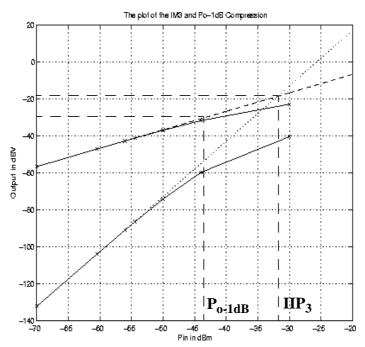

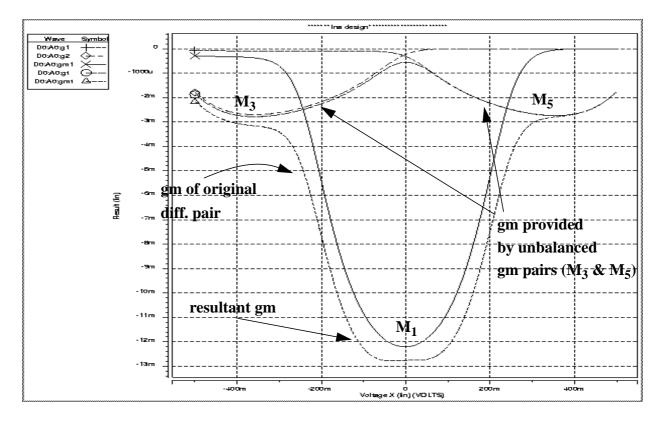

| Figure 6.12 | The IIP <sub>3</sub> and $P_{o-1dB}$ plot for the sixth-order bandpass amplifier | 99  |

|-------------|----------------------------------------------------------------------------------|-----|

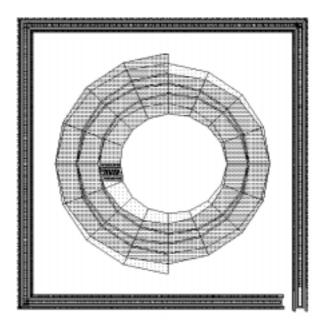

| Figure 7.1. | A two-layer output inductor                                                      | 104 |

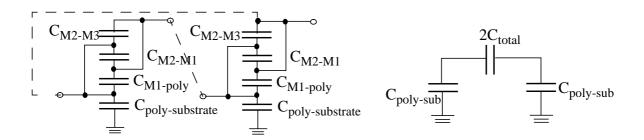

| Figure 7.2  | (a). The structure and (b) the schematic of a metal-to-metal capacitor           | 105 |

| Figure 7.3  | The optimal connection of 2 identical metal-to-metal capacitors                  | 106 |

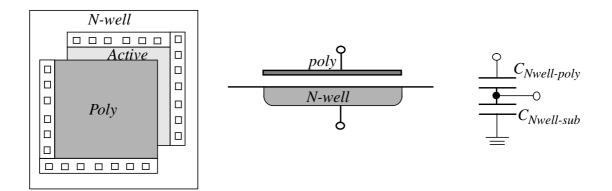

| Figure 7.4  | The structure of a linear capacitor                                              | 106 |

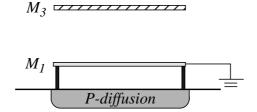

| Figure 7.5  | The pad structure for minimum noise                                              | 108 |

| Figure 7.6  | The floorplan of the bandpass amplifier                                          | 108 |

| Figure 7.7  | The floorplan of the bandpass filter                                             | 109 |

| Figure 7.8  | The layout of the bandpass filter                                                | 109 |

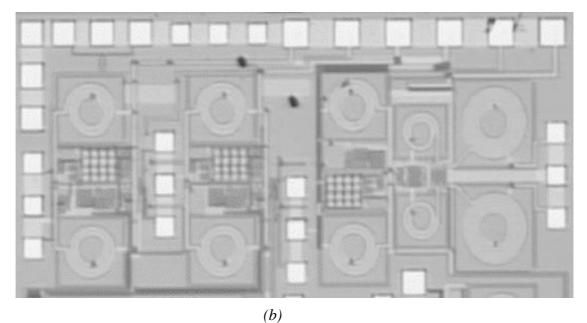

| Figure 7.9  | (a). Floor plan, and (b). Die-photo of the whole amplifier                       | 110 |

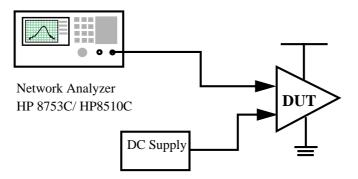

| Figure 8.1. | The test setup for high-frequency measurement                                    | 112 |

| Figure 8.2  | The measured frequency response of the amplifier                                 | 113 |

| Figure 8.3  | The measured frequency response of the circuit under different Q                 | 114 |

| Figure 8.4  | The measurement setup for the input matching                                     | 115 |

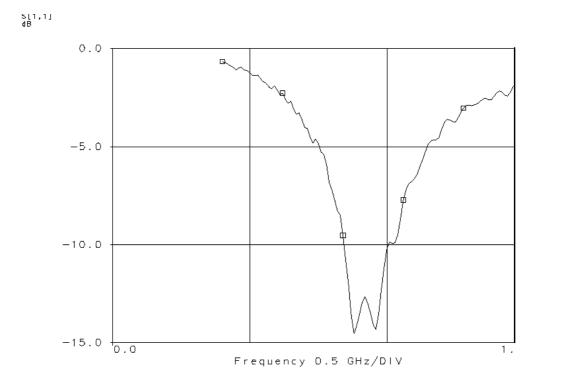

| Figure 8.5  | The measured input S <sub>11</sub> (log magnitude)                               | 115 |

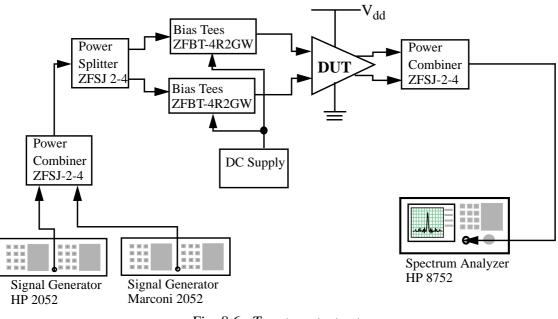

| Figure 8.6  | Two-tone test setup                                                              | 116 |

| Figure 8.7  | Measured result of the two-tone test                                             | 117 |

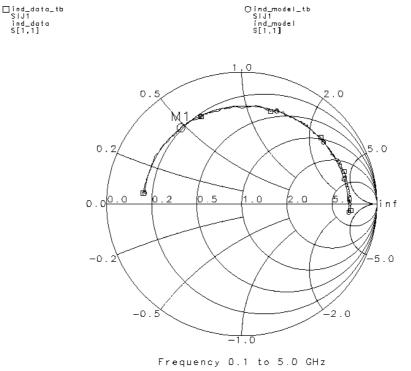

| Figure 8.8  | The measured $S_{11}$ of the two-layer output inductor                           | 119 |

| Figure 8.9  | The extracted model from the two-layer output inductor                           | 120 |

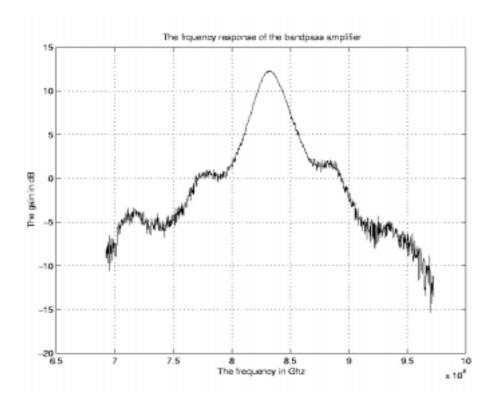

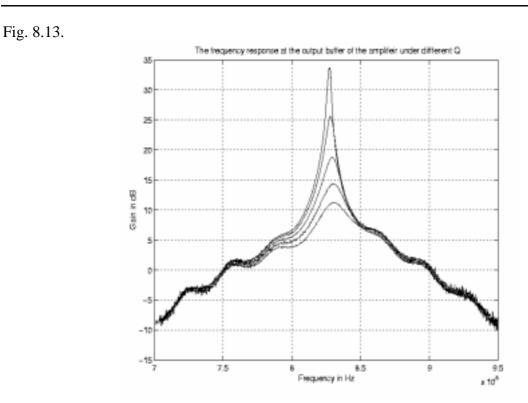

| Figure 8.10 | The measured frequency response of the bandpass amplifier                        | 121 |

| Figure 8.11 | The measured frequency response of the bandpass amplifier                        | 122 |

| Figure 8.12 | The re-simulated frequency response of the bandpass amplifier                  | 122    |

|-------------|--------------------------------------------------------------------------------|--------|

| Figure 8.13 | The measured frequency response of the bandpass amplifier with different 3-d   | В      |

|             | bandwidth                                                                      | 123    |

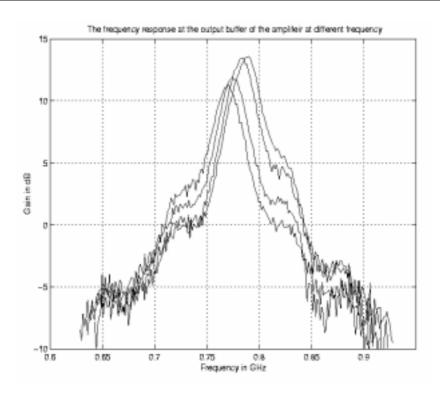

| Figure 8.14 | The measured frequency response of the bandpass amplifier with different frequ | ency   |

|             | tuning voltage                                                                 | 124    |

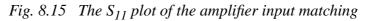

| Figure 8.15 | The S <sub>11</sub> plot of the amplifier input matching                       | 125    |

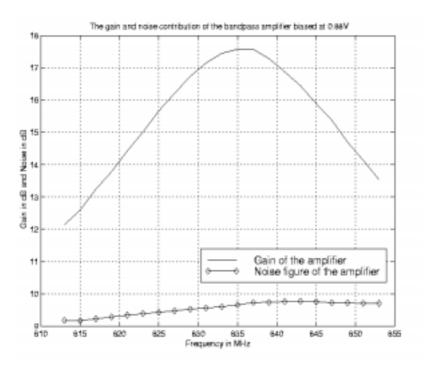

| Figure 8.16 | The noise figure of the amplifier with $BW = 25 MHz$                           | 125    |

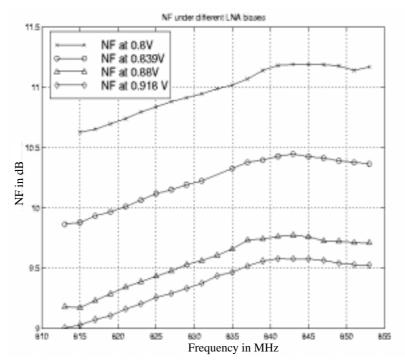

| Figure 8.17 | The noise figure of the amplifier under different biases                       | 126    |

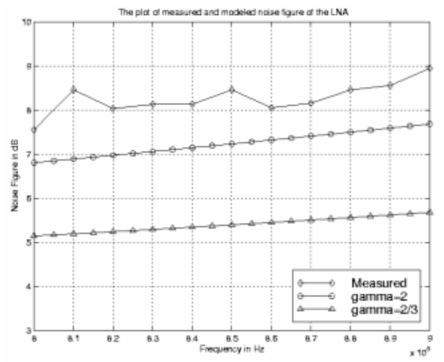

| Figure 8.18 | A comparison of the measured and modeled noise figure of the low-noise amp     | lifier |

|             |                                                                                | 127    |

| Figure 8.19 | A comparison of the measured and modeled noise figure of the bandpass ample    | ifier  |

|             |                                                                                | 128    |

| Figure 8.20 | Two tone test result                                                           | 129    |

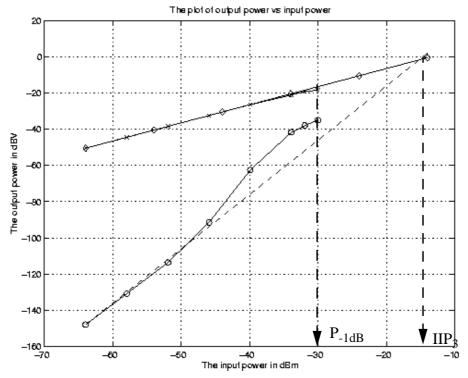

| Figure 8.21 | The plot of $P_{o,fund}$ and $P_{o,IM}$ versus $P_{in}$                        | 129    |

| Figure 8.22 | The frequency response of the first bandpass filter (2nd-stage)                | 130    |

| Figure 8.23 | Measured noise figure versus frequency of the first filter                     | 131    |

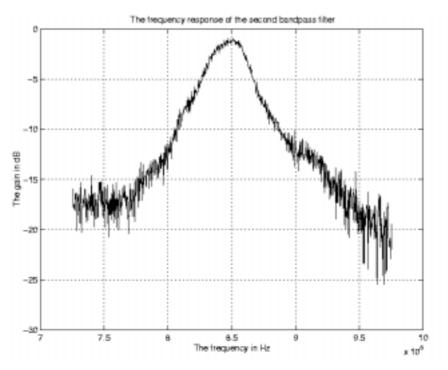

| Figure 8.24 | The frequency response of the second bandpass filter (3rd-stage)               | 132    |

| Figure 8.25 | Measured noise figure versus frequency of the second filter                    | 132    |

| Figure 8.26 | The noise figure and the gain of the output buffer                             | 133    |

| Figure 8.27 | The frequency response of the two-stage amplifier                              | 134    |

| Figure 8.28 | The noise figure of the two-stage amplifier                                    | 135    |

|             |                                                                                |        |

| Figure 8.29 | The plot of $P_{o, fund}$ and $P_{o, IM}$ versus $P_{in}$ (Two-stage) | 136 |

|-------------|-----------------------------------------------------------------------|-----|

| Figure 8.30 | The frequency response of the three-stage amplifier                   | 136 |

| Figure 8.31 | The plot of $P_{IM,3}$ and $P_{fund}$ versus $P_{in}$ (Three-stage)   | 137 |

## List of Tables

| Table 3.1 | General specifications of a LNA in super-heterodyne systems                             | 18  |

|-----------|-----------------------------------------------------------------------------------------|-----|

| Table 3.2 | Modified Requirement for the bandpass amplifier                                         | 19  |

| Table 3.3 | The parameters in the 50- $\Omega$ output buffer                                        | 41  |

| Table 4.1 | The distribution of the noise of each building block                                    | 54  |

| Table 4.2 | The major designed parameters for the bandpass amplifier                                | 55  |

| Table 4.3 | The decomposition of the calculated and simulated noise figure of the amplifier         | 56  |

| Table 5.1 | The size of the modified Q-tuning circuit                                               | 80  |

| Table 5.2 | The comparison of three different linearization techniques                              | 80  |

| Table 6.1 | The gain, center frequency and the Q distribution among the three stages                | 92  |

| Table 6.2 | Information at the output of the first, second and the third stage with equal center fi | re- |

|           | quencies                                                                                | 93  |

| Table 6.3 | The gain, center frequency and the Q distribution among the three stages                | 94  |

| Table 6.4 | The gain, the center frequency and the image rejection of using single, two and three   | ee  |

A 900-MHz CMOS Bandpass Amplifier for GSM Receivers

|           | stage design                                                                      | 96  |

|-----------|-----------------------------------------------------------------------------------|-----|

|           |                                                                                   |     |

| Table 6.5 | The corresponding noise figure of the single, two and three stage design          | 98  |

| Table 7.1 | Comparison between single-layer and two-layer inductors                           | 102 |

| Table 7.2 | The capacitance per unit area for two types of capacitor                          | 104 |

| Table 8.1 | The comparison between simulation and measurement results                         | 117 |

| Table 8.2 | A comparison of the parameters of the two-layer inductor obtained from simulation | and |

|           | measurement                                                                       | 120 |

| Table 8.3 | the designed and measured inductance and capacitance value                        | 121 |

| Table 8.4 | The performance of the bandpass amplifier and the two filters                     | 131 |

| Table 8.5 | The distribution of the design parameters in the first and the second stage       | 134 |

| Table 8.6 | The distribution of the design parameters in each of the three-stage design       | 135 |

| Table 8.7 | The measured results of the single, the two and the three-stage design            | 137 |

## Chapter 1

## Overview

## **1.1 Motivation**

The recent upsurge in the demand for low-power portable wireless communication products creates a lot of research opportunities in both system design and hardware implementation. Some of the popular applications include mobile phones, pagers, wireless LANs (local area networks), RFIDs (radio frequency identification systems). In the past decades, radiofrequency (RF) circuits were dominated by GaAs and silicon bipolar technologies, which exhibit much higher unity-gain frequencies ( $f_t$ ), higher device transconductance (gm) and better noise performance than complementary metal-oxide-semiconductor (CMOS) counterparts. Because the components implemented in these technologies were incompatible with the digital integrated circuits that were usually realized in CMOS domains, wireless systems often comprise several ICs and many discrete components. As a result, the size and the power dissipation of these applications are inevitably large.

Meanwhile, the advancement in digital sub-micron CMOS technology and the continuous

down scaling in CMOS device size have made low-cost and small-size implementation of CMOS RF integrated circuits (ICs) more and more feasible. As digital CMOS technology is known for its low-power dissipation and high density, it provides an attractive solution for integrating analog RF front-end with digital baseband back-ends in a single chip.

### **1.2 Technical Challenges**

Even though CMOS technology has provided a lot of attractions, there are still many technical hurdles needed to be overcome before monolithic integration of a transceiver is possible. The realization of some RF circuits in CMOS technology, including low-noise amplifiers (LNAs) [2], image-reject mixers [6] and voltage-controlled oscillators (VCOs) [7] [8] have been demonstrated in recent literatures. These circuits have comparable performance in terms of linearity, power consumption and noise to those implemented in GaAs and bipolar technologies. Nevertheless, passive on-chip elements, such as inductors and resistors have poor quality and large process variations, and thus some of the key components in a wireless receiver, for example, image-reject filters and intermediate-frequency (IF) channel selection filters, are still usually found to be off-chip.

On-chip planar inductors emerge in CMOS substrate for more than a decade yet their quality factor Q is so low that they were not used in practical circuits, e.g. LNAs, LC-oscillators, until recent years. The low Q is resulted from the highly resistive lossy substrate, which increases high-frequency resistive losses through the lossy substrate [20]. Recently, improvement has been made in reducing the losses of spiral inductor's by etching away the lossy substrate [27], inserting ploy-Si shielding [11], or using highly-conductive copper interconnecting layers [10].

Nonetheless, these methods are not commercially compatible with mainstream digital CMOS technology. The maximum achievable Q of planar inductors in modern CMOS technology is usually less than ten and more commonly less than five.

### **1.3 Research Goals**

The implementation of a single chip wireless transceiver [3] [27] [33] [34] [35] is still one of the hottest research topics in Radio Frequency Integrated Circuit (RFIC) design. Although many obstacles need to be circumvented, recent publications have demonstrated the possibility to implement the RF circuits and the RF front-ends in standard CMOS technology. As a result, it is worthwhile to devote effort to explore the area.

LNAs and especially RF image-reject filters are usually implemented either off-chip or with incompatible hybrid technologies. It is not until recently found that they can be constructed in CMOS technology with some reasonable performance [14] [16]. This thesis explores the design of a bandpass amplifier [5], which can be considered as a Q-enhanced low noise amplifier. It not only amplifies the received signal as a LNA but also helps in rejecting the blocking signals outside the 25-MHz receiver band. It is realized with a compensation circuit to improve the overall Q of the output resonant circuit. The details will be discussed in depth later. Because the Q is enhanced, the image rejection of the bandpass amplifier is also improved and it helps to share the burden of the image-reject filter. Accordingly, the implementation of the image-reject filter on CMOS technology becomes more feasible. As a part of the research work, a RF bandpass filter is designed and cascaded with the original bandpass amplifier in an attempt to provide enough image rejection at the image frequency so that the off-chip image-reject filter can be eliminated.

## **1.4 Thesis Outline**

As an introduction, some important receiver specifications that are related to the design of the bandpass amplifier are reviewed in Chapter 2, and the RF fundamentals such as linearity, noise figure and sensitivity are defined as well.

Chapter 3 covers the basic LNA design and tuning circuits. Different types of input matching, the working principles of the resonant circuit, Q-compensation and frequency tuning circuit. Simulation results are also included to demonstrate the functionality.

To optimize the design in terms of noise, power and linearity, a detailed noise analysis of the bandpass amplifier including tuning circuits are presented in Chapter 4. The analysis provides some hints on optimizing the noise figure of the complete circuit.

The linearity of the bandpass amplifier is much lower than that of typical LNAs due to the Q-compensation circuitry. In Chapter 5, origins of the non-linearity of the circuit are explained. Different type of linearization methods are addressed in terms of their pros and cons. To improve the bandpass amplifier's poor linearity, a proposed linearized circuit is explained and simulation results are presented as well.

Chapter 6 first describes the design of a simple second-order LC filter. Then, the general design of a three-stage, sixth-order bandpass amplifier that is realized by cascading a bandpass amplifier and two second-order bandpass filters, is presented. Design issues such as the allocation of the gain, the center frequency and the quality factor among the three stages are also mentioned

Layout consideration regarding to the bandpass amplifier and bandpass filter are presented in Chapter 7. Furthermore, measurement results are discussed in Chapter 8. Finally, a conclusion is summarized in Chapter 9.

## Chapter 2

## **RF** Fundamentals

#### **2.1 Introduction**

This chapter provides some general background to facilitate the discussion of the bandpass amplifier. Firstly, important parameters for evaluating the performance of LNA will be described. Then, a brief review of the GSM receiver standard and how the specification of the standard affects the design of the amplifier will be addressed.

#### **2.2 Basic RF Fundamentals**

In this section, we will explore some of the useful parameters for RF receivers and individual RF circuit designs, namely, sensitivity, noise figure, linearity,  $IIP_3$  and 1-dB compression point.

#### 2.2.1 Sensitivity

To measure how well a RF circuit can pick up the weak signal from a noisy frequency spectrum, sensitivity is defined as the minimum signal level that a circuit can detect with certain signal-to-noise ratio (SNR). Quantitatively, sensitivity is usually measured in terms of the minimum detectable signal (MDS) that a circuit or a system can detect and demodulate correctly. The minimum detectable signal (P<sub>in,min</sub>) can be expressed as

$$P_{in, min} = P_{Rs} + NF + 10\log B_c + SNR_{min}, \qquad (2.1)$$

where  $P_{Rs}$  is the source resistance noise power, NF is the noise figure of a system,  $SNR_{min}$  is the minimum acceptable signal-to-noise ratio and B is the bandwidth of the system. It should be noted that all the quantities are in dB scale.

For a 50- $\Omega$  source resistance, the source resistance noise power  $P_{Rs}$  is

$$P_{Rs} = \frac{4kTR_s}{4} \frac{1}{R_s}$$

$$= -174 \ dBm/Hz.$$

(2.2)

Other than  $P_{Rs}$ , the other three quantities vary with different systems. For GSM standard, with a channel bandwidth ( $B_c$ ) of 200 kHz, noise figure (NF) of 9 dB and  $SNR_{min}$  of 10 dB, MDS can be calculated as -102 dBm.

#### 2.2.2 Noise Figure (NF)

The signals received at the antenna most likely are very weak and have to be amplified in order to drive the mixer. So as not to further deteriorate the SNR of the received signal, the circuits afterwards should be designed to add as small noise as possible especially at the front end of the receiver. Noise figure is a measure of the amount of noise added after the signal goes through a circuit and it is defined as the ratio of the available output noise power to available output noise due to the source (a 50- $\Omega$  impedance),

$$F = \frac{S_i / N_i}{S_o / N_o} = \frac{SNR_{in}}{SNR_{out}}.$$

(2.3)

$$F = \frac{S_i (N_i G + N_c, o)}{N_i G} = 1 + \frac{N_c, o}{N_i G} = 1 + \frac{N_c, i}{N_i}, \qquad (2.4)$$

where  $N_{c,i}$  and  $N_{c,o}$  are circuit's input-referred and output-referred noise, respectively. G is the gain of the circuit and  $N_i$  is the source noise power. Noise Figure (NF) is usually expressed in log scale (dB) and the noise factor is the corresponding value in linear scale. In this dissertation, the noise performance is evaluated in terms of noise figure. The relationship between noise figure (NF) and noise factor (F) are as follows:

$$NF(in \ dB) = 10 \bullet \log F . \tag{2.5}$$

#### 2.2.3 Linearity

As the frequency spectrum is limited, an ISM frequency band usually assigns with more than one applications, it is likely that the received signal is close to a strong interferer. This situation is more severe if the received signal is already weak when it reaches at the antenna. Desensitization and blocking phenomenon occurs. This is due to the non-linear property of active devices.

Ideally, the input-output relationship of a linear, time-invariant system can be modeled as

$$y(t) = a_1 x(t)$$

, (2.6)

where x(t) and y(t) are the input and output of the non-linear system, But, due to non-linearity, the system input-output relationship si modified to be

$$y(t) = a_1 x(t) + a_2 x^2(t) + a_3 x^3(t) + \dots$$

, (2.7)

The coefficients  $a_2$ ,  $a_3$  provide information on the non-linearity of a device or a circuit. When a sinusoidal signal Acos $\omega t$  is applied to the system in Eq. (2.7), the output y(t) would be

$$y(t) = \frac{a_2 A^2}{2} + \left(a_1 + \frac{3a_3 A^2}{4}\right) A\cos\omega t + \frac{a_2 A^2}{2}\cos 2\omega t + \frac{a_3 A^3}{4}\cos 3\omega t.$$

(2.8)

From Eq. (2.8), the output contains not only the fundamental frequency term, but also many higher order harmonics caused by  $x^2(t)$  and  $x^3(t)$ . Typically, high-order terms are negligible. However as the input amplitude becomes large enough, their effects become to affect the output significant. If the circuit is implemented in fully-differential architecture, the even-order harmonics can usually be neglected. Among the high-order harmonics, the most troublesome the third-order. Several important parameters that affect the performance of analog and RF circuits are now described.

#### 2.2.3.1 1-dB compression point

1-dB compression point is defined as the input signal amplitude at which the output of the signal deviates from the ideal response by 1-dB, and it is depicted in Fig. 2.1. In Eq. (2.7), the first-order coefficient includes two terms, the desired gain  $a_1$ , and the undesired term  $3a_3A^3/4$ . For small input amplitude A, the first term dominates and the output is linearly dependent on the input. However, due to non-linearity, when the input signal amplitude is large, the gain of the fundamental frequency begins to diminish because  $a_1$  and  $a_3$  are usually of opposite sign; thus, the term  $a_1A$  and  $3a_3A^3/4$  cancel each other. The typical 1-dB compression point of a MOSFET device occurs at around -20 to -25 dBm.

A 900-MHz CMOS Bandpass Amplifier for GSM Receivers

Fig. 2.1 The plot of 1-dB compression point

#### 2.2.3.2 Third-order Intermodulation Distortion

Another key parameter to evaluate the linearity of a circuit is intermodulation distortion. When two closely spaced signals mix with each other, they produce signals with frequencies other than the high-order harmonics of the two signals. The most severe distortion is called third-order intermodulation due to the non-linear  $x^3$  term. If the two signals are  $A_1 \cos \omega_1 t$  and  $A_2 \cos \omega_2 t$  are applied to a system like Eq. (2.7), the output will consist of frequency terms  $\cos \omega_1 t$ ,  $\cos \omega_2 t$ ,  $\cos(2\omega_1+\omega_2)t$  and  $\cos(2\omega_1-\omega_2)t$ . Intermodulation causes trouble when a weak signal is closed to two strong interferer shown in Fig. 2.2. At the desired signal frequency, the amplitude of the intermodulation product sometimes is much larger than that of the signal. As a result, the desired signal is corrupted. The third order intermodulation (IM) can be measured by applying two tones  $A\cos\omega_1 t$  and  $A\cos\omega_2 t$  at the input of the circuit, the amplitude of the intermodulation product is measured at the output of the circuit. A plot of the output signal versus the input signal of both

Fig. 2.2 Illustration of the intermodulation product

fundamental and intermodulation product frequency is in logarithmic scale is shown in Fig. 2.3.

Fig. 2.3 The plot of IIP<sub>3</sub>

The third-order IM product increases at a rate of 3 while the fundamental frequency increases at a rate of 1. Third-order intermodulation product ( $IP_3$ ) is used to measure the distortion, which occurs when the third-order IM product equals the fundamental signal amplitude. Indeed, it does not occur in practical due to the compressive nature of the circuit. The

IP3 is calculated by extrapolating both components until they finally intercept with each other. The input-referred IP<sub>3</sub> is called IIP<sub>3</sub>. The IIP<sub>3</sub> can be calculated as

$$IIP_{3} = \frac{P_{out} - P_{out, IM3}}{2} + P_{in},$$

(2.9)

where  $P_{out}$  is the fundamental output power,  $P_{out,IM3}$  is the output IM<sub>3</sub> power and  $P_{in}$  is the input power.

#### 2.2.3.3 Desensitization and Blocking

Blocking occurs when the weak signal is accompanied by a strong interferer that is closed to the received signal, from other wireless applications or other users. This interferer reduces the overall gain of the circuit. As a result, the weak signal received will experience a smaller gain, and this is termed as desensitization. When the interferer's signal amplitude is large enough to reduce the overall gain of the circuit to zero, the phenomena is known as blocking.

#### **2.2.4 Quality Factor (Q-Factor)**

Before discussing the quality factor, a simple parallel RLC circuit in Fig. 2.4 is considered. It can readily be proved that the impedance Z(s) is

Fig. 2.4 A general second-order parallel resonant circuit

$$Z(s) = \frac{s/C}{s^2 + s/RC + 1/LC}$$

=  $\frac{sk}{s^2 + s\omega_{-3dB} + \omega_o^2}$

=  $\frac{sk}{s^2 + s\frac{\omega_o}{Q} + \omega_o^2}$ , (2.10)

where k is a constant,  $\omega_o = 1/LC$  and  $\omega_{-3dB} = 1/RC$ .  $\omega_o$  is the resonant frequency, which is defined as the frequency at which the imaginary part in Eq. (2.10) vanishes.  $\omega_{-3dB}$  is the 3-dB bandwidth of the transfer function. The frequency response is given in Fig. 2.5.

Fig. 2.5 The frequency response of a bandpass transfer function

The ability of a bandpass circuit to reject the out-of-band signals is termed as selectivity. It is usually expressed in terms of quality factor Q,

$$Q = \left(\frac{\omega_o}{\omega_{-3dB}}\right). \tag{2.11}$$

It is equal to the ratio of the resonant frequency to 3-dB bandwidth. The higher is the quality factor, the smaller is the 3-dB bandwidth and the better is the selectivity. Furthermore, the

roll-off of the second-order transfer function in Eq. (2.10) outside frequencies outside the band is 20 dB/decade, i.e. if the 3-dB bandwidth of the response is 25 MHz, the attenuation at 140 MHz away from the resonant frequency is around 18 dB.

#### 2.3 GSM standards and System architecture

Global System for Mobile Communications, or GSM for short, is one of the most widely used wireless communications standard over the past decades. The standard also imposes one of the hardest specifications to be met by system and circuit designers. The frequency band assigned for GSM applications has been divided into two portions, namely the transmitter band (895 - 915 MHz) and the receiver band (935 -960 MHz). The blocking signal levels in the GSM standard are illustrated in Fig. 2.6. The input and output impedance of RF circuits is often  $50-\Omega$  matched to

Fig. 2.6 Blocking signals levels of the GSM Standard

provide maximum power transfer and RF signals are usually expressed in terms of dBm or dBV.

14

The definitions of these two units are presented here as

$$dBm = 10\log\frac{(Power \ in \ W)}{1mW} \tag{2.12}$$

and

$$dBV = 20\log\left(\frac{V_{rms}}{1V_{rms}}\right).$$

(2.13)

1 dBm is 13 dB larger than 1 dBV.

Different receiver architectures have their own strength and weaknesses. Direct conversion is the simplest architecture, however, it suffers from many problems e.g. dc offset and even-order harmonics. Super-heterodyne structure is better than direct conversion in these aspects. On the other hand, the implementation requires a lot of highly selective passive components like image-reject filters and channel-selection filters that make monolithic integration of the receiver very difficult. To fulfill the ultimate goal of a single-chip receiver or even a transceiver, several key components such as LNAs, mixers and frequency synthesizers are designed as part of a GSM receiver with single-IF (70 MHz) superheterodyne architecture. The system is shown in Fig. 2.7.

The discussion here is focused on the design of LNA or bandpass amplifier.

Fig. 2.7 A superheterodyne receiver architecture with single IF and I & Q channel

#### 2.3.1 Minimum and Maximum Tolerable Signals

Minimum detectable signal (MDS) specified as -102 dBm within the 25 MHz GSM receiver band. For maximum signal level, 0 dBm blocking signals at frequency below 915 MHz and above 980 MHz pose stringent requirements on the linearity of the LNA. Even though a duplexer is often inserted in front of a LNA in a transceiver, the blocking signals can at most be attenuated by about 25 dB. It implies that the LNA's 1-dB compression point needs to be much larger than -25 dBm.

#### 2.3.2 Noise Figure

As mentioned in 2.3.1, the MDS of the GSM standard is -102 dBm. The signal-to-noise ratio (SNR) is at least 9 dB to achieve a bit error rate (BER) <  $10^{-4}$ . Meanwhile, the noise spectral density of the antenna (50- $\Omega$  matched) or a 50- $\Omega$  source resistor at 290K is -174 dBm (4kT(50)) and the channel bandwidth (B<sub>c</sub>) is 200 kHz. Thus, the minimum noise floor is -121 dBm. The

noise figure is related to the minimum input signal by

$$P_{in,min} = -174 \text{ dBm/Hz} + \text{NF} + 10\log B_c + \text{SNR}$$

(2.14)

The maximum system noise figure (NF) can be calculated from Eq. (2.14) as 9 dB. The noise contribution of all the stages after the LNA is usually large in our design, but due to the large gain of the LNA, the equivalent input-referred noise is small compared to the LNA noise. As a consequence, the noise figure of the LNA is set to be around 6 dB to leave 3 dB margin for later stages.

#### 2.3.3 Image Rejection

Due to the limited frequency spectrum that can be used in wireless communications, radio receivers must be able to select the weak signal from the strong interfering signals which lie close to the receiver band. As a result, image rejection is a very important parameter to evaluate the performance of a radio receiver. Without loss of generality, let us assume that a low-sideband conversion is employed, i.e. the local oscillator (LO) frequency is 70 MHz (IF frequency) lower than the desired signal ( $\omega_{RF}$ ). As illustrated in Fig. 2.8, there usually exists undesired signals located at 70 MHz below the LO frequency referred to as image frequency ( $\omega_{LO}$ ). Due to the

Fig. 2.8 Illustration of the effect of image signal

mixing, both the desired and image signals shown in Fig. 2.8 modulate with the LO  $(\sin\omega_{LO}t)$ signal and produce frequency components including  $\sin(\omega_{RF}+\omega_{LO})t$ ,  $\sin(\omega_{RF}-\omega_{LO})t$ ,  $\sin(\omega_{LO}+\omega_{IM})t$  and  $\sin(\omega_{LO}+\omega_{IM})t$ . In this case, the frequency components  $\sin(\omega_{RF}-\omega_{LO})t$  and  $\sin(\omega_{LO}+\omega_{IM})t$  coincide and cannot be separated after mixing. If the image signal is large enough, the modulated image signal corrupts the desired signal and degrades the SNR. Therefore, the image signal needs to be attenuated before entering the mixer.

As an example, the image rejection (IR) of a GSM receiver with single IF being at 70MHz is calculated. The blocking signal level (Fig. 2.6) at 140 MHz away from the receiver band is -23 dBm and the MDS of the GSM standard is -102 dBm. To achieve a 9 dB SNR ratio of the whole system, the blocking signals need to be smaller than the MDS by at least 9 dB. Therefore, the attenuation of the image signal at 140 MHz away from the desired signal should be equal to IR = -23 - (-99) + 9 = 85 dB. This value of image rejection is very difficult to be achieved with today's receiver architecture, not to mention a single-chip implementation.

In the GSM receiver architecture shown in Fig. 2.7, in-phase (I) & quadrature-phase (Q) channels have been employed to provide some image rejection for the whole system. Owing to the amplitude and phase mismatches of the I and Q channels, typically within 1 dB and 1<sup>o</sup> respectively, the image rejection achieved is at most 35 to 40 dB. To maintain 80 dB image rejection, the combination of LNA and RF image rejection filter must be able to provide the remaining 40 dB attenuation at the image frequency.

# Chapter 3

# Design of Low-Noise Amplifier (LNA) and Bandpass Amplifier

## **3.1 Introduction**

Low-noise amplifier (LNA) is the first component in a wireless receiver; it not merely provides enough gain to amplify weak signals received from the antenna but also needs to contribute minimum noise to the received signal so that the signal-to-noise ratio will not be severely degraded by the circuit. Another feature of a LNA is the ability to sustain large signals without distortion. Because the preceding stage of a LNA is either an antenna or a RF bandpass filter, the input needs to be well matched to  $50-\Omega$  so that maximum power transfer can be achieved. The general requirement [13] of a LNA is summarized in Table 3.1.

| Parameter(s)     | Specification(s) |

|------------------|------------------|

| Noise Figure     | ~ 3 dB           |

| IIP <sub>3</sub> | -10 dBm          |

| Gain             | 15 - 20 dB       |

| Input impedance  | 50–Ω             |

Table 3.1 General specifications of a LNA in super-heterodyne systems

Based on the GSM specifications described in Chapter 2, the LNA requirements in Table 3.1 are modified and tabulated in Table 3.2.1. In conventional LNA design, inductors are realized using bond-wire to minimize the noise figure, nonetheless, it is the best if they can also be integrated on the same chip. As a consequence, inductors in both the matching network and the resonant circuit are on-chip. These on-chip spirals are lossy and generate a lot of noise, therefore, a large gain is required to mitigate the total noise figure. At the same time, they needs to be compensated so that a better Q can be achieved. Therefore, the total noise figure has to be increased to around 6 dB to account for the lossy inductors and the compensation circuits. Meanwhile, as the amplifier gain is high to reduce the noise figure, the linearity of a bandpass amplifier is degraded and is usually much lower than conventional LNAs. The linearity requirement is adjusted so that the amplifier can meet the minimum GSM standard, yet this value is still very tough to be achieved. The 3-dB bandwidth of the amplifier is set to be 25-MHz to filter out the blocking and image signals.

| Parameters       | Requirement   |

|------------------|---------------|

| Gain             | 20 - 30 dB    |

| IIP <sub>3</sub> | - 18 dBm      |

| Image Rejection  | ~ 20 dB       |

| 3-dB Bandwidth   | 25 MHz        |

| Center frequency | 940 ~ 950 MHz |

| Noise Figure     | ~ 5 - 6 dB    |

Table 3.2: Modified Requirement for the bandpass amplifier

## **3.2 Basic LNA Design**

In this section, important design parameters of a LNA will be presented including the input matching, LNA topology and the output resonant tank.

#### **3.2.1 Input Matching**

As discussed before, the input of a LNA needs to be matched to  $50-\Omega$  to ensure maximum power transfer. There are several types of input matching that can be employed in the design.

The first one is to insert a real 50- $\Omega$  resistor in parallel with the input of device shown in Fig. 3.1 so that 50- $\Omega$  matching can be guaranteed at any frequencies. It is the simplest way, but

Fig. 3.1 Input matching using  $50-\Omega$  resistor

not an effective way to be utilized for LNA design. The major drawback is poor noise performance because the noise contributed from the 50- $\Omega$  resistor is exactly the same as that of a 50- $\Omega$  source resistor. As a consequence, the noise figure of this configuration would exceed 3 dB.

Common-gate configuration is another method to realize the input matching as illustrated in Fig. 3.2. It is known that the impedance looking from the source of a device is  $\frac{1}{gm}$ , and an input impedance of 50- $\Omega$  can be achieved by properly biased the input device M<sub>1</sub>. The

Fig. 3.2 Input matching using common-gate configuration

disadvantage of this approach is that the transconductance of the input device is fixed, the noise after the input device  $M_1$  cannot be reduced by simply increasing the transconductance of the input device.

The noise factor (F) of the configuration is

$$NF = \left(\frac{4kTR_s + 4kT\gamma_{gm}}{4kTR_s}\right)$$

$$= (1 + \gamma) \qquad (3.1)$$

As stated in Chapter 2, there is actually no difference between noise factor and noise figure, the former will be used in the following discussion

For long-channel devices,  $\gamma = \frac{2}{3}$ , and the minimum NF would be around 2.2 dB.

However, for short-channel device,  $\gamma$  can be as large as 2 to 3, and NF would approach to 6 dB. Therefore, the configuration is not commonly used as well.

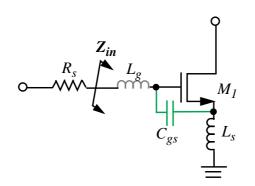

Another method is inductive source degeneration, which is given in Fig. 3.3. The input impedance  $Z_{in}$  is equal to

$$Z_{in}(s) = sL_g + sL_s + \frac{1}{sC_{gs}} + \frac{gm}{C_{gs}}L_s = sL_g + sL_s + \frac{1}{sC_{gs}} + \omega_T L_s , \qquad (3.2)$$

Fig. 3.3 Input matching using inductive source degeneration

where  $L_g$ ,  $L_s$  and  $C_{gs}$  are the gate inductance, the source inductance and the gate-to-source capacitance of  $M_1$  respectively.  $\omega_T$  is defined as gm/C<sub>gs</sub>, unity-gain frequency. The imaginary part

vanishes at  $\omega_o$ , where  $\omega_o = \frac{1}{\sqrt{(L_g + L_s)C_{gs}}}$ . At resonance, the impedance  $Z_{in}$  is purely

resistive and equal to

$$Z_{in}(\omega_o) = \omega_T L_s, \tag{3.3}$$

The advantage of this configuration is that the resistive term in Eq. (3.2) is not realized using a physical resistor or its equivalents, and it is therefore theoretically noiseless. However, if on-chip spiral inductors are used, their noise contribution due to the resistive losses cannot be neglected. To take the resistive losses into account, the modified output impedance  $Z_{in}$  is

$$Z_{in}(s) = sL_g + sL_s + \frac{1}{sC_{gs}} + \frac{gm}{C_{gs}}L_s + R_g + R_l = sL_g + sL_s + \frac{1}{sC_{gs}} + \omega_T L_s + R_g + R_l, (3.4)$$

where  $R_g$  and  $R_l$  represent the series loss of the inductor  $L_g$  and  $L_s$  respectively. The real part of  $Z_{in}$  becomes

$$Z_{in}(\omega_o) = \omega_T L_s + R_g + R_{l'}$$

(3.5)

If inductors are realized using bond-wire, the quality factor can be as high as 50 and the noise degradation due to lossy inductors are very small. Nonetheless, if inductors are achieved using on-chip spirals, the quality factor is usually limited to around 5. This degrades the noise performance of the whole circuit. The detailed noise analysis is going to be discussed in depth in Chapter 4. To investigate how the resistive component in spiral inductors affects the input matching, a plot of the input matching of the LNA employing the inductive degeneration near resonance under different inductor's quality factor are displayed in Fig. 3.4. It should be noted that the resistive losses of the spirals contributes a large portion in the 50- $\Omega$  matching. When Q is set to 5, the input impedance drops to around  $30-\Omega$ . As mentioned above, no noisy resistive component in the inductive degeneration is the key advantage of this configuration. However, the planar inductor's loss reduces the advantage and limits the noise performance of the design. Actually, more than 20  $\Omega$  of the matching originates from the resistive loss and it inevitably produces noise at the input which cannot be reduced by the gain of the amplifier. As an example, if 20- $\Omega$  of the matching is contributed from the inductor's resistive losses, the low limit of NF is around 2.2 dB already. As a result, the LNA has poor noise figure and the condition would be more severe if Q is lower than 2.5.

The noise figure of the configuration can be proved to be

$$F = 1 + \frac{R_g + R_l}{R_s} + \frac{\gamma (R_s \omega_o C_{gs})^2}{R_s gm}$$

= 1 +  $\frac{R_g + R_l}{R_s} + \frac{\gamma R_s (\omega_o C_{gs})^2}{gm}$ . (3.6)

From the expression, the term  $1 + \frac{R_g + R_l}{R_s}$  is governed by the intrinsic Q of the inductor,

Fig. 3.4 The magnitude of the input matching under different inductor's Qit cannot be altered unless the spiral's Q can be improved. The last term depends on two design constraints, gm and  $C_{gs}$ . The noise figure can be reduced by increasing the transconductance, but, it dissipates more power. Another method is to reduce  $C_{gs}$  by using minimum channel length (L), nonetheless, the reduction degrades the linearity as the Q of input matching network which is defined as

$$Q_{in} = \frac{1}{\omega C_{gs}(R_s + R_g + R_l + \omega_T L_s)} = \frac{1}{2\omega R_s C_{gs}}$$

(3.7)

increases when  $C_{gs}$  decreases. Accordingly, there are trade-offs between linearity and noise figure. In this design, the use of on-chip inductors poses additional constraints on the size of  $C_{gs}$ . It should be pointed out that a small  $C_{gs}$  is accompanied with a large  $L_g$  so that the series input resonant circuit resonants at the desired frequency. Therefore,  $L_g$  cannot be arbitrarily selected as

A 900-MHz CMOS Bandpass Amplifier for GSM Receivers

it also governs the input matching and the noise performance of the whole circuit. Balance should be made so that an optimum noise figure can be obtained.

#### 3.2.2 LNA Topology

Even though the inductive source degeneration is not noiseless as deduced from the formula, its noise performance would be acceptable unless the inductor's Q is very low. The configuration has been chosen as the input matching of the LNA. In Eq. (3.5), the input matching is  $\omega_T L_s$  if the resistive loss is omitted and it is clear that only  $L_s$  is involved. Indeed, the gate inductance  $L_g$  in the matching network is to combine with  $L_s$  and  $C_{gs}$  to provide narrowband response at the input. At resonance  $\omega_o$ , the series resonant circuit impedance is at a minimum ( $R_s$ ).

Another advantage of the configuration is that it provides current gain  $(G_i)$  at resonance, which is given by

$$G_{i} = \frac{gm_{1}}{sL_{g} + sL_{s} + \frac{1}{sC_{gs}} + \omega_{T}L_{s} + R_{g} + R_{l} + R_{s}}.$$

(3.8)

This current gain also reduces the noise from the following stages. The simulated input matching of the LNA design is depicted in Fig. 3.5. The input impedance at the frequency of interest is 101  $\Omega$ . The resonant frequency of the series RLC circuit is at 940 MHz and the S<sub>11</sub> is - 45 dB.

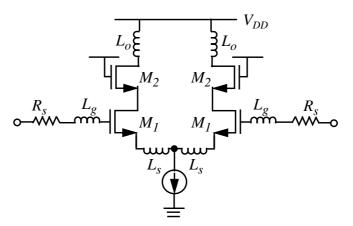

The basic architecture of a narrowband LNA is illustrated in Fig. 3.6.

It consists of a common-cascoded structure with the input matching described to reduce the noise from the output of the LNA and the subsequent stages. The cascode device  $M_2$  was chosen to

Fig. 3.5 The simulated input matching of the amplifier

Fig. 3.6 The basic architecture of a common-cascoded LNA

improve the reverse isolation between the input and the output and alleviate the Miller effect of  $M_1$  on the input matching. The LNA is implemented in differential manner to minimize evenorder harmonics and improve the linearity. It also helps to reject the common-mode substrate noise and parasitics due to packaging. To provide the highest level of integration, all components are realized on-chip. The output of the LNA is a parallel LC resonant tank, which resonates at the GSM's receiver band, 935 MHz to 960 MHz.

The transconductance of the amplifier is

$$Gm_{in}(s) = \frac{gm_1\left(\frac{1}{sC_{gs}}\right)}{sL_g + sL_s + \frac{1}{sC_{gs}} + \omega_T L_s + R_g + R_l + R_s}.$$

(3.9)

The imaginary part of the input impedance vanishes at resonance and merely the real part  $(R_g + R_l + \omega_T L_s)$  is left, which is designed to be equal to  $R_s$ . The transconductance at resonance is

$$Gm_{in}(\omega_o) = \frac{gm_1}{2\omega_o C_{gs}R_s} = \frac{\omega_T}{2\omega_o R_s}$$

(3.10)

From the expression in Eq. (3.10), the transconductance only depends on the ratio of  $gm/sC_{gs}$ . Since a smaller  $C_{gs}$  is accompanied with larger inductance values  $(L_g + L_s)$  for a given resonant frequency, it increases the size and the noise of the circuit.

#### 3.2.3 Parallel RLC resonant circuit

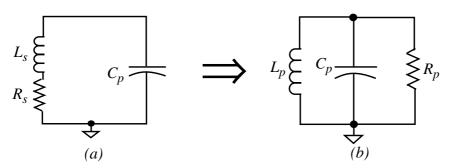

After discussing the input matching circuit and the transconductance of the narrowband LNA, the output resonant circuit is now addressed. A lossy LC resonant tank is illustrated in Fig. 3.7. The circuit in Fig. 3.7a can be transformed into a parallel RLC circuit in Fig. 3.7b. The transformed  $L_p$  and  $R_p$  are

$$L_p = \frac{(Q^2 + 1)L_s}{Q^2}$$

(3.11)

Fig. 3.7 A parallel lossy LC circuit

$$R_p = (Q^2 + 1)R_s (3.12)$$

respectively, where Q is the quality factor of the inductor.

$$Q = \frac{\omega L_s}{R_s} . \tag{3.13}$$

The transfer function of this parallel RLC circuit is

$$Z(s) = \frac{\frac{s}{C_p}}{s^2 + \frac{s}{R_p C_p} + \frac{1}{L_p C_p}}.$$

(3.14)

The corresponding natural frequency and the 3-dB bandwidth are given by

$$\omega_o = \frac{1}{\sqrt{L_p C_p}} \tag{3.15}$$

and

$$\omega_{-3 \ dB} = \frac{1}{R_p C_p}.$$

(3.16)

So as to filter out the out-of-band blocking and image signals, the 3-dB bandwidth of this narrowband bandpass amplifier is 25 MHz, which is the bandwidth of the GSM receiver band

(935 -960 MHz). The Q of an LNA is usually dominated by the intrinsic Q of the output inductor (<5). Nonetheless, to attain a the specified bandwidth, the circuit's quality factor needs to be around 35 to 40. As a result, compensation methods have been proposed to cancel out the resistive losses of the spiral inductors and it is going to be discussed in Section 3.4.1.

#### **3.2.4** Noise Considerations

Since low-noise figure is the one of the most important specification of a LNA, the noise considerations will be analyzed in depth in Chapter 4.

## **3.3 Monolithic Spirals** [15] [32] [31]

#### 3.3.1 Limitations of on-chip spirals

One of the critical limitations on integrating high performance LNAs and bandpass filters on chip are spiral inductors. Unlike resistors and capacitors, whose their values are well estimated except for variations due to the process (around 10%), on-chip spirals are still not well optimized in terms of shape, metal width, metal spacing, quality factor and value. Modern CMOS process usually consists of an heavily doped epi layer which is highly conductive, eddy current induced by the magnetic field of the inductor onto the substrate directly degrades the inductor performance.

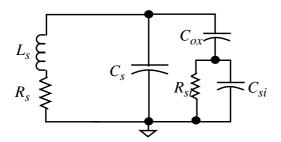

#### **3.3.2 General Spiral Inductor Model**

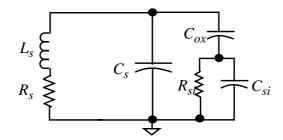

A widely used inductor model [20] is depicted in Fig. 3.8, where  $R_s$  is the series resistance of the inductor  $L_s$ .  $C_s$  represents the capacitance between the spiral and the center-tap underpass.

Fig. 3.8 A complete inductor model

$C_{ox}$  is the capacitance between the spiral and the substrate.  $R_{si}$  and  $C_{si}$  models the lossy silicon substrate.

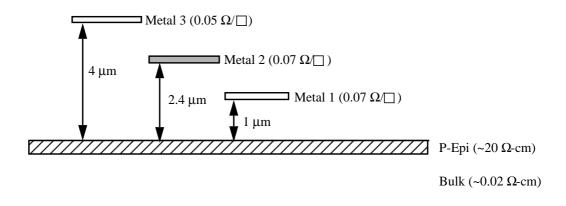

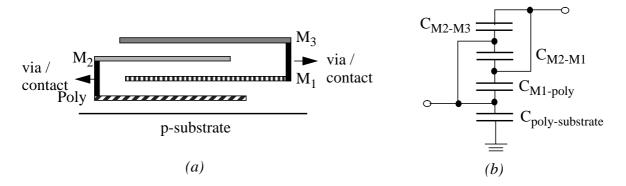

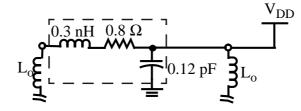

The losses of on-chip spirals is usually not limited only by the metal winding losses but also by the lossy silicon substrate. At low frequencies, the impedance of  $C_{ox}$  is very large, and the spiral is isolated from the lossy substrate. Thus, the loss is only contributed from the metal layer. As frequency increases, the impedance of  $C_{ox}$  decreases, and the resistive loss due to the substrate begins to increase. At high frequency,  $C_{ox}$  is virtually shorted and the substrate losses dominates. Thus, the resistive losses increases with the frequency instead of remaining constant. Some of the process information for 0.8 µm single-poly, triple metal CMOS is duplicated graphically in Fig. 3.9.

The inductance value (single-layer metal) is well estimated by the Greenhouse's formula [19]. A simple estimate of a spiral inductance can also be found to be [13]

$$L = \mu_o n^2 r, \qquad (3.17)$$

where  $\mu_0$  is the permeability of free space, n is the number of turns, and r is the radius of the inductor. To have a more accurate estimate of the inductance value, the inductor structure can be analyzed in 3-D electromagnetic simulator like SONNET EM [26]. Nonetheless, it is usually

Fig. 3.9 General process information of a typical 0.8 µm CMOS (HP SCN26G)

time-consuming especially when the structure needs to be optimized using the simulator in terms of spacing, metal width and total area. As a compromise, another program ASITIC [21], which has been reported to have a good agreement between the modeling and the measurement result of the inductors on BiCMOS technology, is employed in the design to optimize the design. An attractive advantage of using the program is that it is much faster than E-M SONNET and circular inductor can also be analyzed. One of the drawbacks of the tool is that the simulator does not include the effect of eddy current in the substrate, which is not serious in a less-conductive BiCMOS substrate but quite important in lossy CMOS substrate. This accounts for the fact that the simulated high-frequency inductor's Q is much better than the measured one.

Monolithic spirals are usually put on the topmost metal (Metal 3 in our case) as the sheet resistance is the smallest (50 m $\Omega/\Box$ ) and the separation between the spiral and the lossy substrate is the largest (4 µm). Besides, circular spirals are known to have higher Q than the square inductor with the same metal width, spacing. They are utilized in the design in an attempt to optimize the quality factor. Other design consideration such as metal spacing, number of turns, inner hole size will be discussed in Chapter 7.

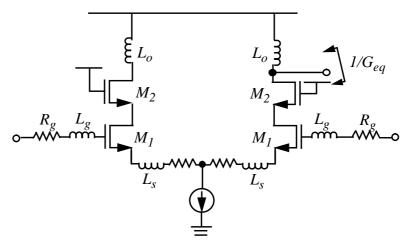

## 3.4 Design of a bandpass amplifier

As discussed earlier in Chapter 2, the image-reject filter will be finally integrated together with other components in a single-chip transceiver. To realize the goal, the LNA in a receiver has to share the image rejection burden together with the on-chip RF bandpass filter so that the image rejection provided by the front-end is enough to meet the minimum requirement of the GSM standard and the off-chip image-reject filter can be eliminated. However, as stated in Section 3.3.1, the spiral inductor's Q is so low that the LNA utilizing them cannot provide much image rejection (~ 10 dB) and thus Q-compensation circuit is required to enhance or to compensate the loss in the spiral. After compensation, both the 3-dB bandwidth and the image rejection of a LNA can be greatly improved at the expense of larger noise figure and poorer linearity, which will be discussed later. The LNA with Q-compensation described below is termed as bandpass amplifier as it can provide not only signal amplification as conventional LNA but also filtering function as bandpass filters.

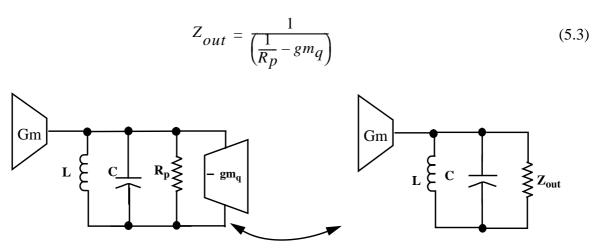

#### **3.4.1 Q Compensation Technique**

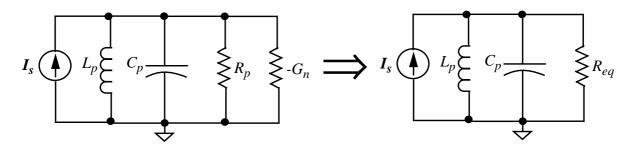

To compensate the losses due to low-quality spiral inductors, a negative conductance  $G_n$  is introduced in parallel to the resonant tank depicted in Fig. 3.10, where  $R_{eq}$  is the resultant parallel resistance. For ideal LC resonant tank, the energy is stored in the magnetic field of the inductor or in the electric field of the capacitor, and no energy is lost in the circuit. In practice, energy is dissipated in the non-ideal inductors and capacitors. This loss is represented as  $R_p$  in Fig. 3.10. So as to reduce the losses in the LC tank, the current flowing through the resistor  $R_p$  is partially provided by the negative conductance  $G_n$  rather than the LC resonant circuit. Accordingly, the LC

Fig. 3.10 A parallel LC resonant tank compensated with negative conductance

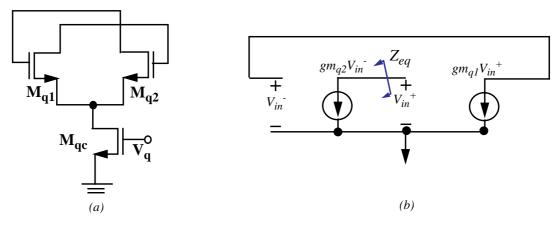

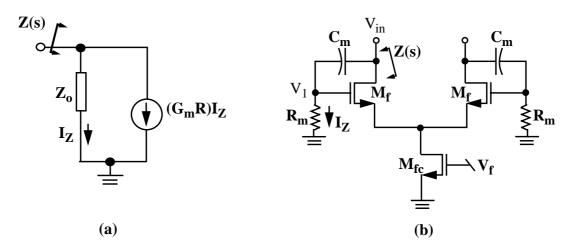

resonant circuit looks like to be lossless when all the current flowing through  $R_p$  is supplied by  $G_n$ . Nonetheless, it is unstable when the circuit is over-compensated, i.e.  $G_n > R_p$ .