# A 1-V CMOS Power Amplifier for Bluetooth Applications

by

# Ho Ka Wai

A Thesis Submitted to The Hong Kong University of Science and Technology in Partial Fulfillment of the Requirements for the Degree of Master of Philosophy in Electrical and Electronic Engineering

August 2002, Hong Kong

## **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Ho Ka Wai

### A 1-V CMOS Power Amplifier for Bluetooth Applications

by

### Ho Ka Wai

This is to certify that I have examined the above MPhil thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the thesis examination committee have been made.

**Dr. Howard Cam LUONG** Thesis Supervisor

**Dr. Ross Murch** Thesis Examination Committee Member (Chairman)

**Dr. Philip K. T. Mok** Thesis Examination Committee Member

#### **Prof. Philip Ching-Ho Chan**

Head of Department of Electrical and Electronic Engineering

Department of Electrical and Electronic Engineering The Hong Kong University of Science and Technology

August 2002

# Acknowledge

I would like to take this opportunity to express my greatest gratitude to many individuals who have given me a lot of supports during my two-year master program.

First of all, I am indebted to my thesis supervisor, Dr. Howard Cam Luong, for his insight, the valuable guidance throughout the entire research and his patience in reminding me to complete the works on time.

I would also be grateful to Frederick Kwok for his efficient technical support in measurement setups and PCB making. Allen Ng for his patience in teaching me how to use the bondwire machine. S. F. Luk for his kindly help in CAD tools and chips tape-out.

I would like to thank my friends, Ming, Vincent, Gary, Gerry, Lincoln, Sun, Martin, Joseph, Kenneth and Alan in analog research lab. They have given me a lot of valuable suggestions in circuit design and provide enjoyment outside of the university.

I would like to thank Dr. Ross Murch and Dr. Philip K. T. Mok for being my thesis

exam committee.

I would like to thank Agnes Au who does not mind working with me on holidays and supports me by all means.

Finally, I would like to special thank my family for their encouragement and moral support.

# **Table Of Contents**

| Title P                                  | age                                                                                  | i                            |

|------------------------------------------|--------------------------------------------------------------------------------------|------------------------------|

| Autho                                    | rization Page                                                                        | ii                           |

| Signat                                   | ure Page                                                                             | iii                          |

| Ackno                                    | wledgment                                                                            | iv                           |

| Table                                    | Of Contents                                                                          | vi                           |

| List O                                   | f Figures                                                                            | ix                           |

| List O                                   | f Tables                                                                             | xii                          |

| Abstra                                   | ict                                                                                  | xiii                         |

|                                          |                                                                                      |                              |

| <u>Chapt</u>                             | er 1 Introduction                                                                    | 1                            |

| <u>Chapt</u><br>1.1                      | er 1 Introduction<br>Motivation                                                      | <u>1</u><br>1                |

|                                          |                                                                                      |                              |

| 1.1                                      | Motivation                                                                           | 1                            |

| 1.1<br>1.2                               | Motivation<br>Specifications<br>Thesis Outline                                       | 1<br>3                       |

| 1.1<br>1.2<br>1.3                        | Motivation<br>Specifications<br>Thesis Outline                                       | 1<br>3<br>5                  |

| 1.1<br>1.2<br>1.3<br><u>Chapt</u>        | Motivation<br>Specifications<br>Thesis Outline<br>er 2 Basics Of Power Amplifier     | 1<br>3<br>5<br><u>8</u>      |

| 1.1<br>1.2<br>1.3<br><u>Chapt</u><br>2.1 | Motivation Specifications Thesis Outline er 2 Basics Of Power Amplifier Introduction | 1<br>3<br>5<br><u>8</u><br>8 |

|              |       | 2.3.1.1 C                           | lass A                     | 13       |

|--------------|-------|-------------------------------------|----------------------------|----------|

|              |       | 2.3.1.2 C                           | lass B                     | 15       |

|              |       | 2.3.1.3 C                           | lass AB                    | 18       |

|              | 2.3.2 | Non-Linea                           | r Power Amplifiers         | 19       |

|              |       | 2.3.2.1 C                           | lass C                     | 19       |

|              |       | 2.3.2.2 C                           | lass E                     | 21       |

|              |       | 2.3.2.3 C                           | lass F                     | 23       |

| 2.4          | Sumn  | ary                                 |                            | 24       |

| <u>Chapt</u> | er 3  | De                                  | sign Of Power Amplifier    | 27       |

| 3.1          | Intro | luction                             |                            | 27       |

| 3.2          |       | n Of Power                          | Amplifier                  | 27       |

| 5.2          | 3.2.1 |                                     | -                          | 28       |

|              |       | Differentia                         |                            |          |

|              | 3.2.2 |                                     | wer Amplifier              | 29       |

|              | 3.2.3 | Output Matching Network             |                            | 31       |

|              | 3.2.4 | Design Of Output Stage              |                            | 33       |

|              | 3.2.5 | Common-Gate Class-E Power Amplifier |                            | 35       |

|              | 3.2.6 | Driver Stag                         | ge Using Positive Feedback | 39       |

|              | 3.2.7 | Proposed A                          | Architecture               | 39       |

|              | 3.2.8 | Pre-simulation Results              |                            | 43       |

|              | 3.2.9 | Inductor R                          | ealization                 | 45       |

| <u>Chapt</u> | er 4  | Bo                                  | ndwire Modeling            | 48       |

| 4.1          | Intro | luction                             |                            | 48       |

| 4.2          |       | tor Model                           |                            | 49       |

| 4.3          |       |                                     | on Of Bondwire Inductance  | 4)<br>50 |

| 4.3          | лпату |                                     |                            | 50       |

| 4.4          | Simulation Results of Bondwire Inductance | 53 |

|--------------|-------------------------------------------|----|

| <u>Chapt</u> | er 5 Layout Considerations                | 56 |

| 5.1          | Introduction                              | 56 |

| 5.2          | Capacitors Layout                         | 57 |

| 5.3          | Wire Layout                               | 59 |

| 5.4          | Floorplan                                 | 60 |

| 5.5          | Post-Layout Simulation Results            | 62 |

| <u>Chapt</u> | er 6 Measurement Results                  | 64 |

| 6.1          | Introduction                              | 64 |

| 6.2          | Bondwire Measurement                      | 64 |

|              | 6.2.1 Testing Setup                       | 64 |

|              | 6.2.2 Measurement Results                 | 65 |

| 6.3          | The Power Amplifier Measurement           | 68 |

|              | 6.3.1 Die Photo of the Power Amplifier    | 68 |

|              | 6.3.2 Testing Setup                       | 68 |

|              | 6.3.3 Measurement Results                 | 71 |

| 6.4          | Performance Summary                       | 75 |

| <u>Chapt</u> | er 7 Conclusion                           | 77 |

| 7.1          | Conclusion                                | 77 |

| 7.2          | Potential Improvement                     | 78 |

| 7.3          | Future Work                               | 82 |

| Appen        | dix A Input Impedance of the output stage | 85 |

# **List Of Figures**

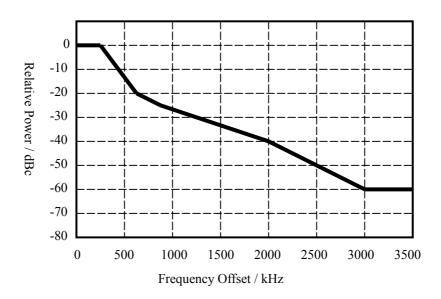

| Figure 1.1  | Output spectrum mask for class 1 Bluetooth                         | 4  |

|-------------|--------------------------------------------------------------------|----|

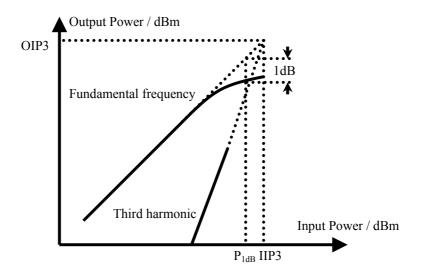

| Figure 2.1  | Definitions of IP3 and $P_{1dB}$                                   | 10 |

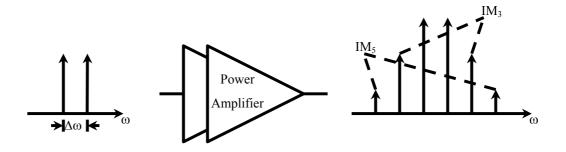

| Figure 2.2  | Two-tone test of a power amplifier                                 | 10 |

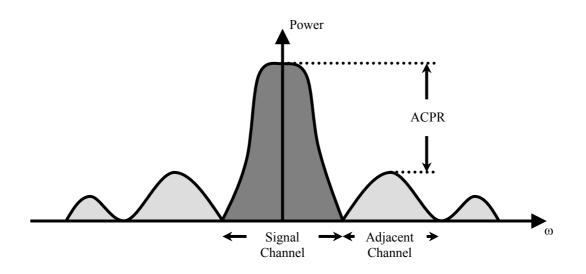

| Figure 2.3  | Definition of ACPR                                                 | 11 |

| Figure 2.4  | Typical configuration of a class-A power amplifier                 | 13 |

| Figure 2.5  | Voltage and current waveforms of an ideal class-A power amplifier  | 14 |

| Figure 2.6  | Voltage and current waveforms of an ideal class-B power amplifier  | 16 |

| Figure 2.7  | Complementary class-B power amplifier                              | 16 |

| Figure 2.8  | A transformer coupled class-B power amplifier                      | 17 |

| Figure 2.9  | Voltage and current waveforms of an ideal class-AB power amplifier | 18 |

| Figure 2.10 | Voltage and current waveforms of an ideal class-C power amplifier  | 20 |

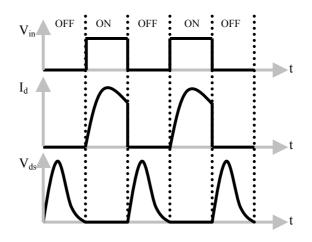

| Figure 2.11 | A typical configuration of a class-E power amplifier               | 22 |

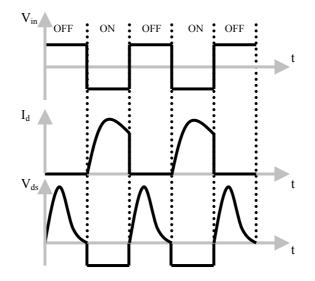

| Figure 2.12 | Voltage and current waveforms of an ideal class-E power amplifier  | 22 |

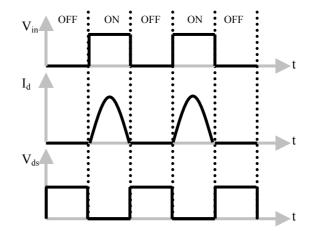

| Figure 2.13 | A simple configuration of a class-F power amplifier                | 23 |

| Figure 2.14 | Voltage and current waveforms of an ideal class-F power amplifier  | 24 |

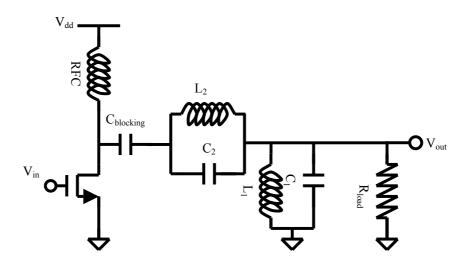

| Figure 3.1  | Configuration of a class E power amplifier                         | 29 |

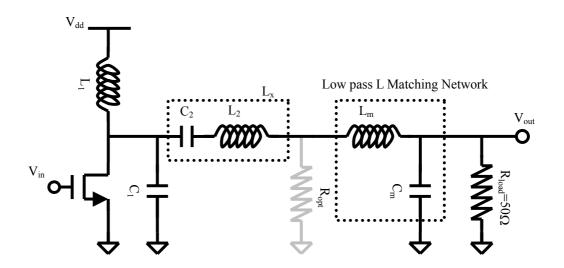

| Figure 3.2  | Complete schematic of a class E power amplifier                    | 32 |

| Figure 3.3a | A switch using common-source configuration                         | 36 |

| Figure 3.3b | A switch using common-gate configuration                           | 36 |

| Figure 3.4  | Schematic of the published common-gate class-E power amplifier     | 37 |

| Figure 3.5  | Schematic of the proposed common-gate class-E power amplifier      | 37 |

| Figure 3.6  | Voltage and current waveforms of a common-gate class E power      |    |

|-------------|-------------------------------------------------------------------|----|

|             | amplifier                                                         | 38 |

| Figure 3.7  | Schematic of the proposed power amplifier                         | 40 |

| Figure 3.8  | Equivalent schematic of the interstage-matching network           | 42 |

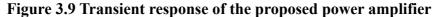

| Figure 3.9  | Transient response of the proposed power amplifier                | 44 |

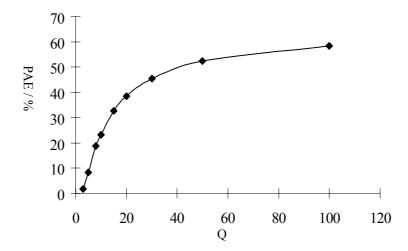

| Figure 3.10 | PAE versus inductor Q                                             | 45 |

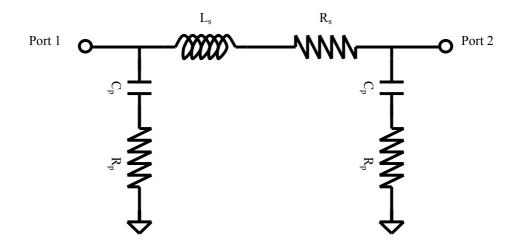

| Figure 4.1  | Lumped-element model for a bondwire inductor                      | 49 |

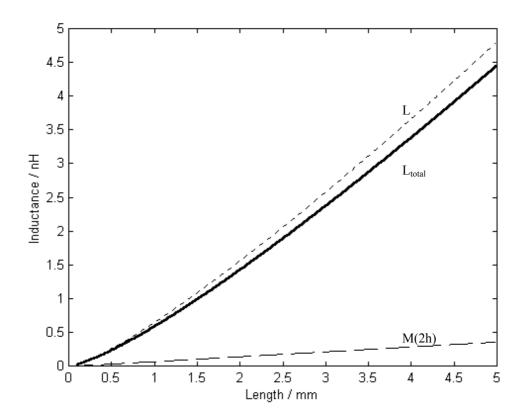

| Figure 4.2  | Theoretical total inductance against the length of the wire       | 51 |

| Figure 4.3  | Simulated Inductance and quality factor against the length of the |    |

|             | bondwire                                                          | 53 |

| Figure 5.1  | Polysilicon-polysilicon capacitor with parasitics                 | 58 |

| Figure 5.2  | Capacitors inside the proposed power amplifier                    | 59 |

| Figure 5.3  | Floorplan of the overall circuit                                  | 60 |

| Figure 5.4  | Circuit layout of the proposed power amplifier                    | 61 |

| Figure 5.5  | Post-simulation on the transient response of the proposed power   |    |

|             | amplifier                                                         | 62 |

| Figure 6.1  | Testing setup for bondwire inductance                             | 65 |

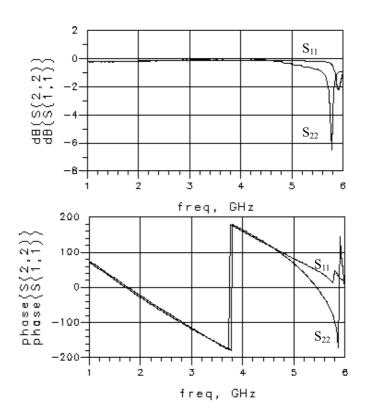

| Figure 6.2  | Simulated and measured S-parameter of open-pad testing setup      | 65 |

| Figure 6.3  | Simulated and measured S-parameter of bondwire measurement        | 66 |

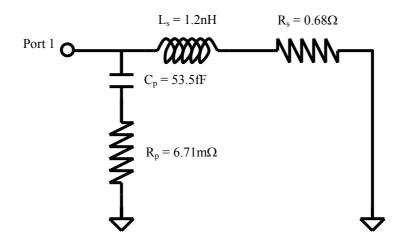

| Figure 6.4  | A 1.2nH bondwire model                                            | 67 |

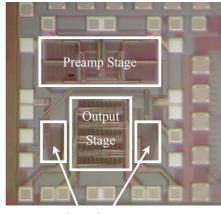

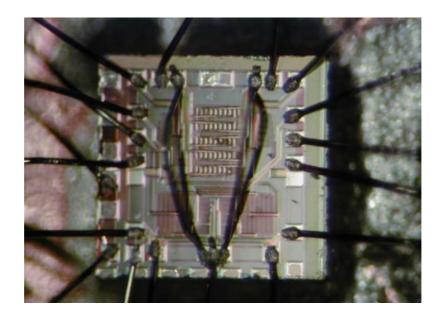

| Figure 6.5  | Photograph of the chip                                            | 68 |

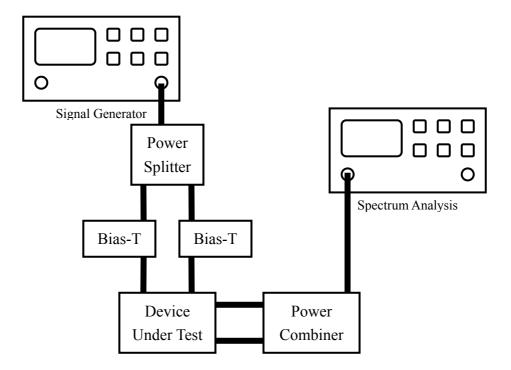

| Figure 6.6  | Testing setup for the proposed power amplifier                    | 69 |

| Figure 6.7  | Experimental prototype of the power amplifier                     | 71 |

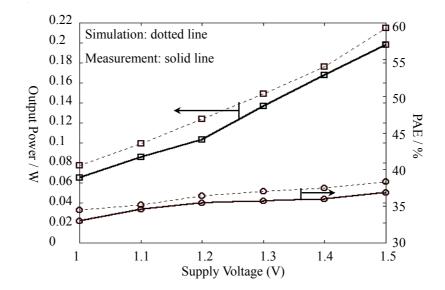

| Figure 6.8  | Output power and PAE versus supply voltage                        | 72 |

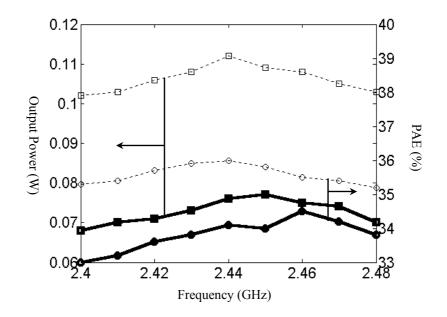

| Figure 6.9   | Dutput power and PAE versus frequency with 1V and 1.2V supply |    |

|--------------|---------------------------------------------------------------|----|

|              | voltage                                                       | 73 |

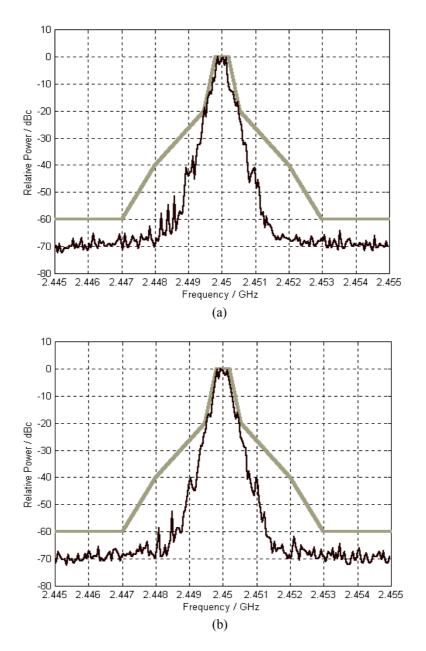

| Figure 6.10a | The measured ACPR under 1V supply voltage                     | 74 |

| Figure 6.10b | The measured ACPR under 1.2V supply voltage                   | 74 |

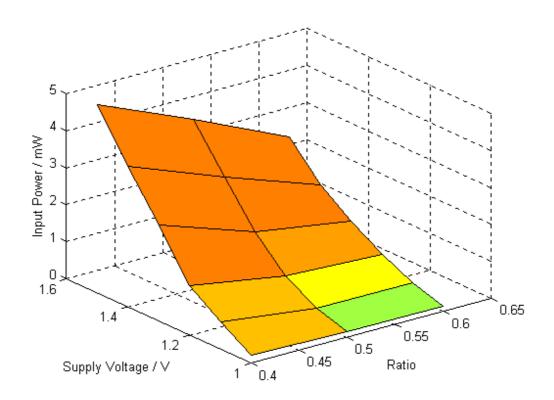

| Figure 7.1   | Input power and supply voltage against the ratio of the input |    |

|              | device size to the size of the positive feedback device       | 81 |

| Figure A1    | Schematic of the output stage                                 | 85 |

# List Of Tables

| Table 1.1 | Transmit spectrum mask                                          | 4  |

|-----------|-----------------------------------------------------------------|----|

| Table 2.1 | Performance summaries of different classes of power amplifiers  | 25 |

| Table 3.1 | Summary of the values of the passive components                 | 43 |

| Table 3.2 | Summary of the transistors sizing                               | 43 |

| Table 3.3 | Performance of the power amplifier                              | 44 |

| Table 5.1 | Modified parameters for post-layout simulation                  | 62 |

| Table 5.2 | Performance of the power amplifier                              | 63 |

| Table 6.1 | Parameters for different inductors                              | 67 |

| Table 6.2 | Summary of performance of the power amplifiers                  | 75 |

| Table 7.1 | Summary of the simulation on the ratio of the size of the input |    |

|           | device to the positive feedback device                          | 80 |

### A 1-V CMOS Power Amplifier for Bluetooth Applications

by Ho Ka Wai

Department of Electrical and Electronic Engineering The Hong Kong University of Science and Technology

#### ABSTRACT

With recent advance in CMOS processes, many essential building blocks for wireless transceivers, such as low-noise amplifier (LNA), mixer, frequency synthesizer, channel selection filter and digital-to-analog converter, have been demonstrated using CMOS technology. However, not much work has been done or reported a CMOS power amplifier, in particular at low supply voltage. As supply voltage is reduced to 1V, the performance of the power amplifier, such as the output power and the efficiency are degraded.

In this thesis, the design considerations of a RF CMOS power amplifier under low supply voltage are detailed. A two-stage power amplifier operated at 2.4GHz and 1-V supply has been designed and fabricated for Bluetooth applications in a standard 0.35µm CMOS technology. A common-gate Class E output stage, which operates under low supply voltage without degrading the efficiency, is proposed. A pre-amplifier with positive feedback configuration is employed to drive the common-gate output stage. To achieve high efficiency and high output power, bondwires are used as inductors for the power amplifier because of their high quality factor.

Measurement results show that the amplifier delivers 18dBm output power with 33% power-added efficiency (PAE) under a 1V supply voltage. With a 1.2V supply, the amplifier delivers 20dBm output power with 35 % PAE and can be integrated for class 1 Bluetooth application. The measured output spectrum falls within the Bluetooth spectrum mask when a modulated signal is input to the power amplifier. The adjacent-channel power rejection (ACPR) at 550kHz offset is -21.4 dBc under 1V and -23.5 dBc with 1.2V supply voltage.

# **CHAPTER 1**

## **INTRODUCTION**

### **1.1 Motivation**

Wireless communications have shown remarkable growth in the last decade. For example, more and more people have their own mobile phones. Some of them have already owned several mobile phones in the past few years and are eager to buy new phones with better performance. Manufacturers have to develop smaller mobile phones with longer lifetimes and lower cost so as to keep competitive. Therefore, experts in wireless communications put significant efforts to further improve the performance and reduce the cost of the mobile phone.

Nowadays, the dominant technologies used for the radio frequency (RF) front-end circuits of a mobile phone are Gallium Arsenide (GaAs), BiCMOS and silicon bipolar. These technologies offer higher breakdown voltage, lower substrate loss and higher quality of monolithic inductors and capacitors compared with CMOS technology. However, they are much more expensive. CMOS technology is exclusively used on the digital signal-processing unit. The realization of the RF front-end circuits using CMOS technology can provide single-chip solution which greatly reduces the cost. Moreover, the advance in CMOS process has made it more possible to realize CMOS RF circuits with performance comparable to that using GaAs, BiCMOS and silicon bipolar. Most of the essential building blocks of a receiver, such as low noise amplifier (LNA), mixer, frequency synthesizer and intermediate frequency (IF) filter, have been realized by CMOS processes [1][2].

Recently, short distance wireless communications, such as wireless local area network (WLAN) and Bluetooth, have drawn the attention of researchers due to the rapidly growth in personal communication systems. CMOS RF front-end circuits are capable to meet the specifications so that the whole system can be integrated into one chipset [3].

Although CMOS technology provides single chip solution, it also suffers from a poor quality factor of monolithic passive components, low breakdown voltage of the transistors and large process variation. Also, the scaling of the CMOS technology forces the supply voltage to a lower level which results in degradation of the performance of the transceiver. Among all the building blocks of a transceiver, the power amplifier contributes the most in terms of power consumption of the whole transceiver. The efficiency of the power amplifier becomes one of the crucial parameters to be optimized for power saving. However, the efficiency of the power amplifier is degraded by reducing supply voltage.

This dissertation will focus on the design considerations and implementation of a CMOS power amplifier for Bluetooth applications under low supply voltage.

## **1.2 Specifications**

In this section, the specification of Bluetooth will be described. Also, the requirement of power amplifier for Bluetooth applications will be detailed.

As the last building block of the transmitter, a RF power amplifier has to amplify the RF signal before a RF signal is transmitted at the antenna. Because there are losses in the channel, the signal power should be large enough so that the signal is still readable at the receiver. Therefore, the output power of the power amplifier defines the transmission distance of a communication standard.

Bluetooth is a short distance wireless communication standard which operates from 2400MHz to 2483.5MHz Industrial Scientific Medicine (ISM) band. Based on the

signal transmission distance, the required transmitter power level for Class 1, Class 2 and Class 3 are 20dBm, 4dBm and 0dBm, respectively. The modulation scheme employed is Gaussian Frequency Shift Keying (GFSK) which is a constant envelope modulation scheme [4]. Table 1.1 shows the requirement of the transmitted power at certain frequency offset.

| Frequency Offset | Transmit Power |

|------------------|----------------|

| ± 550 kHz        | -20 dBc        |

| M-N  = 2         | -20 dBm        |

| $ M-N  \ge 3$    | -20 dBm        |

Table 1.1 Transmit spectrum mask

According to table 1.1, the output spectrum of the power amplifier for Class-1 Bluetooth should be under the profile as shown below.

Figure 1.1 Output spectrum mask for class 1 Bluetooth

Since the specification on linearity of the power amplifier is quite relaxed, non-linear power amplifiers can be used to achieve high efficiency. The trade off between linearity and efficiency will be detailed in chapter 2.

With the advance in process, the supply voltage is scaled down. The new market trend is to build a single supply system with low operating voltage. Our research group, the Analog Research Group, have demonstrated the use of 1-V supply voltage in many essential building blocks such as low noise amplifier (LNA), mixer and voltage-controlled oscillator (VCO) [5]. Therefore, the power amplifier will be designed under 1-V supply voltage in order to fully integrate the whole transceiver. The output power is targeted at 20dBm for Class 1 Bluetooth application.

# **1.3 Thesis Outline**

In this thesis, there are 7 chapters. Some of the basics of power amplifier will be detailed in chapter 2 to provide background information for the readers. Chapter 3 will discuss the design considerations of the power amplifier used for Bluetooth applications. The inductor is one of the essential components in power amplifier circuit. The modeling of the bondwire inductor will be described in chapter 4. In chapter 5, both circuit and printed circuit board (PCB) layout considerations will be presented. The measurement results of bondwire and the power amplifier will be

shown in chapter 6. The thesis ends with a conclusion in chapter 7 and talks about the potential improvement of the circuit and the future work.

# Reference

- A. Rofougaran, G. Chang, J. J. Rael, J. Y. C. Chang, M. Rofougaran, P. J. Chang, M. Djafari, M. K. Ku, E. W. Roth, A. A. Abidi, H. Samueli, "A Single-Chip 900-MHz Spread-Spectrum Wireless Transceiver in 1-μm CMOS Part II: Receiver Design," *IEEE J. Solid-State Circuits*, pp. 535-547, April 1998.

- [2] D. K. Shaeffer, A. R. Shahani, S. S. Mohan, H. Samavati, H. R. Rategh, M. del Mar Hershenson, X. Min, C. P. Yue, D. J. Eddleman, T. H. Lee, "A 115mW, 0.5µm CMOS GPS Receiver with Wide Dynamic-Range Active Filters," *IEEE J. Solid-State Circuits*, pp. 2219-2231, Dec. 1998.

- [3] H. Komurasaki, T. Heima, T. Miwa, K. Yamamoto, H. Wakada, L. Yasui, M. Ono, T. Sano, H. Sato, T. Miki, and N. Kato, "A 1.8-V operation RFCMOS transceiver for bluetooth," *Digest of VLSI Circuits Conference*, pp 230-233, 2002.

- [4] Bluetooth Specification v1.0b.

- [5] Chan A., Ng K., Wong J. and Luong H. C. "A 1-V 2.4-GHz RF Receiver Front-End for Bluetooth Applications," *IEEE International Symposium on Circuits and Systems 2001*, pp. 454-457, Sydney, Australia, May 2001.

# **CHAPTER 2**

## **BASICS OF POWER AMPLIFIER**

### **2.1 Introduction**

Wherever there are wireless communications, there are transmitters. When there are transmitters, there must be RF power amplifiers. People rate the performance of an RF power amplifier in terms of the power gain, the efficiency and the linearity. Also, the basic underlying principles of operations of different power amplifier modes should be thoroughly understood before an improved circuit topology can be designed. Therefore, understanding the language used in the world of power amplifiers and the basic operating principle of different modes of power amplifier is required.

In this chapter, the merits and the terminologies used to characterize a power amplifier will be reviewed. Also, different classes of power amplifier and their corresponding features will be described.

### 2.2 Figure Of Merits

Whenever an RF power amplifier is discussed, people are interested in its power gain, power-added efficiency (PAE), the drain efficiency (DE) and the linearity.

The power gain of a power amplifier is defined as follows:

Power Gain =

$$\frac{\text{Power delivered to the load}}{\text{Power avaliable at the input port}} = \frac{\text{Pout}}{\text{P}_{\text{in}}}$$

(2.1)

The RF power amplifier consumes most of the power inside a transceiver. To preserve the battery lifetime, the power amplifier should be effective in converting DC power to RF power. PAE and DE are the parameters to characterize the effectiveness of power conversion. They are defined as:

$$DE = \frac{P_{out}}{P_{DC}}$$

(2.2)

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}}$$

(2.3)

where  $P_{out}$  is the output power at the desired frequency,  $P_{DC}$  is the DC supply power and  $P_{in}$  is the input power at the frequency of interest. PAE includes information on the driving power for a power amplifier, so PAE is commonly used instead of DE.

It is observed that the PAE is approximately equal to the DE if the power gain is

large enough. It also means that the power amplifier is more efficient.

Traditionally, linearity is measured with third order intermodulation intercept (IP3) and 1dB compression point ( $P_{1dB}$ ). Figure 2.1 shows the graphic representations of IP3 and  $P_{1dB}$ .

Figure 2.1 Definitions of IP3 and P<sub>1dB</sub>

Those parameters can be obtained using a two-tone test [1] as pictured in Fig. 2.2.

Figure 2.2 Two-tone test of a power amplifier

By applying two single-tone signals with equal amplitude but with slightly different frequencies circuit, the intermodulation products of the power amplifier are then measured at the output.

However, IP3 and P<sub>1dB</sub> are not accurate enough and can only provide a rough measure of linearity of a power amplifier. This is because most power amplifiers operate near the 1dB compression point in order to achieve the highest efficiency, and the nonlinear effects of higher order distortion should be taken into account. Therefore, the adjacent-channel power rejection (ACPR) is used to assess the linearity of a power amplifier instead of IP3 and P<sub>1dB</sub>. Figure 2.3 shows the definition of ACPR.

**Figure 2.3 Definition of ACPR**

When a modulated signal is applied to the power amplifier, the output of the power amplifier consists of the amplified signal channel and the adjacent channel signal A 1V CMOS Power Amplifier for Bluetooth Applications 11

resulted from intermodulation. Since the input used in testing the ACPR is a modulated signal, higher order distortions are also included. Therefore, it is more accurate to measure the linearity of a power amplifier using ACPR instead of a two-tone test.

## 2.3 Classification Of Power Amplifiers

Digital modulation offers superior performance, such as noise insensitiveness and integration of low cost CMOS process over analog modulation, and is widely used in wireless systems. To facilitate discussion on the tradeoff between power efficiency and spectral efficiency in digital modulation, literature classifies power amplifiers as either linear power amplifiers or nonlinear power amplifiers [2].

#### 2.3.1 Linear Power Amplifiers

When a linear power amplifier is used to amplify a signal, there is linear relationship between the input signal and the output signal. This is important for the non-constant envelope modulation scheme because the signal information, which is embedded in the envelope, will be lost if the power amplifier is not linear enough. Among all classes of power amplifiers, only class-A, class-AB and class-B can be viewed as a linear power amplifier.

A 1V CMOS Power Amplifier for Bluetooth Applications

#### 2.3.1.1 Class A

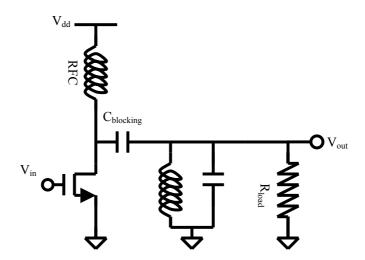

A class-A power amplifier is the simplest power amplifier. It can be viewed as a small-signal amplifier except the signal level is a substantial fraction of the bias level. A typical circuit topology is shown in Fig. 2.4.

Figure 2.4 Typical configuration of a class-A power amplifier

It consists of an RF choke, a DC blocking capacitor, a parallel LC tank and a transistor. An RF choke (RFC) is used to feed DC power to the drain and provide a constant current to the transistor. Also, the use of inductive load doubles the voltage swing at the drain of the transistor which lowers the supply voltage by a factor of two [3]. The DC blocking capacitor prevents current flow to the output loading in order to eliminate DC power consumption. Due to the non-linearity of the transistor, the parallel LC tank filters the out-of-band emission so that only a

single tone sine wave is observed across the output loading.

The NMOS transistor shown in Fig. 2.4 is operated in the saturation region or pinch-off region for the whole input cycle. The transistor is biased to  $V_{dd}$  so that it operates in the saturation region for the entire period. Since both the transconductance ( $g_m$ ) and the output resistance ( $R_{out}$ ) of the transistor remain the same throughout the entire input cycle, the gain,  $g_m R_{out}$ , is approximately the same throughout the period and the linearity is the best among the other classes of power amplifier. Figure 2.5 shows the waveforms of a class-A power amplifier.

Figure 2.5 Voltage and current waveforms of an ideal class-A power amplifier

However, due to the 100% duty cycle or 360° conduction angle, the transistor always draws current during the period and the voltage across the transistor is always larger than zero. In other words, the transistor dissipates power constantly throughout the cycle. High linearity is achieved with the price of poor efficiency in a class-A

power amplifier.

The efficiency can be derived with the fact that the transistor is biased at  $V_{dd}$  and the amplitude of the output voltage swing is as large as  $V_{dd}$ . Also, the DC supply current,  $I_{DC}$  is the same as the RF current,  $I_{rf}$ . Therefore, the DE of a class-A power amplifier is:

$$DE = \frac{P_{rf}}{P_{DC}} = \frac{\frac{1}{2}I_{rf}V_{dd}}{I_{DC}V_{dd}} = \frac{1}{2}$$

The inherent DE of a class-A power amplifier is limited to 50%. Any non-ideal effects, such as losses associated with the parasitics will further reduce the efficiency. Therefore, the class-A power amplifier is chosen only when the requirement of linearity is stringent.

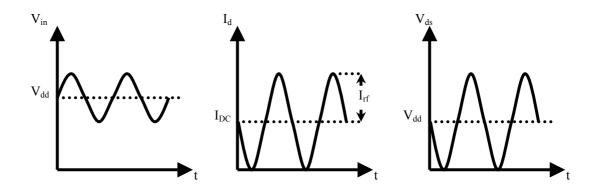

#### 2.3.1.2 Class B

It is noticed that the efficiency can be improved if the transistor does not conduct current for the entire cycle, but only draws current at a certain period of time. For example, if the transistor conducts half of the cycle, it is categorized as class-B power amplifier. Because the transistor has a 180° conduction angle, the transistor is biased at the threshold voltage and the transistor is in cut off region during half period of time, as shown in Fig. 2.6.

Figure 2.6 Voltage and current waveforms of an ideal class-B power amplifier

In practice, a class-B power amplifier is usually realized in push-pull configuration,

as shown in Fig. 2.7, to maximize efficiency.

Figure 2.7 Complementary class-B power amplifier

On the first half of the cycle, the current is 'pushed' to the output loading through the PMOS transistor. On the other half cycle, the current is 'pulled' from the load to NMOS transistor. However, due to the absent of high speed PMOS device, this

configuration is seldom used for RF applications.

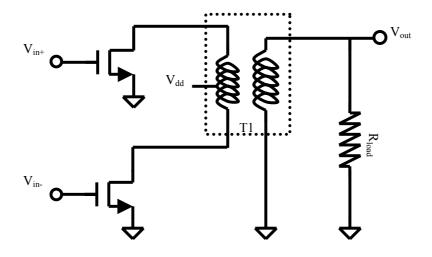

As shown in Fig. 2.8, a transformer-coupled class-B power amplifier utilizes two NMOS transistors.

Figure 2.8 A transformer coupled class-B power amplifier

Since two NMOS transistors are used, it is more suitable for high-speed applications. The transformer is used to combine the differential-ended drain current into a single-ended current.

With a 50% duty cycle, the DE can achieve 78% [3]. However, the linearity is inevitably degraded due to the switching between the cut-off region and the pinch-off region of the transistors. In practice, a class-B power amplifier is difficult to implement because the two transistors may have different threshold voltages and they may be ON or OFF at the same time.

#### 2.3.1.3 Class AB

When the transistors are ON at the same time for some instant, the amplifier is defined as a class-AB power amplifier. The corresponding waveforms are shown in Fig. 2.9.

Figure 2.9 Voltage and current waveforms of an ideal class-AB power amplifier

As its name implies, all parameters associated with a class-AB power amplifier lie between class-A and class-B. For example, the efficiency is between 50% and 78%. The performance of linearity is somewhere between class-A and class-B. Since the duty cycle of the transistors is ranged from 100% to 50%, the transistors are biased above the threshold voltage.

The circuit topologies of a class-AB power amplifier can be either a simple transistor configuration as class-A or a push-pull configuration as class-B. Class-AB power amplifiers are widely used in a system with a non-constant envelope modulation scheme [4] since it can provide better linearity with acceptable efficiency.

### 2.3.2 Non-Linear Power Amplifiers

When a system employs constant envelope modulation scheme, the linearity of a power amplifier is not critical. A non-linear power amplifier can be used so as to obtain higher efficiency. Class-C, class-E and class-F are examples of non-linear power amplifiers with high efficiency.

#### 2.3.2.1 Class C

The efficiency of a power amplifier is increased from 50% for a class-A power amplifier to 78% for a class-B power amplifier with the condition angle decreased from 360° to 180°. It is observed that efficiency greater than 78% can be achieved if the condition angle is further reduced to a level smaller than 180°. The resultant power amplifier is categorized as class-C. In fact, the circuit topologies can be the same for class-A, class-AB, class-B and class-C. The transistor in a class-A, class-AB, class-B and class-C. The transistor in a class-A, class-AB, class-B and class-C. The transistor is the biasing condition. With the reduction in condition angle, the efficiency is traded-off with the linearity from class-A to class-C. The price of achieving high efficiency is the poor linearity performance. Moreover, although the efficiency can approach 100%

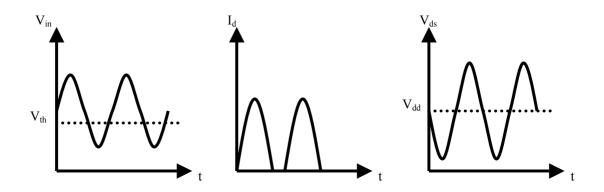

with conduction angle trends to zero, the output power will be zero since there is no drain current at all. Figure 2.10 shows the current and voltage waveforms of a class-C power amplifier.

Figure 2.10 Voltage and current waveforms of an ideal class-C power amplifier

From [5], the DE can be expressed in terms of  $\phi$  where  $2\phi$  is the conduction angle (in radian) for the class-C power amplifier:

$$DE = \frac{\phi - \sin\phi}{4\left[\sin\left(\frac{\phi}{2}\right) - \frac{\phi}{2}\cos\left(\frac{\phi}{2}\right)\right]}$$

(2.4)

Equation 2.4 can also be applied to class-A with  $2\phi = 2\pi$ , class B with  $2\phi = \pi$  and class-AB with  $\pi < 2\phi < 2\pi$ .

When the conduction angle is reduced, the input driving power has to be increased in order to maintain the device in the pinch-off regions which is essential to retain the output power level. Among all of the conventional power amplifiers, the input-driving requirement of a class-C power amplifier is the largest. Therefore, a class-C power amplifier is only suitable for a system with constant envelope modulation scheme and low output power. For a system with high output power and a constant envelope modulation scheme, switch mode power amplifier is used which have both high output power and superior efficiency.

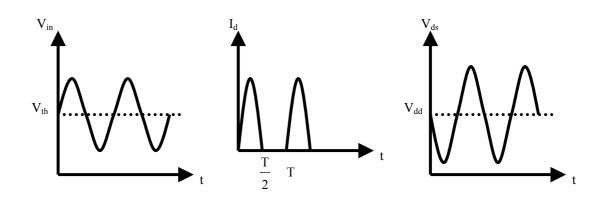

#### 2.3.2.2 Class E

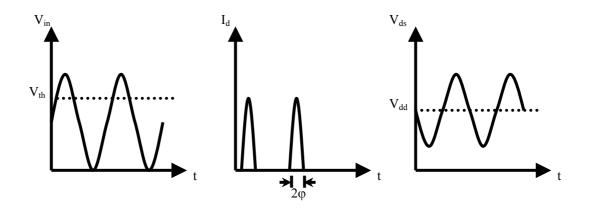

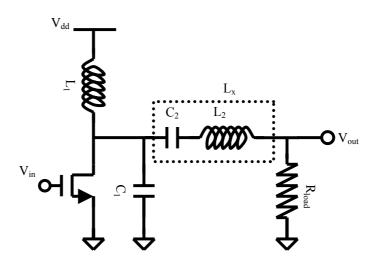

The class-E power amplifier was first invented by Sokal in 1975 [6]. Several criteria have to be fulfilled for a power amplifier to be categorized as class-E. First of all, voltage across the switch remains low when the switch turns off. When the switch turns on, voltage across the switch should be zero. Finally, the first derivative of the drain voltage with respect to time is zero,  $\frac{dV_{ds}}{dt} = 0$ , when the switch turns on. The first two conditions suggest that the power consumption by the switch is zero. The last condition,  $\frac{dV_{ds}}{dt} = 0$ , ensures that the voltage-current product is minimized even if the switch has a finite switch on time. Figure 2.11 shows a typical configuration of a class-E power amplifier. L<sub>1</sub> acts as either an RF choke or a finite DC-feed inductance [7]. C<sub>2</sub> and L<sub>2</sub> are designed to be a series LC resonator plus an excess inductance L<sub>x</sub> at the frequency of interest. C<sub>1</sub> and L<sub>x</sub> are designed so that the conditions for a class-E power amplifier operation are met.

Figure 2.11 A typical configuration of a class-E power amplifier

Figure 2.12 shows the waveforms of a class-E power amplifier.

Figure 2.12 Voltage and current waveforms of an ideal class-E power amplifier

It was observed that there is no overlapping between the voltage and the current waveforms. Class-E power amplifiers achieve 100% efficiency theoretically in the expense of poor linearity performance. However, the peak drain voltage is approximately  $3.6V_{dd}$  which increases the stress on the device especially for low

breakdown CMOS process.

#### 2.3.2.3 Class F

The idea of a class-F power amplifier is to exploit the harmonic contents so that the drain voltage and current waveforms are shaped to achieve higher efficiency. A sharper edge of the drain voltage will lower the loss of the switch. Therefore, a square wave is desired at the drain. A parallel LC tank tuned to the third harmonic is included to obtain the third harmonic component and add to the fundamental component to approximate a square wave at the drain of the transistor. The circuit configuration of a class-F power amplifier is shown in Fig. 2.13.

Figure 2.13 A simple configuration of a class-F power amplifier

$L_1$  and  $C_1$  are tuned to resonate at the fundamental frequency while  $L_2$  and  $C_2$  are tuned to present non-zero load impedance at the third harmonic frequency to make

up the second terms in the Fourier series expansion of a square wave. Figure 2.13 shows only the simplest class-F power amplifier with one LC tank tuned to the third harmonic. Additional LC tanks can be added to resonate at other odd harmonic frequencies to obtain a better square wave. The voltage and the current waveforms shown in Fig. 2.14 will be observed.

Figure 2.14 Voltage and current waveforms of an ideal class-F power amplifier

A class-F power amplifier can achieve 100% efficiency ideally. However, the disadvantage, in addition to the highly non-linear performance, is the complicated circuit topology for scaling of 3<sup>rd</sup> harmonic.

# 2.4 Summary

This chapter provides background for the designer to choose a suitable power amplifier. Efficiency and linearity are the major considerations when a class of power amplifier is to be selected. It is very important to understand the specifications of the power amplifier in advance because different applications will result in different choices of power amplifiers. A table of summary is shown of the performance of all the classes discussed.

|          | Ideal Efficiency | Linearity | Practical efficiency | Process            |

|----------|------------------|-----------|----------------------|--------------------|

| Class A  | 50%              | Good      | 35%                  | SOI 0.5µm CMOS [8] |

| Class AB | 50% - 78.5%      | Good      | 45%                  | 0.35µm CMOS [9]    |

| Class B  | 78.5%            | Moderate  | 49%                  | PHEMT [10]         |

| Class C  | 78.5% - 100%     | Poor      | 55%                  | 0.6µm CMOS [11]    |

| Class E  | 100%             | Poor      | 62%                  | 0.35µm CMOS [12]   |

| Class F  | 100%             | Poor      | 80%                  | PHEMT [10]         |

Table 2.1 Performance summaries of different classes of power amplifiers

## Reference

- [1] R. Razavi, "RF Microelectronics", 1998.

- [2] Steve C. Cripps, "RF Power Amplifiers for Wireless Communications", 1999.

- [3] Thomas. H. Lee, "*The Design of CMOS Radio-Frequency Integrated Circuits*", 1998.

- [4] J. T. Hwang, H. S. Lee, "1W 0.8µm BiCMOS adaptive Q-current controlled class-AB power amplifier for portable sound equipments," *IEEE International Solid-State Circuits Conference*, pp. 382-485, vol. 1, 2002.

- [5] H. L. Kraus, C. W. Bostian, and F. H. Raab, "Solid State Radio Engineering", 1980.

- [6] N. Sokal and A. Sokal, "Class E A New Class of High-Efficiency, Tuned Single-Ended Switching Power Amplifier". *IEEE J. Solid-State Circuits*, vol. Sc-10, no. 3, pp. 168-176, June 1975.

- [7] R. E. Zulinski and J. W. Steadman, "Class-E power amplifiers and frequency multipliers finite dc feed inductance". *IEEE Transitions on Circuits and Systems*, vol. CAS-34, no. 9, pp. 1074-1087, September 1987.

- [8] S. Lam, W. H. Ki, M. Chan, "Characteristics of RF power amplifiers by 0.5μm SOS CMOS process," IEEE International SOI Conference, pp. 141-142, 2001.

- [9] C. Fallesen, P. Asbeck, "A 1 W 0.35µm CMOS power amplifier for GSM-1800 with 45% PAE," *IEEE International Solid-State Circuits Conference*, pp. 158-159, 2001.

- [10] P. M. White, "Effect of input harmonic terminations on high efficiency class-B and class-F operation of PHEMT devices," IEEE MTT-S Digest, vol. 3, pp. 1611-1614, 1998.

- [11] R. Gupta, B. M. Ballweber, and D. J. Allstot, "Design and Optimization of CMOS RF Power Amplifiers". *IEEE J. Solid-State Circuits*, vol. 36, no. 2, pp 166-175, Feb. 2001.

- [12] K. Mertens, M. Steyaert, and B. Nauwelaers, "A 700-MHz 1-W Fully Differential CMOS Class-E Power Amplifier". *IEEE J. Solid-State Circuits*, vol. 37, pp. 137-141, February 2002.

- [13] T. C. Kuo, B. Lusignan, "A 1.5 W class-F RF power amplifier in 0.2µm CMOS technology," *IEEE International Solid-State Circuits Conference*, pp. 154-155, 2001.

A 1V CMOS Power Amplifier for Bluetooth Applications

# **CHAPTER 3**

## **DESIGN OF POWER AMPLIFIER**

### **3.1 Introduction**

Recall that the research goal is to design a CMOS power amplifier for Bluetooth applications. Therefore, the corresponding specifications should be studied before the design of the power amplifier.

As stated in chapter 1, the output power of the power amplifier is set to be 20dBm for class-1 Bluetooth application under 1V supply voltage. Since the modulation scheme employed by Bluetooth is GFSK, which is a constant envelope modulation scheme, a non-linear power amplifier can be used to achieve high efficiency. Among all classes of non-linear power amplifiers, the class-E power amplifier is the most attractive candidate in terms of circuit simplicity and high efficiency performance.

In this chapter, the circuit technique used for the power amplifier to work under low

supply voltage will be detailed in this chapter. Also, the design considerations of a class-E power amplifier will be discussed. Both the calculated and the simulated results will be presented. Finally, the characteristics of one of the crucial components, the inductors, will be investigated.

### 3.2 Design of Power Amplifier

#### **3.2.1 Differential Topology**

Differential configuration will be adopted because of its numerous advantages. First of all, the common-mode noise is minimized which reduces the disturbance of substrate coupling to other circuits. Since the current is discharged to the ground twice per cycle, interference to the desired signal is reduced.

A large output voltage swing is needed for a power amplifier so as to provide moderate output power. However, the breakdown voltage of the devices in CMOS process is too low to withstand a large voltage swing. With the process scaling, the situation is even worse. Fortunately, the most pronounced advantage of differential configuration, gain boosting, relaxes the stringent requirement on device breakdown voltage. The same circuit topology with differential configuration gives double output power compared with the single-ended configuration. Also, the size of the transistor can be smaller because the current flow through the transistor is reduced for the same supply voltage and the same output power.

### **3.2.2 Class-E Power Amplifier**

The circuit topology of a class-E power amplifier is reprinted in Fig. 3.1.

Figure 3.1 Configuration of a class E power amplifier

The component values can be calculated using the following equations [1]:

$$L_{x} = \frac{\pi V_{dd}^{2} \left(\pi^{2} - 4\right)}{2\omega P_{out} \left(\pi^{2} + 4\right)}$$

(3.1)

$$C_1 = \frac{P_{\text{out}}}{\pi\omega V_{\text{dd}}^2}$$

(3.2)

$$R_{load} = 0.577 \frac{V_{dd}^2}{P_{out}}$$

(3.3)

These equations can be derived by the fact that the switch is either turned on or off. Therefore, two state equations can be obtained. For a power amplifier to be categorized as class-E, several criteria, as stated in chapter two, have to be fulfilled. These criteria are the boundary conditions to be applied and the state equations can be solved.

It should be noted that the above equations are only valid for class-E power amplifiers and  $R_{load}$  is not necessary the same for all classes of power amplifier [2].  $R_{load}$  is usually called optimum load ( $R_{opt}$ ) and is defined as a loading presented to the power amplifier for a desired output power with the highest efficiency. The optimum load is designed according to the specification on output power and the supply voltage.

In the above analysis,  $L_1$  is assumed to be an RFC. The rule of thumbs for an inductor to be an RFC is that the reactance of  $L_1$  is larger than ten times the reactance of  $C_1$ :

$$X_{L_1} > 10 X_{C_1}$$

(3.4)

In fact,  $L_1$  acts as either a RF choke (RFC) or a finite DC-feed inductance. However, it is advantageous to choose  $L_1$  as a finite DC-feed inductor because the serial resistance of the inductor is reduced with a smaller inductance value which provides higher efficiency than an RFC with the same output power and the same supply voltage [3]. The operating frequency can be pushed higher with a finite DC-feed inductor since the parasitic capacitors associated with the transistors are resonated out by the inductor. In practice, the capacitor used to fulfill the class-E operation,  $C_1$ , can be implemented by the parasitic capacitance of the transistor. Therefore,  $L_1$  can be calculated by the resonant equation of a LC tank.

$$L_{1} = \frac{1}{\omega^{2}C} = \frac{1}{\omega^{2} \left(C_{p} - C_{1}\right)}$$

(3.5)

In the above equation, C is the total capacitance at the drain of the transistors,  $C_p$ , minus the required parasitic capacitor,  $C_1$ , in fulfilling the operating condition of a class-E power amplifier.

#### 3.2.3 Output Matching Network

The output power will be low if the power amplifier is directly connected to the antenna, which has a 50 $\Omega$  loading. For example, if  $R_{opt} = 50\Omega$  and  $V_{dd}$  is 1V, then

$$P_{out} = 0.577 \frac{V_{dd}^2}{R_{opt}} = 11.54 \text{mW}$$

As a result, the optimum load is typically about several ohms and can be obtained with the supply voltage ( $V_{dd}$ ) and the output power ( $P_{out}$ ) fixed according to the specification of a wireless standard.

In order to match the 50 $\Omega$  loading, an up-conversion matching network is implemented to transform the optimum load to a 50 $\Omega$  load. L-matching network is chosen because of its circuit simplicity. Also, the excess inductance (L<sub>x</sub>) in a class-E power amplifier can be combined with the inductor used in the matching network if a low-pass L matching network is used. Therefore, the schematic of a class-E power amplifier is modified as Fig. 3.2.

Figure 3.2 Complete schematic of a class E power amplifier

The values of  $L_m$  and  $C_m$  can be calculated using the following equations [4]:

$$L_{\rm m} = \frac{\sqrt{R_{\rm opt} \left(R_{\rm L} - R_{\rm opt}\right)}}{\omega}$$

(3.6)

$$C_{\rm m} = \frac{\frac{\sqrt{\left(R_{\rm L} - R_{\rm opt}\right) / R_{\rm opt}}}{R_{\rm L}}}{\omega}$$

(3.7)

#### 3.2.4 Design Of Output Stage

Since the power amplifier is designed for class-1 Bluetooth application, the output power is 20dBm, 100mW. The use of differential topology is to relax the output power from 100mW to 50mW. The target output power is designed to be 60mW to provide margin for some losses due to parasitics and the supply voltage of the power amplifier is set to 1V. Therefore, the optimum load can be calculated using equation 3.1.

$$R_{opt} = \frac{V_{dd}^2}{P_{out}} \left(\frac{8}{\pi^2 + 4}\right) = \frac{1}{60m} (0.577) = 9.6\Omega$$

Also, the values of parameters,  $L_x$  and  $C_1$  can be calculated using equation 3.2 and 3.3 to meet the requirements of a class-E power amplifier.

$$L_{\rm X} = \frac{\pi V_{\rm dd}^2 (\pi^2 - 4)}{2\omega P_{\rm out} (\pi^2 + 4)} = 0.735 \text{nH}$$

$$C_1 = \frac{P_{\rm out}}{\pi \omega V_{\rm dd}^2} = 1.27 \text{pF}$$

With  $R_{opt} = 9.6\Omega$ , the parameters of a L-matching network can be calculated using

equation 3.6 and 3.7.

$$L_{m} = \frac{\sqrt{R_{opt} (50 - R_{opt})}}{\omega} = 1.31 \text{nH}$$

$$C_{m} = \frac{\sqrt{(50 - R_{opt})/R_{opt}}}{\frac{50}{\omega}} = 2.72 \text{pF}$$

The parasitic capacitance associated with the transistor should be known before the calculation of  $L_1$ . As a result, the size of the transistor should be designed first in order to find out the value of  $L_1$ . However, the empirical equation to calculate the transistor sizing is absent due to the *apriori* designability of the class E power amplifier, the size of the transistor can only be estimated by the their maximum allowable current flow.

Because the output power is set to 60mW and the supply voltage is 1V, the average current flow through the transistor is about 60mA. Since the switch will conduct current for only half of the period, the peak current should be at least 120mA. With  $V_{gs} = V_{ds} = 1V$ ,  $V_{th} = 0.6V$  and  $\mu C_{ox} = 140\mu A/V^2$ , the size of the transistor can be calculated by the current equation:

$$I_{d} = \frac{\mu C_{ox}}{2} \frac{W}{L} \left( V_{gs} - V_{t} \right)^{2}$$

(3.8)

Because TSMC 0.35- $\mu$ m CMOS will be used, the W/L of the transistor is found to be approximately equal to 4500 $\mu$ /0.4 $\mu$ , which gives 4.2pF parasitic capacitors. Therefore, L<sub>1</sub> can be calculated by equation 3.5:

$$L_1 = \frac{1}{\omega^2 C} = \frac{1}{\omega^2 (C_p - C_1)} = 1.6 \text{nH}$$

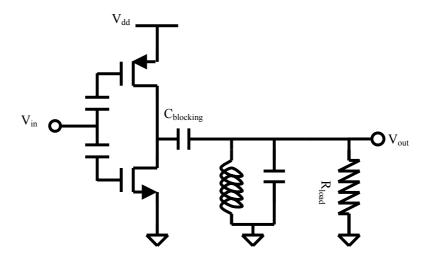

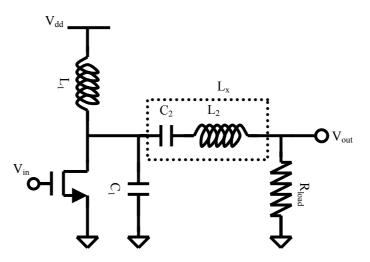

#### 3.2.5 Common-Gate Class E Power Amplifier

In the above analysis, all the components are assumed to be ideal. However, it is not the case in practice. For example, the passive components, inductor and capacitor, consist of parasitic serial resistances. Also, the switch has finite on-resistance and finite transition times. As a result, the efficiency of a class-E power amplifier is much degraded from theoretical 100% to the highest achievable PAE of 63% in CMOS process [5]. Those non-ideal effects push RF circuit designers to develop new circuit techniques to support low voltage design.

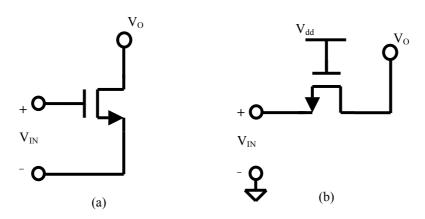

In a class-E power amplifier, the transistor acts as a switch instead of a current source. The switch can be implemented by either common-source or common-gate configuration. Usually, the switch is implemented using a common-source configuration. For a common-source switch, the input signal is applied at the gate of the transistor. The voltage across the transistor,  $V_{ds}$  is fixed by the supply voltage.

Figure 3.3 A switch using (a) common-source (b) common-gate configuration

When the supply voltage is scaled down, the voltage dropped across the on-resistance of the transistor is compatible to the supply voltage. The effective supply voltage will decrease the power capability and hence degrade the efficiency.

$$V_{\text{effective}} = V_{\text{dd}} - V_{\text{R}_{\text{on}}}$$

(3.9)

The situation is even worse if an RFC is used instead of a finite DC feed inductor. Therefore, a finite DC feed inductor is preferred because the voltage drop across the inductor is minimized and the effect on the effective supply voltage is neglected.

[6] proposed a common-gate class-E power amplifier to relax the device stress. The corresponding schematic is shown in Fig. 3.4. The common-gate class-E power amplifier is connected in cascode with a large transistor to avoid the loading effect to the input stage. However, the cascode transistor unfortunately reduces the voltage

headroom across the switch.

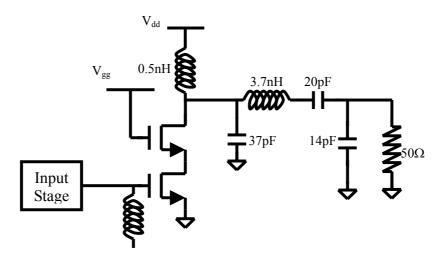

Figure 3.4 Schematic of the published common-gate class-E power amplifier

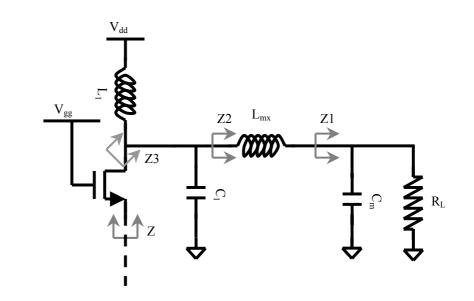

To overcome the voltage drop across the switch, a common-gate switch without connecting in cascode is proposed and the schematic of the proposed common-gate class-E power amplifier is shown in Fig. 3.5.

Figure 3.5 Schematic of the proposed common-gate class-E power amplifier

For a common-gate switch, the input signal is directly applied to the source. By proper biasing, the effective supply voltage can be increased from  $V_{dd} - V_{Ron}$  (in the common-source case) to  $V_{dd} - V_{Ron} + V_{signal}$  where  $V_{signal}$  is the amplitude of the input signal. Figure 3.6 shows the corresponding current and voltage waveforms of the proposed common-gate class E power amplifier.

Figure 3.6 Voltage and current waveforms of a common-gate class E power amplifier

The idea utilizes the fact that the voltage at the source is in phase with the voltage at the drain. If the source is biased at ground and the gate is tied to  $V_{dd}$ , the switch is turned on when the voltage of the source is negative. Since the input signal is applied to the source, the amplitude of the signal increases the voltage across the switch. As a result, the supply voltage is raised effectively. The effect of  $V_{Ron}$  can be compensated by the amplitude of the applied signal in the common-gate

configuration, and the supply voltage can be lower with compatible efficiency. The problem of low impedance of the input of the common-gate switch without cascode can be solved with the inclusion of a driver stage with positive feedback before the class-E amplifier.

#### **3.2.6 Drive Stage Using Positive Feedback**

The pre-amplifier of the power amplifier is a very important element since the efficiency and the output power can be very low if the driving signal to the output stage is not optimum. Under low supply voltage, the pre-amplifier is very hard to design mainly because the size of the output stage transistors needs to be in millimeter range, which introduces a large capacitive loading.

Because differential configuration is employed, the problem can be solved by utilizing a cross-coupled pair to form a positive feedback as the pre-amplifier. Several publications demonstrated the use of the positive feedback in power amplifiers [5][7]. Also, a pre-amplifier with positive feedback provides a large swing to the input of the output stage which maintains high efficiency.

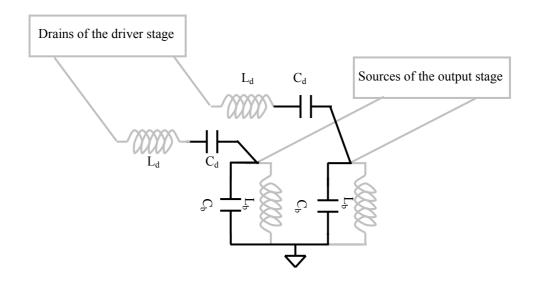

#### 3.2.7 Proposed Architecture

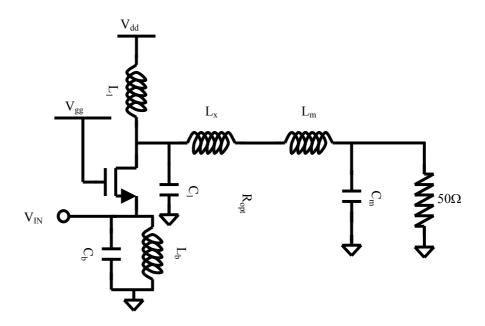

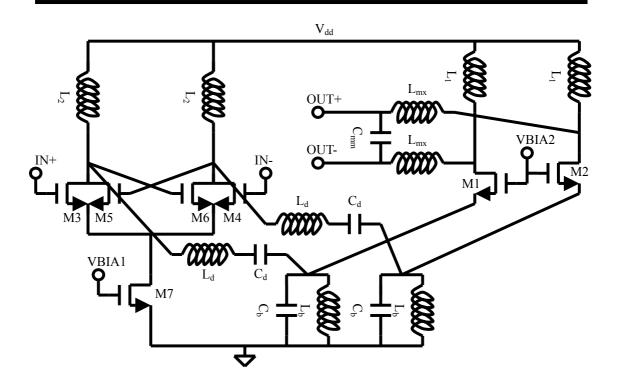

The overall schematic of the proposed power amplifier is shown in Fig. 3.7.

Figure 3.7 Schematic of the proposed power amplifier

The design of the proposed power amplifier starts by specifying the required power gain and the output power. First of all, the output power is assumed to be 120mW, 20.8dBm. The power gain of the output stage is set to 7dB. Therefore, the required input power for the output stage is 13.8dBm. In other words, the output power of the driver stage should be at least 13.8dBm. The input power to a power amplifier utilizing positive feedback input stage is around 3dBm [5][7]. As a result, the power gain of the driver stage is equal to 10.8dBm. It is always the case that the power gain of the input stage is higher than the output stage because the input stage is focused on high power gain while the output stage is targeted to achieve high efficiency.

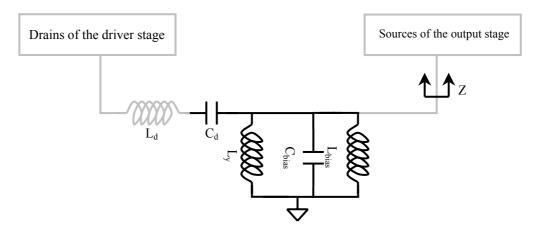

Since the DC biasing points for the drain of the driver stage and the source of the output stage are different, an interstage-matching network with a DC blocking capacitor,  $C_d$ , is implemented to connect the driver stage and the output stage.

Another function of the interstage-matching network is to present an optimum load to the driver stage while transfer the maximum power to the input of the output stage. Since the driver stage using positive feedback works as a class-E power amplifier, the values of the components of the driver stage can be calculated using the same agreement as the output stage.

$$R_{opt}(preamp) = \frac{V_{dd}^2}{P_0(preamp)} \left(\frac{8}{\pi^2 + 4}\right) = \frac{1}{12m} (0.577) = 48\Omega$$

$$L_{X}(\text{preamp}) = \frac{\pi V_{dd}^{2} (\pi^{2} - 4)}{2\omega P_{o}(\text{preamp}) (\pi^{2} + 4)} = 2nH$$

$$C_1(\text{preamp}) = \frac{P_o(\text{preamp})}{\pi \omega V_{dd}^2} = 0.253 \text{pF}$$

$$L_2 = \frac{1}{\omega^2 C} = \frac{1}{\omega^2 (C_p - C_2)} = 2.4 \text{nH}$$

The impedance looking from the source of the output stage to the 50 $\Omega$  load is calculated as shown below:

$$Z = \frac{1}{g_{m1}} + \frac{\omega^{2}L_{1}L_{mx} + j\omega L_{1}R_{L}\left(\omega^{2}L_{mx}C_{m} - 1\right)}{R_{L}\left\{\omega^{2}\left[L_{1}\left(C_{m} + C_{p}\right) + L_{mx}C_{m}\left(1 - \omega^{2}L_{1}C_{p}\right)\right] - 1\right\} + j\omega\left[L_{mx}\left(\omega^{2}C_{p}L_{1} - 1\right) - L_{1}\right]}$$

Since all the parameters have been designed, the impedance Z is found to be:

The biasing LC tank  $L_b$  and  $C_b$  is to bias the source of the output stage to ground and can be separated into two parts: a LC tank resonates at the frequency of interest and a matching network,  $L_y$  and  $C_d$ , for matching the impedance Z and Ropt(*preamp*). Figure 3.8 shows the equivalent schematic of the interstage-matching network.

Figure 3.8 Equivalent schematic of the interstage-matching network

Since the capacitor  $C_{bias}$  will be implemented by the parastics capacitance of  $C_d$  which will be detailed in Chapter 5,  $C_{bias}$  is chosen to be one fifth of  $C_d$  and the inductor  $L_{bias}$  can be calculated using the resonant equation:

$$L_{bias} = \frac{1}{\omega^2 C_{bias}}$$

Table 3.1 summarizes the values of the passive components used in the power amplifier.

Table 3.1 Summary of the values of the passive components

| L <sub>1</sub> | L <sub>2</sub> | L <sub>m</sub> | C <sub>m</sub> | L <sub>b</sub> | C <sub>b</sub> | L <sub>d</sub> | C <sub>d</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1.6nH          | 2.4nH          | 2nH            | 1.36pF         | 1.9nH          | 0.55pF         | 2nH            | 4.2pF          |

Table 3.2 summarized the sizing of the transistors used in the proposed power amplifier. The corresponding parasitic drain capacitances,  $C_p$ , are also shown and the capacitances are used to calculate the finite DC feed inductors,  $L_1$  and  $L_2$ .

Table 3.2 Summary of the transistors sizing

|                | M1     | M2     | M3     | M4     | M5     | M6     | M7      |

|----------------|--------|--------|--------|--------|--------|--------|---------|

| W              | 4500µm | 4500µm | 600µm  | 600µm  | 1200µm | 1200µm | 12000µm |

| L              | 0.4µm   |

| C <sub>p</sub> | 4.2pF  | 4.2pF  | 0.78pF | 0.78pF | 1.35pF | 1.35pF | 17pF    |

#### **3.2.7 Pre-simulation Results**

The proposed power amplifier is simulated using Hspice. Level 49 BSIM3 model for TSMC 0.35- $\mu$ m double-polysilicon 4-metal layer process is used throughout the

simulation. The performance of the proposed power amplifier is summarized in Table 3.3.

|            | Frequency | Supply Voltage | Input Power | Output Power | Power Gain | DE    | PAE   |

|------------|-----------|----------------|-------------|--------------|------------|-------|-------|

| Calculated | 2.4GHz    | 1V             | -           | 120mW        | 17.8dB     | 100%  | -     |

| Simulated  | 2.4GHz    | 1V             | 3dBm        | 116.7mW      | 17.6dB     | 65.1% | 63.8% |

Table 3.3 Performance of the proposed power amplifier

The DE is only 65.1% because the transistors have a finite transition time which introduced overlapping of the voltage and the current waveforms. In addition to the power dissipation due to the finite transition time, the on-resistor of the switch degrades the efficiency.

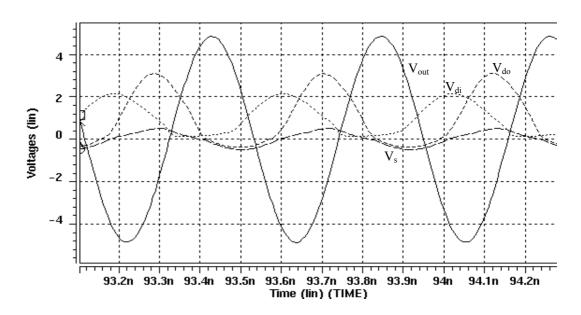

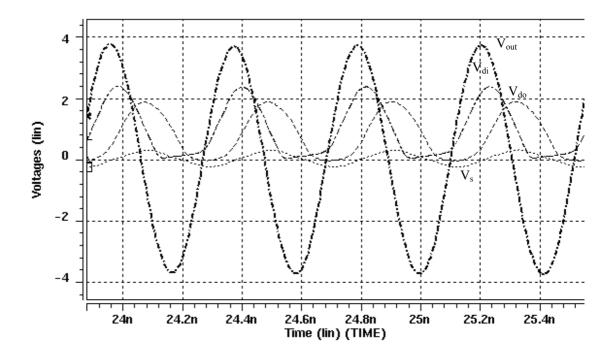

Figure 3.9 shows the waveforms of the drain of the driver stage ( $V_{di}$ ), the drain of the output stage ( $V_{do}$ ) and the source of the output stage ( $V_s$ ).

It can be seen that the voltage at the source of the output stage swings to a negative value which increases the effective supply voltage.

#### 3.2.8 Inductor Realization

In the pre-simulation, all the passive components are ideal. The parasitic serial resistance of both the capacitor and the inductor are assumed to be zero. In practice, the efficiency depends highly on the quality of the passive components especially the inductors. The quality of an inductor can be justified by quality factor (Q):

$$Q = \frac{\omega L}{R}$$

(3.10)

To investigate the effect on the inductor Q, PAE of the proposed power amplifier is plotted against Q in Fig. 3.10.

Figure 3.10 PAE versus inductor Q

It is observed that the PAE drops rapidly when the Q is below 20. Therefore, the

inductor Q should be kept at a level higher than 20 for acceptable PAE.

CMOS monolithic inductors are well known for its low quality factor (Q) due to high substrate loss and high parasitics. Monolithic inductors are widely used in RF applications even when the Q of monolithic inductors ranges from 3 to 6 in the CMOS process. Many building blocks, such as LNA and VCO, use monolithic inductors with Q-compensation circuitry [8]. These methods of Q compensation of on-chip inductors, however, are not feasible in power amplifiers because the power consumed in compensating the inductor losses would significantly lower the efficiency. Therefore, bondwire inductors are used to implement high-Q inductors to obtain a higher PAE.

### Reference

- [1] N. Sokal and A. Sokal, "Class E A New Class of High-Efficiency, Tuned Single-Ended Switching Power Amplifier". *IEEE J. Solid-State Circuits*, vol. Sc-10, no. 3, pp. 168-176, June 1975.

- [2] R. Gupta, B. M. Ballweber, and D. J. Allstot, "Design and Optimization of CMOS RF Power Amplifiers". *IEEE J. Solid-State Circuits*, vol. 36, no. 2, pp 166-175, Feb. 2001.

- [3] R. E. Zulinski and J. W. Steadman, "Class-E power amplifiers and frequency multipliers with finite dc feed inductance". *IEEE Transitions on Circuits and Systems*, vol. CAS-34, no. 9, pp. 1074-1087, September 1987.

- [4] D. M. Pozar, "Microwave Engineering", 1993.

- [5] K. Mertens, M. Steyaert, and B. Nauwelaers, "A 700-MHz 1-W Fully Differential CMOS Class-E Power Amplifier". *IEEE J. Solid-State Circuits*, vol. 37, pp. 137-141, February 2002.

- [6] C. Yoo and Q. Huang, "A common-gate switch 0.9-W class-E power amplifier with 41% PAE in 0.25µm CMOS". *IEEE J. Solid-State Circuits*, vol. 36, No. 5, pp. 823-830, May 2001.

- [7] K. C. Tsai and P. R. Gray, "1.9-GHz 1-W CMOS RF power amplifier for wireless communication". *IEEE J. Solid-State Circuits*, vol. 34, pp. 962-970, July 1999.

- [8] Y. W. Chung and Y. H. Shuo, "The Design of a 3-V 900-MHz CMOS Bandpass Amplifier". *IEEE J. of Solid-State Circuits*, vol. 32, No. 2, Feb. 1997.

# **CHAPTER 4**

# **BONDWIRE MODELING**

## **4.1 Introduction**

In chapter 3, the design of the proposed power amplifier and the pre-simulation results were presented. However, it is possible that measurement results cannot match the simulation results if the modeling of the components used is not accurately done. Although the model of the transistors (the level 49 BSIM3 model) is accurate enough, the model of another essential component, inductor, is still inaccurate in RF applications.

In the design of the power amplifier, all the inductors are realized using bondwire. Because of the high quality factor offered by bondwire which reduces resistive power losses, a higher PAE can be obtained. Although bondwire inductors provide a high quality factor, predetermination of bondwire inductance is difficult. Since the inductance is sensitive to bonding geometry, bondwires need to be modeled accurately before they can be used as inductors in a power amplifier.

In this chapter, the model used for bondwire inductor will be introduced and the quantitative analysis of the inductance will be presented. The analytical solution will provide a rough estimation of the relationship between the inductance and the physical length of the bondwire which facilitates both the circuit layout and the PCB layout. Finally, the simulation of the bondwire inductance and the quality factor will be done using HP's ADS.

## 4.2 Inductor Model

In order to have an accurate model, all the elements used in the inductor model have to be well defined according to the electromagnetic theory and the physical structure. Figure 4.1 shows a lumped element model for the bondwire inductor.

Figure 4.1 Lumped-element model for a bondwire inductor

$L_s$  is the inductance of the bondwire,  $R_s$  models the serial resistor,  $C_p$  accounts for the overlap capacitance between the inductor and the ground plate and  $R_p$  models the substrate loss. This model will be used to do the empirical fit of the measurement results in chapter 6.

### 4.3 Analytical Solution Of Bondwire Inductance

The inductance of a wire can be calculated by equation 4.1 [1]:

$$L = \frac{\mu_0 l}{2\pi} \left\{ ln \left[ \left( \left( \frac{2l}{d} \right) + \left( 1 + \frac{2l}{d} \right)^2 \right)^{\frac{1}{2}} \right] + \frac{d}{2l} - \left( 1 + \left( \frac{d}{2l} \right)^2 \right)^{\frac{1}{2}} + \mu_r \delta \right\}$$

(4.1)

$$\delta = 0.25 \tanh\left(\frac{4d_{\rm s}}{d}\right) \tag{4.2}$$

$$d_{\rm S} = \sqrt{\frac{\rho}{\pi f \mu_0 \mu_{\rm r}}} \tag{4.3}$$

where l is the length of the wire, d is the diameter of the wire,  $\rho$  is the resistivity of the material of the wire, d<sub>s</sub> is the skin depth and  $\mu_0$ ,  $\mu_r$  are the absolute permeability and the relative permeability of the wire respectively.

The inductance of the wire will be decreased if the wire close to the ground plate. The negative mutual inductance caused by the ground plate is give by [1]:

$$M(2h) = \frac{\mu_0 l}{2\pi} \left\{ ln \left[ \left( \left( \frac{1}{2h} \right) + \left( 1 + \left( \frac{1}{2h} \right)^2 \right) \right]^{\frac{1}{2}} \right] + \frac{2h}{l} - \left( 1 + \left( \frac{2h}{l} \right)^2 \right)^{\frac{1}{2}} \right] \right\}$$

(4.4)

where h is the distance between the ground plate and the inductor. As a result, the total inductance of the wire is reduced to  $L_{total} = L - M(2h)$ .

Since aluminum bondwire with 1.25-mil diameter will be used,  $\rho = 1.75 \times 10^{-8} \Omega m$ ,  $\mu_r = 1.00002$ ,  $\mu_0 = 4\pi \times 10^{-7} Hm^{-1}$  and  $d = 31.75 \mu m$ . Also, 2h = 2mm because the bondwire is typically 1mm above the ground plate. The theoretical total inductance of the wire is plotted against the length of the wire in Fig. 4.2.

Figure 4.2 Theoretical total inductance ( $L_{total}$ ) against the length of the wire

Several inductance values will be used in the proposed power amplifier. For example, the RFC of the input stage and the output stage are 2.3nH and 1.6nH respectively. Also, 2nH inductors are used in the output of the power amplifier and the interstage matching. Their corresponding lengths can be found in Fig. 4.2.

The resistance of the bondwire can be estimated using the following equation

$$R_{\rm s} = \rho \frac{1}{A} \tag{4.5}$$

where l is the length of the wire, A is the effective area of the wire,  $\rho$  is the resistivity of the material of the wire. Because of the skin effect [2], the effective area of the wire is reduced from  $\pi \left(\frac{d}{2}\right)^2$  to  $\pi \left[\left(\frac{d}{2}\right)^2 - \left(\frac{d-2d_s}{2}\right)^2\right]$ .

For example, the serial resistance, R<sub>s</sub>, of inductance with 2nH can be calculated by equation 4.5 with l = 2.65mm,  $\rho = 1.75 \times 10^{-8} \Omega m$  and  $d = 31.75 \mu m$ :

$$R_{s}(2nH) = \rho \frac{1}{A} = 1.75 \times 10^{-8} \frac{2.65 \times 10^{-3}}{\pi \left[ \left( \frac{31.75\mu}{2} \right)^{2} - \left( \frac{31.75\mu - 2.718\mu}{2} \right)^{2} \right]} = 0.357\Omega$$

Therefore, the quality factor of the bondwire inductor with 2nH inductance is:

$$Q = \frac{\omega L}{R_s} = 84.5$$

## 4.4 Simulation Results of Bondwire Inductance

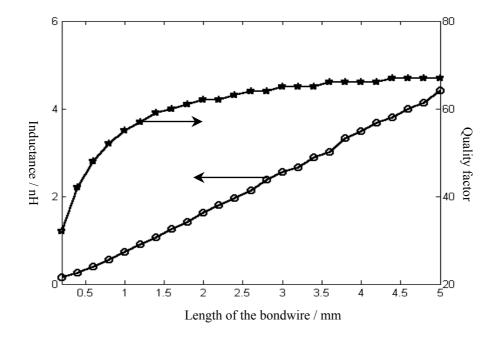

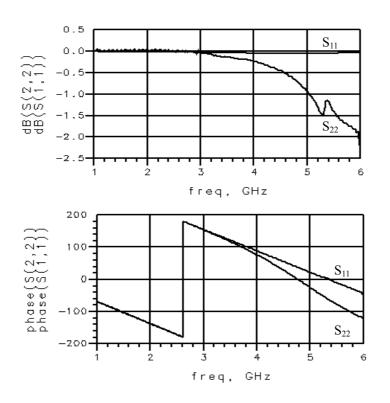

The analytical equations, however, do not accurately provide information on the quality factor of an inductor. Fortunately, commercial software, HP's ADS, contains a function to simulate the bondwire inductance and the quality factor as long as the physical parameters are provided. For example, the length of the bondwire, the height of the bondwire to the ground plate and conductivity of the material used. Since aluminum bondwire with 1.25-mil diameter will be used, the same parameters,  $\rho = 1.75 \times 10^{-8} \Omega m$ ,  $\mu_r = 1.00002$ ,  $\mu_0 = 4\pi \times 10^{-7} Hm^{-1}$ , 2h = 2mm and  $d = 31.75 \mu m$ , are inputted. The relationships of the length with both the inductance and the quality factor are shown in Fig. 4.3 with the frequency fixed to 2.4GHz.

Figure 4.3 Simulated Inductance (asterisk marked) and quality factor (circle marked) against the length of the bondwire

The inductance and the quality factor are found by the Y-parameters [3]. It is observed that the quality factor increases with the length of the bondwire. This is because when the bondwire is longer, the eddy current induced by the ground plate will decrease, which results in smaller losses. The quality factor remains constant when the effect of the ground plate is neglected. From the simulation, the quality factor is at least 30 and can be used in the power amplifier without severely degrading the PAE.

## Reference

- [1] A. M. Niknejad, R. G. Meyer, "Design, Simulation and Applications of Inductors and Transformers for Si RFICS", 2000.

- [2] Pieter L. D. Abrie, "The Design of Impedance-matching Networks for Radio-Frequency and Microwave Amplifiers", 1985.

- [3] R. L. Bunch, D. I. Sanderson, S. Raman, "Quality Factor and Inductance in Differential IC Implementations," *IEEE Microwave Magazine*, pp. 82-92, June 2002.

A 1V CMOS Power Amplifier for Bluetooth Applications

# **CHAPTER 5**

# LAYOUT CONSIDERATIONS

## **5.1 Introduction**

Due to the enormous current flow in a power amplifier compared to other building blocks, a 100 mV reduction in the output voltage swings will result when there is only  $0.2\Omega$  parasitic resistor. Therefore, the layouts of the power amplifier have to be carefully designed so that the performance of the circuit will not be degraded.

In this chapter, some layouts of the components will be detailed. For example, the layouts of the capacitor and the interconnection wire will be discussed. Because bondwire will be used as the inductors, the floorplan and the layout of the overall circuit as well as the PCB will be presented. Finally, the post-simulation results will be given.

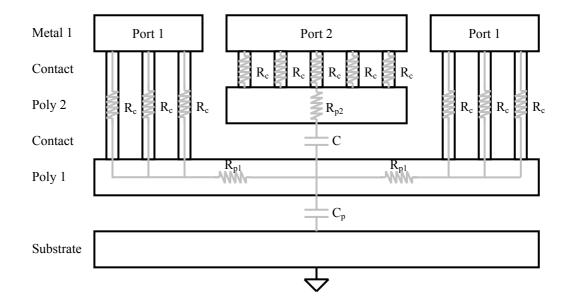

### **5.2 Capacitors Layout**

There are numerous approaches used when drawing the layout of capacitors, capacitors, polysilicon-polysilicon capacitors and substrate-well metal-metal layout capacitors. techniques, Among all the the capacitor using polysilicon-polysilicon provides the highest capacitance density. However, some of the process does not offer double polysilicon layers for capacitors realization. Fortunately, the TSMC 0.35-µm process offers double polysilicon layers, so the layout of the capacitors will be drawn using double polysilicon layers.

Two important issues have to be considered for the layout of the capacitors.

First of all, the serial resistance of the capacitors layout should be minimized especially when the capacitor is in the signal path of the circuit. The resistivity of polysilicon is larger compared with the resistivity of metal. The large resistivity of polysilicon contributes the most to the serial resistance of the capacitor. Therefore, the dimension of the polysilicon should be small enough to minimize the serial resistance and large capacitance can be realized using fingers. Also, the interconnection should use metal as the media instead of polysilicon.

Contacts are used to connect the polysilicon to the metal. Since a contact contributes  $6.9\Omega$  resistance, many contacts have to be present to minimize the serial

resistance. As a result, the layout of a polysilicon-polysilicon capacitor should be similar to the one shown in Fig. 5.1.

Figure 5.1 Polysilicon-polysilicon capacitor with parasitics

Secondly, the parasitic capacitance introduced by the capacitor itself should be taken into account. A parasitic capacitor  $(C_p)$  is formed between the lower polysilicon layer and the substrate. This parasitic capacitor is accompanied with the wanted polysilicon-polysilicon capacitor (C) where C is about 5 times  $C_p$ . Therefore, the ports should be assigned carefully depending on the circuit. For example, port 2 should be assigned to a node which is more sensitive to the parasitics while the parasitic should have negligible effect for the node connected to port 1.

Figure 5.2 extracts the part of the schematic of the proposed power amplifier containing the capacitors.

A 1V CMOS Power Amplifier for Bluetooth Applications

Figure 5.2 Capacitors inside the proposed power amplifier

It is observed that the capacitor  $C_d$  can be implemented by the polysilicon-polysilicon capacitor while the parasitic capacitor as discussed is utilized as the capacitor  $C_b$ . Therefore, the area of the capacitors layout can be reduced and the parasitic effect can be eliminated.

## 5.3 Wire Layout

Due to the finite current density of the metal layers, even the simplest component, the interconnecting wire, has to be designed carefully so that the width is large enough to allow a large current to flow without burning the wire.

By rule of thumb, a metal slab with thickness of 1-µm is capable of handling 1mA of current. Since there are approximately 40mA of current flow in the driver stage and 100mA of current drawn from the output stage, the corresponding widths of the

metal are  $40\mu$ m and  $100\mu$ m. Although metal 4, which is about 1.4 times thicker than other metal layers, reduces the width to  $29\mu$ m and  $72\mu$ m, respectively, these wide metals introduce an undesirably large parasitic capacitor with the substrate. Therefore, two or three metal layers are connected in parallel so as to minimize the parasitic capacitor. In order to eliminate the capacitor formed between the metals, a large number of via are added to reduce the potential difference.

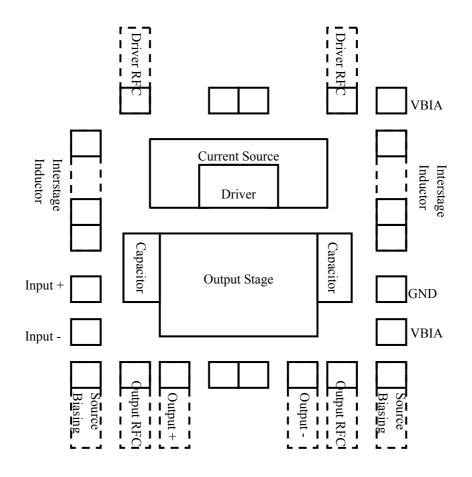

## 5.4 Floorplan

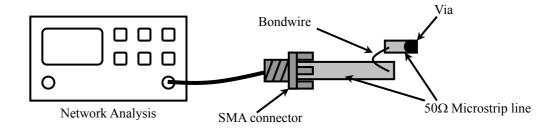

Figure 5.3 shows the block diagram of the overall layout.

Figure 5.3 Floorplan of the overall circuit

Since all the inductors are realized by bondwires, the layouts of the pads as well as the circuits are placed to facilities bonding of the bondwires.

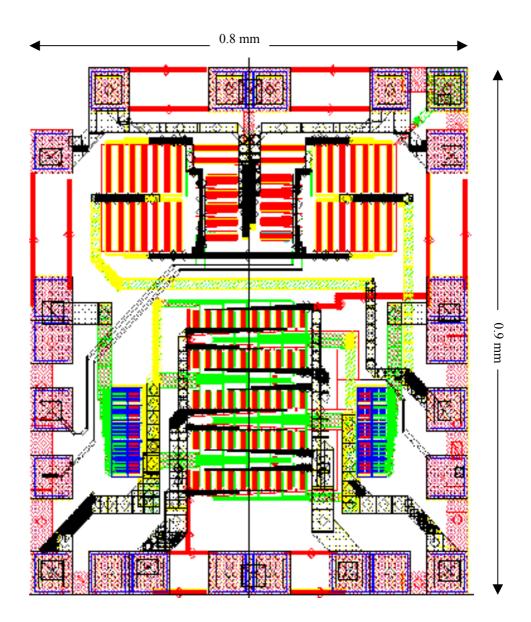

Figure 5.4 shows the final layout of the proposed power amplifier. The area of the chip is  $0.9 \times 0.8 \text{ mm}^2$ .

Figure 5.4 Circuit layout of the proposed power amplifier

## **5.5 Post-Layout Simulation Results**

Due to the parasitics introduced by the circuit layout, some of the values of the inductors are reduced to optimize the performance of the overall circuit. The modified inductances are shown in Table 5.1.

Table 5.1 Modified parameters for post-layout simulation